鄭艷芳1,唐海娣2,李雪寶1

(1.江蘇科技大學(xué),江蘇 張家港 215600;2.江蘇耐維思通科技股份有限公司,江蘇 張家港 215600)

摘要:基于靈活自適應(yīng)的空口波形技術(shù)FOFDM(Filtered OFDM)是現(xiàn)代通信技術(shù)的研究熱點,設(shè)計并實現(xiàn)可調(diào)FIR濾波器是實現(xiàn)該技術(shù)的核心工作之一。本文設(shè)計的基于FPGA的可調(diào)節(jié)FIR濾波器系數(shù)的自適應(yīng)調(diào)整是通過控制算法對信道中的信號進(jìn)行快速檢測,然后將結(jié)果和濾波器的輸出結(jié)果進(jìn)行差值計算進(jìn)行反饋調(diào)節(jié)。利用Quartus II和DSP Builder設(shè)計基于FPGA的16階系數(shù)可調(diào)FIR濾波器,給出核心模塊的設(shè)計電路圖和仿真結(jié)果。仿真結(jié)果表明:基于靈活自適應(yīng)空口波形技術(shù)可以在FPGA上實現(xiàn),而且由于FPGA具有天然的并行性,實際的通信系統(tǒng)中可以采用并發(fā)模式進(jìn)行,達(dá)到提高信號傳送速率的目的。

關(guān)鍵詞:可調(diào)FIR濾波器;FPGA;F-OFDM

中圖分類號:TN713+.7文獻(xiàn)標(biāo)識碼:ADOI: 10.19358/j.issn.1674-7720.2017.04.009

引用格式:鄭艷芳,唐海娣,李雪寶.基于FPGA的可調(diào)節(jié)FIR濾波器的設(shè)計與實現(xiàn)[J].微型機(jī)與應(yīng)用,2017,36(4):29-31,35.

0引言

4G移動通信方興未艾,業(yè)界對于5G移動通信技術(shù)的討論已經(jīng)如火如荼。作為移動通信領(lǐng)域“皇冠”上的一顆明珠,基于靈活自適應(yīng)的空口波形技術(shù)和成倍提升頻譜效率的多址技術(shù)SCMA(Sparse Code Multiple Access)成為業(yè)內(nèi)人士關(guān)注的焦點,其中,優(yōu)化頻帶資源的利用率是FOFDM的核心。人們在研究算法優(yōu)化的同時,也在關(guān)注算法的硬件實現(xiàn)。FPGA(Field Programmable Gate Array)在能耗、成本、運算速度等方面具有得天獨厚的優(yōu)勢, 已經(jīng)被廣泛應(yīng)用于各種數(shù)字信號處理和數(shù)字通信領(lǐng)域。本文重點研究FOFDM核心技術(shù)之一的可調(diào)FIR濾波器,設(shè)計并實現(xiàn)基于FPGA的可調(diào)節(jié)FIR濾波器。

近年來,基于FPGA的數(shù)字濾波器研究已經(jīng)取得了很多成果[114],其中文獻(xiàn)[14]的設(shè)計理念最接近本文。然而,從現(xiàn)有的文獻(xiàn)來看,并沒有可供參考的用于基于自適應(yīng)的空口波形技術(shù)的方法,此外,本文設(shè)計流程和側(cè)重點與文獻(xiàn)[14]也是不同的。本文第1節(jié)為核心模塊設(shè)計,第2節(jié)為MATLAB仿真結(jié)果和系統(tǒng)仿真結(jié)果,第3節(jié)給出了基本結(jié)論和下一步研究目標(biāo)。

1基于FPGA的可調(diào)FIR濾波器設(shè)計

該設(shè)計總體思路是:利用輸入波形的各項參數(shù),借助MATLAB中的FDAtool工具計算出FIR濾波器所需參數(shù),存入RAM。濾波器核心模塊讀取參數(shù)信息,調(diào)節(jié)濾波器的截止頻率等參數(shù),調(diào)節(jié)該模塊的功能。

利用DSP_Builder開發(fā)核心濾波器模塊的流程示意圖如圖1所示。

最基本的FIR濾波器的系統(tǒng)函數(shù)為:

可以用卷積表示為:

y(n)=x(n)*h(n)(2)

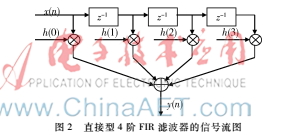

例如,一個典型的直接型4階FIR濾波器,其表達(dá)式[11] 可寫為式(3):

h(n)=h(0)x(n)+h(1)x(n-1)+h(2)x(n-2)+h(3)x(n-3)(3)

在圖2中,總共存在3個延時單元、4個乘法器和一個4輸入的加法器。

如果使用普通的數(shù)字信號處理器來實現(xiàn)這個4階FIR濾波器,只能用串行的方式順序地執(zhí)行延時、乘、加操作。這必須用到多個指令周期,而無法在一個指令周期內(nèi)完成。但是如果采用FPGA來實現(xiàn),就可以利用FPGA指令可以并行的優(yōu)點,在一個指令周期內(nèi)得到結(jié)果。

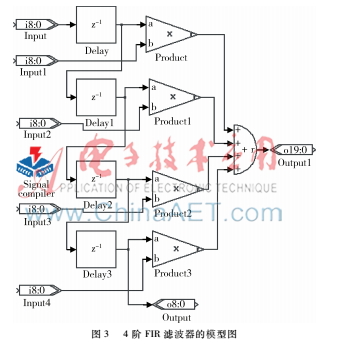

根據(jù)公式(3)和圖2,可以在Simulink中用DSP_Builder里的相關(guān)器件畫出一個圖3所示的4階FIR濾波器模型。

圖3中“Delay”為延時單元,“Product”為乘法器單元,“ParallelAdderSubtractor”為加法器單元,“Input”與“Output”分別為輸入輸出。

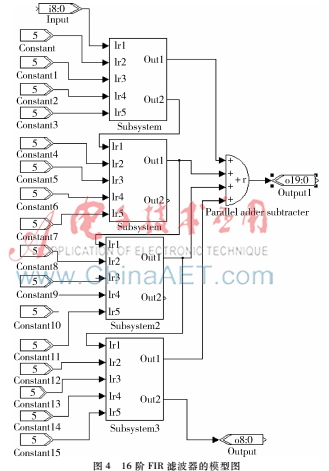

(1)設(shè)計4階FIR濾波器子系統(tǒng)

新建一個文件,將子系統(tǒng)模塊(Subsystem)放入文件中,雙擊打開子系統(tǒng)模塊,將上面已經(jīng)設(shè)計好的4階FIR濾波器放進(jìn)去,并對端口進(jìn)行修改。修改后的Subsystem模塊有5個輸入和2個輸出,“input”與“output”都修改為“Altbus”(因為它們不再作為主輸入端口,而是作為子系統(tǒng)的傳輸端口)。

(2)設(shè)計16階FIR濾波器

4階子系統(tǒng)完成后,按照圖4搭建一個16階的FIR濾波器。其中Constant模塊的初始值為5,需要另外計算,下文講解如何計算Constant值。

(3)計算Constant的值

Constant的值就相當(dāng)于h(n),是決定FIR濾波器具體性能的重要參數(shù),該值為濾波器要調(diào)節(jié)的核心參數(shù),它是通過濾波器的輸出和輸入信號的差值得到的。

(4)導(dǎo)出參數(shù)

點擊左上角的File,單擊Export,跳出Export界面,點擊下方的Export按鈕,可以將16個參數(shù)導(dǎo)出到MATLAB的主窗口。

(5)將參數(shù)填入FIR濾波器的模型中

在MATLAB仿真階段,該參數(shù)可以手動輸入到FIR濾波器Constant模塊中,這樣便完成了一個16階低通FIR濾波器的設(shè)計。在系統(tǒng)設(shè)計階段,步驟(4)計算結(jié)果會暫存在定制的RAM模塊中。

2設(shè)計驗證

2.1核心模塊仿真

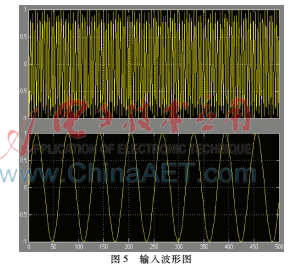

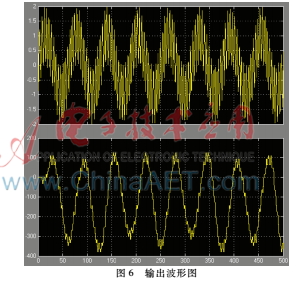

為了驗證設(shè)計的16階FIR濾波器正確與否,需要進(jìn)行仿真。為此,給濾波器的輸入端加上一個混合信號,混合信號包含一個40 Hz的高頻信號和一個0.013 Hz的低頻信號,兩個信號由Add模塊相疊加,再分別加上示波器模塊“Scope”來顯示波形結(jié)果。FDAtool設(shè)置就和上文所述相同,并將所得數(shù)據(jù)填入Constant模塊中,仿真時間設(shè)為500 s。

圖5的上方為40 Hz的波形,下方為0.013 Hz的波形。圖6的上方為輸入的混合信號波形,下方為濾波器輸出波形。將兩幅圖比較可以明顯看出,高頻信號40 Hz的波形被濾除,濾波器輸出的是低頻的0.013 Hz的信號。

2.2系統(tǒng)仿真

(1)將將mdl文件編譯生成VHDL語言;

(2)計算輸入信號和濾波器輸出的差值,將該值存入RAM;

(3)讀入RAM數(shù)據(jù),逐漸確定濾波器截止頻率;

(4)仿真。

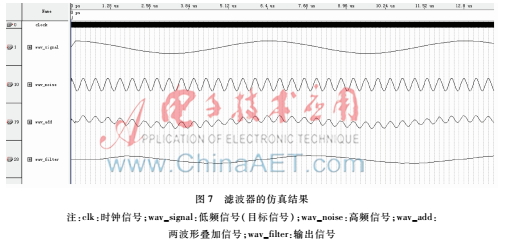

為了驗證所設(shè)計的可調(diào)FIR濾波器的正確性,設(shè)計了基于上述模塊的低通濾波器進(jìn)行波形的仿真。兩個正弦波疊加形成輸入信號,一個25 kHz信號人為標(biāo)記為噪聲信號,另一個4 kHz作為目標(biāo)信號,程序調(diào)節(jié)濾波器的截止頻率到4.5 kHz。仿真結(jié)果如圖7所示。由圖中可知,該濾波器濾除了高于截止頻率的信號部分,保留了低于截止頻率的信號部分,因此濾波器功能正確。調(diào)節(jié)輸入信號和截止頻率后,結(jié)果也能達(dá)到如圖7所示的效果。

3結(jié)論

本文FPGA設(shè)計了一種可調(diào)FIR濾波器,利用DSP Builder結(jié)合MATLAB的優(yōu)勢將該濾波器的設(shè)計簡化為MATLAB Simulink設(shè)計,大大縮短了設(shè)計時間。未來將進(jìn)一步完善可調(diào)濾波器設(shè)計,探索基于FPGA的可調(diào)FIR濾波器在實際通信系統(tǒng)中的實現(xiàn)方法,進(jìn)而提高通信系統(tǒng)效率。

參考文獻(xiàn)

[1] 李彬. FIR數(shù)字濾波器的FPGA實現(xiàn)技術(shù)研究[D]. 成都:西南交通大學(xué),2004.

[2] 劉朋全. 基于FPGA的FIR數(shù)字濾波器的設(shè)計和實現(xiàn)[D]. 西安:西北工業(yè)大學(xué),2006.

[3] 楊娜. 基于MATLAB與DSP的自適應(yīng)濾波器設(shè)計與實現(xiàn)[J]. 微型機(jī)應(yīng)用,2015,34(21):16-20.

[4] 杜勇. 數(shù)字調(diào)制解調(diào)技術(shù)的MATLAB與FPGA實現(xiàn)[M]. 北京:電子工業(yè)出版社,2015.

[5] 高耀鴻. 基于FPGA的FIR低通濾波器[D].長沙:湖南大學(xué),2012.

[6] 張馳. 基于Matlab的FIR濾波器設(shè)計及FPGA實現(xiàn)[J]. 應(yīng)用科技,2005,33(6):84-86.

[7] 孫耀奇. 基于Matlab和FPGA的FIR數(shù)字濾波器設(shè)計及實現(xiàn)[J]. 現(xiàn)代電子技術(shù),2008(11):89-92.

[8] 張園. 基于MATLAB和QuartusⅡ的FIR濾波器設(shè)計與仿真[J]. 電子工程師,2008,34(2):25-27.

[9] 阿依夏木·力提甫. 一種基于MATLAB及FPGA的FIR低通濾波器的設(shè)計與實現(xiàn)[D]. 烏魯木齊:新疆師范大學(xué),2011.

[10] 陳雁. 用MATLAB設(shè)計及FPGA實現(xiàn)FIR濾波器的方法[D].北京:北京航空航天大學(xué),2003.

[11] 宋千. 基于FPGA的FIR濾波器高效實現(xiàn)[J]. 信號處理,2001,17(5):385-391.

[12] 馬桂芳.基于FPGA和DSP Builder的FIR數(shù)字濾波器設(shè)計[J]. 常州工學(xué)院學(xué)報,2011,24(5):23-26.

[13] 彭雪峰. 基于MATLAB與QuartusⅡ的FIR濾波器設(shè)計與驗證[J]. 電子設(shè)計工程,2009,17(11):118-124.

[14] 陳虹,崔葛瑾.基于FPGA的系數(shù)可調(diào)FIR濾波器設(shè)計[J].實驗室研究與探索,2008,27(6)47-50.