牟剛

(炬芯(珠海)科技有限公司,廣東 珠海 519085)

摘要:手機(jī)的帶寬吞吐性能是影響手機(jī)總體性能的一個(gè)重要指標(biāo),目前幾乎所有第三方的手機(jī)評(píng)測(cè)軟件都有對(duì)這一項(xiàng)指標(biāo)的單獨(dú)測(cè)試。但這些測(cè)試基本上都存在一些問題,并不能全面真實(shí)地反映手機(jī)的帶寬吞吐性能。文章從硬件的角度深入分析了CPU、Cache、DDR等模塊的實(shí)現(xiàn)方式對(duì)帶寬測(cè)試軟件的影響,并結(jié)合最常用的ARM系列CPU做了對(duì)比,最后提出了新的帶寬吞吐性能評(píng)價(jià)方式。

關(guān)鍵詞: 帶寬;數(shù)據(jù)吞吐;Cache;DDR

中圖分類號(hào):TP368.1文獻(xiàn)標(biāo)識(shí)碼:ADOI: 10.19358/j.issn.1674-7720.2017.09.024

引用格式:牟剛.手機(jī)芯片帶寬性能評(píng)測(cè)手段的分析和優(yōu)化[J].微型機(jī)與應(yīng)用,2017,36(9):81-84.

0引言

隨著智能手機(jī)的快速普及,2015年全球的出貨量已達(dá)14億臺(tái)。這其中大半部分都是Android系統(tǒng)的手機(jī),它們的核心操作系統(tǒng)基本一樣,但硬件平臺(tái)就各有不同了。對(duì)手機(jī)硬件性能的評(píng)測(cè)成為了業(yè)界以及用戶所關(guān)注的重點(diǎn)[1]。相應(yīng)的,第三方的手機(jī)測(cè)評(píng)軟件就應(yīng)運(yùn)而生了。這些測(cè)評(píng)軟件往往將紛繁復(fù)雜的各項(xiàng)硬件性能轉(zhuǎn)化為一個(gè)個(gè)清晰明了的數(shù)字,讓消費(fèi)者以最直觀的方式了解一部手機(jī)的性能水平。由于其使用的簡便性和直觀性,不光是手機(jī)的最終消費(fèi)者經(jīng)常使用它作為手機(jī)選擇的參考,不少方案廠商也利用這些測(cè)評(píng)軟件作為手機(jī)芯片選擇的依據(jù)。

現(xiàn)代的手機(jī)主控芯片都是多核系統(tǒng),運(yùn)算能力越來越強(qiáng),但內(nèi)存性能卻提升有限[2]。因此內(nèi)存性能往往成為系統(tǒng)性能的瓶頸,對(duì)內(nèi)存帶寬吞吐性能的測(cè)試也顯得尤為重要。本文將分析目前帶寬性能測(cè)試軟件的一些局限性,結(jié)合硬件設(shè)計(jì)探討影響帶寬性能測(cè)試的因素,最后提出對(duì)帶寬性能測(cè)試優(yōu)化的方向。

1CPU測(cè)試帶寬的局限性

手機(jī)的主控芯片是個(gè)復(fù)雜的SoC(System on Chip),有多個(gè)主設(shè)備可以訪問DDR(內(nèi)存),DDR控制器的復(fù)雜程度也越來越高,它可以協(xié)調(diào)均衡各個(gè)主設(shè)備的訪問。但除了CPU,其他的主設(shè)備第三方用戶是不方便直接用軟件來控制的,如視頻編解碼模塊,這些模塊都需要專門的驅(qū)動(dòng)程序來控制,而驅(qū)動(dòng)程序都是由硬件廠商提供,第三方用戶不了解其中的細(xì)節(jié)。因此一般是利用統(tǒng)計(jì)CPU訪問DDR的速度來評(píng)估芯片總的帶寬吞吐性能。這就帶來一個(gè)問題,可能CPU全速運(yùn)行測(cè)試程序所需要的帶寬也達(dá)不到DDR能提供的理論帶寬,這時(shí)帶寬吞吐性能受限于CPU發(fā)讀寫命令的能力,而不是受限于DDR。

例如,以ARM cortexA9 CPU做仿真實(shí)驗(yàn),在CPU訪存接口上掛一個(gè)理想的32位DDR模型(有訪問請(qǐng)求立即響應(yīng),沒有延時(shí)),CPU頻率為1 008 MHz時(shí),測(cè)得數(shù)據(jù)拷貝帶寬為2 140 MB/s。而手機(jī)上一般會(huì)配置540 MHz 32位DDR,能提供的理論帶寬為4 320 MB/s,已經(jīng)遠(yuǎn)超cortex-A9的帶寬吞吐能力了,這種情況下帶寬性能測(cè)試得到的只是CPU的訪存性能,而不是DDR的總體帶寬性能。

2Cache對(duì)帶寬吞吐測(cè)試的影響

現(xiàn)在的帶寬吞吐性能評(píng)測(cè)軟件都是利用統(tǒng)計(jì)CPU訪問DDR的速度來評(píng)估芯片總的帶寬吞吐性能,這就需要考慮CPU Cache的影響。

為了加快訪問數(shù)據(jù)的速度,現(xiàn)代多核處理器通常包含私有緩存(L1 Cache)和末級(jí)共享緩存(L2 Cache)[3]。L1 Cache大小通常有幾十KB,L2 Cache通常有數(shù)百KB到幾MB。CPU對(duì)數(shù)據(jù)的訪問都會(huì)經(jīng)過Cache再到DDR。不同的Cache行為實(shí)現(xiàn)會(huì)導(dǎo)致CPU對(duì)DDR訪問量的巨大差異。

目前手機(jī)主控芯片幾乎都是采用ARM Cortex系列的CPU,下面就以ARM cortex系列最常用的CPU(A5,A7,A9,A53)來分析不同的Cache配置對(duì)CPU訪存性能的影響。

2.1對(duì)連續(xù)地址的寫操作

CPU對(duì)連續(xù)地址的寫入速度是反映帶寬性能的重要指標(biāo),軟件上對(duì)應(yīng)memset操作,用C語言描述如下:

int *dst;

for(int i=0;i<count;i++)

*dst= value

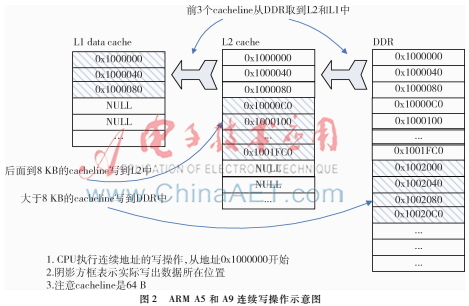

實(shí)際上由于Cache的存在,數(shù)值并不是直接寫到DDR中。對(duì)于ARM cortexA5和cortexA9 CPU,這一過程如圖1所示。

L1 data Cache一般都配置為write back + write allocate。但ARM對(duì)所有系列CPU的L1 Cache都做了優(yōu)化:檢測(cè)到連續(xù)地址3次Cache line的write操作,即自動(dòng)切換為write through + write no allocate。所以可以看到在圖中L1 data Cache只有前3個(gè)Cache line(0x1000000~0x1000040)的數(shù)據(jù)從DDR中讀取出來了,后面的數(shù)據(jù)就直接寫入L2 Cache了。

CortexA5和cortexA9的L2 Cache 依然是write back+write allocate。但沒有類似于L1 Cache那樣的自動(dòng)切換到write through + write no allocate的機(jī)制。所以每次從L1 data Cache有數(shù)據(jù)寫到L2 Cache,都應(yīng)該從DDR中讀取相應(yīng)地址的一個(gè)Cache line大小的數(shù)據(jù)分配到L2 Cache中,再對(duì)這個(gè)分配好的Cache line做寫操作。但實(shí)際上由于L1 data Cache每次對(duì)L2 Cache的寫操作都是一個(gè)Cache line的大小,即整個(gè)Cache line都被重寫了,因此也不用關(guān)心DDR中對(duì)應(yīng)這個(gè)Cache line地址的數(shù)據(jù)是什么了。這里L(fēng)2 Cache就直接分配了一個(gè)Cache line來存放L1 data Cache寫過來的數(shù)據(jù),沒有再去讀DDR。

ARM cortexA7和cortexA53的情況又有所不同,如圖2。

CortexA7和cortexA53的L1 data Cache 實(shí)現(xiàn)機(jī)制與前面一樣,但L2 Cache的實(shí)現(xiàn)不同。雖然同樣是write back + write allocate,但其有個(gè)自動(dòng)檢測(cè)機(jī)制,檢測(cè)到連續(xù)地址的127次Cache line的write操作可以自動(dòng)切換到write through+write no allocate。如圖2所示,地址0x1002000之后的數(shù)據(jù)就直接寫到DDR中了。

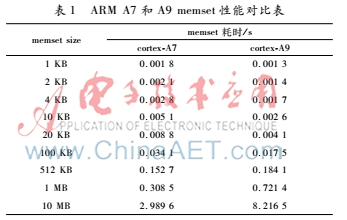

根據(jù)上面的分析,對(duì)于CPU向外寫數(shù)據(jù)的操作,在小于一定大小的情況下,實(shí)際上并不會(huì)操作DDR,而是在操作L2 Cache。表1是兩款手機(jī)CPU 同頻下的memset性能對(duì)比,它們的CPU分別使用了ARM cortexA7和cortexA9。

從表中數(shù)據(jù)可以看出,在size小于10 KB時(shí),cortexA9性能好于cortexA7,此時(shí)都是對(duì)L2 Cache的訪問,性能決定于CPU的指令發(fā)射能力以及流水線的亂序執(zhí)行能力,這些能力cortexA9都強(qiáng)于cortexA7。在10 KB <size <100 KB時(shí),cortexA9比cortexA7性能好得更明顯,因?yàn)榇藭r(shí)cortexA7已經(jīng)開始直接寫DDR了,而cortexA9依然在訪問L2 Cache。在size > 100 KB時(shí),cortexA9的性能逐漸被cortexA7反超,因?yàn)榇藭r(shí)cortexA9也開始有訪問DDR的操作了,size越大訪問DDR占比越大,最后幾乎完全是對(duì)DDR的訪問了。這時(shí)性能主要由DDR的性能決定。

2.2對(duì)連續(xù)地址的讀操作

CPU對(duì)連續(xù)地址的讀取速度也是反映帶寬性能的重要指標(biāo),可用C語言描述如下:

int *src;

for(int i=0;i<count;i++)

value = *(src + i);

cortexA5和cortex-A9的L2 Cache是非exclusive模式,即L1不命中時(shí),從DDR讀取回來的Cache line會(huì)保存在L2 Cache中。如圖3。

CortexA7和cortexA53的L2 Cache是exclusive模式,即L1不命中時(shí),從DDR讀取回來的Cache line不會(huì)保存在L2 Cache中。只有當(dāng)被改寫過的Cache line從L1 Cache刷出來時(shí)才會(huì)存到L2 Cache中。如圖4。

以上兩種實(shí)現(xiàn)方式各有利弊。做重復(fù)讀取性能測(cè)試時(shí),如果數(shù)據(jù)量小于L1 data Cache size,exclusive模式和非exclusive模式性能相當(dāng)。當(dāng)數(shù)據(jù)量大于L1 data Cache size,且小于L2 Cache size時(shí),非exclusive模式性能較好。當(dāng)數(shù)據(jù)量大于L2 Cache size時(shí),exclusive模式性能略好,如果除了讀操作還有其他的寫操作,那么exclusive模式性能優(yōu)勢(shì)就更明顯了,因?yàn)檫@種模式下讀操作占用了較少的L2 Cache,可以分配給其他操作使用。

2.3數(shù)據(jù)拷貝性能

數(shù)據(jù)拷貝是CPU最常見的訪存行為,也是帶寬性能測(cè)試軟件最常用的測(cè)試方式。數(shù)據(jù)拷貝包含了從源地址的讀數(shù)據(jù)操作和向目標(biāo)地址的寫數(shù)據(jù)操作。一般來講數(shù)據(jù)地址都是連續(xù)的。前面兩節(jié)討論了連續(xù)地址的寫操作和讀操作,這兩項(xiàng)性能也大致決定了數(shù)據(jù)拷貝的性能。

除此之外,DDR控制器在讀寫交替時(shí)的處理也會(huì)影響數(shù)據(jù)拷貝的性能。

DDR的地址線分為bank、row和column。一個(gè)bank中同時(shí)只能打開一個(gè)row,而處于不同bank中的row是可以同時(shí)打開的。為了充分利用這一特性來優(yōu)化DDR訪問效率,bank、row、column地址和物理地址的對(duì)應(yīng)方式會(huì)被精心設(shè)計(jì),有多種映射方式[4]。圖5是某款手機(jī)的地址排列方式。

假設(shè)做數(shù)據(jù)拷貝,源地址是0x100000(對(duì)應(yīng)row2,bank0),目標(biāo)地址是0x200000(對(duì)應(yīng)row4,bank0),它們對(duì)應(yīng)同一個(gè)bank的不同row。從源地址讀一組Cacheline大小的數(shù)據(jù),需要打開DDR的bank0_row2,然后CPU將這組數(shù)據(jù)寫入目標(biāo)地址,這時(shí)就需要先關(guān)閉bank0_row2,再打開bank0_row4。在這個(gè)讀寫交替的過程中,就有對(duì)DDR某一row的關(guān)閉和打開操作,需要耗費(fèi)較多的時(shí)間。

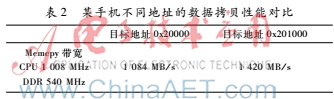

同樣還是做這樣的數(shù)據(jù)拷貝,如果將目標(biāo)地址換成0x201000(對(duì)應(yīng)bank1_row4),再做寫操作時(shí)就不用將bank0_row2關(guān)閉,直接打開bank1_row4就可以了。并且由于源和目標(biāo)地址的row都沒有關(guān)閉,后面的讀寫操作都不用再做打開row的操作了,這就大大地提高了數(shù)據(jù)拷貝的性能。表2是某款手機(jī)(采用cortex-A9 CPU)在不同目標(biāo)地址條件下數(shù)據(jù)拷貝性能的測(cè)試數(shù)據(jù)。

可以看到,僅僅是改變目標(biāo)地址就使連續(xù)地址的數(shù)據(jù)拷貝性能出現(xiàn)了很大差異,避免讀寫地址沖突后數(shù)據(jù)拷貝性能可提高31%。

3帶寬性能測(cè)試的優(yōu)化方向

前面分析了目前手機(jī)帶寬性能測(cè)試的局限性,并結(jié)合硬件設(shè)計(jì)探討影響帶寬性能測(cè)試的因素。根據(jù)這些因素,可以從以下幾個(gè)方面進(jìn)一步優(yōu)化完善帶寬性能測(cè)試方式:

(1)多個(gè)主設(shè)備同時(shí)訪問DDR,盡量達(dá)到DDR的帶寬極限。手機(jī)主控芯片中除了CPU,對(duì)帶寬需求最大的就是GPU[5],而GPU一般都可以通過上層的openGL軟件操作。GPU的測(cè)例可以使用多個(gè)圖層的疊加操作,這種操作對(duì)GPU的運(yùn)算能力需求較弱,對(duì)帶寬要求較高。在測(cè)試時(shí),讓CPU密集執(zhí)行數(shù)據(jù)拷貝操作,同時(shí)讓GPU做圖層疊加,結(jié)合兩者的實(shí)際完成時(shí)間給出帶寬性能評(píng)估分?jǐn)?shù)。

(2)用CPU測(cè)試數(shù)據(jù)拷貝性能,數(shù)據(jù)量要遠(yuǎn)大于L2 Cache的大小,避免Cache的影響。除了連續(xù)地址的數(shù)據(jù)拷貝,還要增加非連續(xù)地址的數(shù)據(jù)讀取性能測(cè)試,以避免CPU預(yù)取功能的影響,更真實(shí)地反映DDR的單次延時(shí)。如以下C代碼:

int *src;

for(int i=0;i<count;i+=STRIDE)

value = *(src+i);

注意STRIDE的取值要大于兩個(gè)Cache line size,以免觸發(fā)連續(xù)Cache line的預(yù)取操作。將連續(xù)地址的數(shù)據(jù)拷貝和非連續(xù)地址的數(shù)據(jù)讀取性能結(jié)合評(píng)估并打分。

(3)為全面考察不同地址對(duì)數(shù)據(jù)拷貝性能的影響,做多次數(shù)據(jù)拷貝操作,每次都改變一下目標(biāo)數(shù)據(jù)地址的偏移,如以下C代碼:

int *src, *dst;

for(int j=0;j<loop_count;j++)

for(int i=0;i<count;i++)

*(dst+i+j*0x1000) = *(src+i);

4結(jié)束語

第三方的帶寬吞吐性能測(cè)試軟件不僅為終端消費(fèi)者提供了手機(jī)性能的比較手段,也為手機(jī)方案廠商選擇芯片提供了可靠依據(jù),甚至最上游的芯片設(shè)計(jì)廠商也會(huì)利用這些測(cè)試軟件來指導(dǎo)芯片架構(gòu)的設(shè)計(jì)。本文提出的帶寬吞吐性能測(cè)試優(yōu)化方式可以更全面公正地評(píng)估手機(jī)芯片的實(shí)際性能,加快了芯片設(shè)計(jì)性能問題的收斂,具有良好效果。

參考文獻(xiàn)

[1] 楊怡君,黃大慶.Android手機(jī)自動(dòng)化性能測(cè)試工具的研究與開發(fā)[J]. 計(jì)算機(jī)應(yīng)用,2012,32(2):554-556.

[2] WULF W A, MCKEE S A. Hitting the memory wall: implications of the obvious[J]. SIGARCH Comput. Archit. News, 1995,23(1):20-24.

[3] 高珂,陳荔城,范東睿,等.多核系統(tǒng)共享內(nèi)存資源分配和管理研究[J]. 計(jì)算機(jī)學(xué)報(bào),2015,38(5):1021-1031.

[4] SHAO J, DAVIS B T. The bitreversal SDRAM address mapping[J]. In SCOPES ’05: Proceedings of the 2005 Workshop on Software and Compilers for Embedded Systems, ACM, 2005:62-71.

[5] 徐新海,林宇,斐易偉.CPUGPGPU異構(gòu)體系結(jié)構(gòu)相關(guān)技術(shù)綜述[J]. 計(jì)算機(jī)工程與科學(xué),2009,8(4):74-76.