隨著流程趨于完整,工具不斷精進和在市場上獲得認(rèn)可,先進封裝正在成為主流。

隨著在單個die上集成各式各樣的功能模塊(部件)的成本持續(xù)上升,先進封裝正迅速成為芯片制造商的主流選擇。

盡管圍繞這一轉(zhuǎn)變已經(jīng)有好幾年的討論,但實際情況是,它經(jīng)歷了半個多世紀(jì)才得以實現(xiàn)。上世紀(jì)60年代,先進封裝始于IBM的倒裝芯片,而在20世紀(jì)90年代,隨著多芯片模組的出現(xiàn),先進封裝技術(shù)又得到了進一步提升,特別是在mil/aero市場。盡管如此,先進封裝此前從未成為商業(yè)芯片制造商的首選,因為在硅領(lǐng)域,縮小特征尺寸的成本更低,針對等比例縮小的工具和IP生態(tài)系統(tǒng)已經(jīng)很好地建立起來,并且從設(shè)計到盈利的時間(time-to-profitability)也更明確。

隨著finFETs和double patterning的引入,16/14nm節(jié)點處的經(jīng)濟發(fā)生顯著變化。在更新的節(jié)點上,設(shè)計和制造成本將不斷增加。特征尺寸的縮小在5nm節(jié)點的過孔甚至和互連將需要新材料,5nm或3nm節(jié)點上需要新型晶體管結(jié)構(gòu)(目前來看,最可能的是全柵FET)。此外需要高數(shù)值孔徑的EUV,以及新的刻蝕、沉積和檢測設(shè)備。總而言之,這些步驟增加了在先進工藝流程中開發(fā)和制造芯片的成本,能夠用足夠的體量來對沖這劇增成本的市場機會變得越來越少。

盡管EUV技術(shù)的持續(xù)延遲迫使設(shè)計團隊采用metal1和metal2的多重曝光,但上述的那些因素對于半導(dǎo)體行業(yè)來說并不意外。然而,行業(yè)需要時間來開發(fā)可行的替代方案,并證明和改進方案。EDA供應(yīng)商正在提供設(shè)計工具和完整的流程,支持選擇各種封裝技術(shù)構(gòu)建芯片,并且在高可見性市場(高知名度市場)中生產(chǎn)足夠的先進封裝芯片,以證明該方案是可行的,比如蘋果、AMD、華為、思科、IBM和賽靈思(Xilinx)等供應(yīng)商,以及3D NAND、高帶寬內(nèi)存(HBM)和混合內(nèi)存立方體(Hybrid Memory Cube)等技術(shù)。

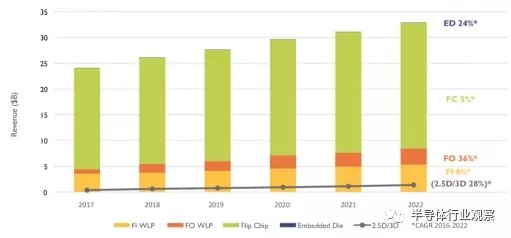

另外,在全球最大的IDM公司中,英特爾和三星現(xiàn)已提供低成本的專有橋接技術(shù)及代工服務(wù)。除了2.5D和3D封裝技術(shù)之外,所有主要的OSAT都提供一個或多個版本的扇出型晶圓級封裝(fan-out wafer-level packaging,fan-out WLP)技術(shù)。先進封裝各個領(lǐng)域的增長反映了這一現(xiàn)狀。

圖 1:不同平臺的先進封裝營收(縱坐標(biāo)單位為十億美元)。資料來源:Yole Developpement研究機構(gòu)于2017年5月發(fā)布的2017年先進封裝行業(yè)報告

自動化工具的設(shè)計

先進封裝市場增長的跡象之一是設(shè)計自動化工具的發(fā)展。在三大EDA供應(yīng)商中,Cadence是率先提供封裝工具和解決方案。早在上個世紀(jì)九十年代,Cadence就進入了這一市場,自2000年以來,它一直基于模擬芯片設(shè)計并不能簡單套用等比例縮小原理的事實而從事相關(guān)的工具開發(fā)。而這一遠(yuǎn)見花了近15年的時間,終于成為市場主流,其他EDA供應(yīng)商也發(fā)現(xiàn)了封裝領(lǐng)域是一個值得投入研發(fā)的機會。

本月初,被西門子收購的Mentor推出了用于先進封裝的流程和新工具。該公司的高級IC封裝解決方案部門——Board Systems Division的產(chǎn)品營銷經(jīng)理Keith Felton說:“這個工藝現(xiàn)在類似于硅工藝。我們預(yù)計將推出多個設(shè)計套件。因此,您將看到兩個用于fan-out晶圓級封裝的套件,每個封裝都有細(xì)微變化,同時還將推出堆疊die,基板上晶圓上芯片(chip on wafer on substrate,CoWoS),高引腳數(shù)倒裝芯片和系統(tǒng)級芯片封裝(system-in-package,SiP)等多種封裝技術(shù)”。

Felton表示,上述設(shè)計套件將與其他工具一起使用,包括DFMtools和PCB分析和驗證工具。

ANSYS總經(jīng)理兼副總裁John Lee表示:“這些都是基于物理的仿真。這不僅僅是關(guān)于半導(dǎo)體的問題,還是熱分析和機械模擬。以臺積電的InFO技術(shù)硅片的晶圓級封裝為例,由于明顯的物理效應(yīng),需要進行同步熱學(xué)分析。這可能發(fā)生在7nm、10nm、16nm甚至更早的工藝節(jié)點。但散發(fā)熱量的元件將影響系統(tǒng)的可靠性。所以如果你考慮的是電遷移而不是熱效應(yīng),那你的分析可能會偏悲觀;然而如果所以,如果你談?wù)摰氖请娺w移而不是熱量,那么你可能對世界有一個悲觀的看法。如果你的觀點不是悲觀的,那將會很危險的”。

Synopsys公司董事長兼聯(lián)合首席執(zhí)行官Aart de Geus表示,真正的關(guān)鍵在于將整個系統(tǒng)可視化,并構(gòu)建跨封裝方案的組件和工具。“因此,在IP解決方案上,你必須對其進行描述使之在任何情況下都有效。整體仿真是對由各種形式的多個芯片組成的系統(tǒng)進行仿真,當(dāng)然也包括軟件仿真。對設(shè)計人員來說,建立模型和原型的能力至關(guān)重要。包括針對數(shù)字和混合信號相關(guān)的設(shè)計”。

de Geus指出,它(代指上面的系統(tǒng)可視化?跨封裝方案的組件和工具?整體仿真?還是建立模型?我沒找到相關(guān)資料,前后文又聯(lián)系不起來,沒法準(zhǔn)確翻譯)該解決方案還包括硬件模擬(emulation)和軟件原型,“不管是在封裝內(nèi)部還是在7nm SoC上,你需要能夠在這些虛擬的硬件上運行軟件”。

但這些應(yīng)用于先進封裝的工具,在預(yù)測的準(zhǔn)確性上都還有很長一段路需要繼續(xù)探索。

“EDA設(shè)計工具將給半導(dǎo)體行業(yè)帶來巨大影響,”TechSearch International總裁Jan Vardaman表示:“如果沒有設(shè)計工具,很多事情都無法完成,未來工具應(yīng)用將更加廣泛。在一個設(shè)計中,只要劃分允許,你想盡可能多地使用成熟工藝,為此,我們迫切需要設(shè)計工具。”

封裝策略

“隨著產(chǎn)品一代代演進,我們的第一代方法逐漸成為常態(tài),”ASE的高級工程總監(jiān)Ou Li如是說,“隨著先進產(chǎn)品的發(fā)展,我們可以把所學(xué)到的東西用于其他產(chǎn)品,希望利用學(xué)習(xí)曲線、機器學(xué)習(xí)及產(chǎn)能,我們能夠容納其余的這些產(chǎn)品。因此,最先進的產(chǎn)品得到了產(chǎn)量和業(yè)務(wù)規(guī)模的支持。對于規(guī)模更小、更分散的市場來說,這些情況可能不會出現(xiàn)。但是對于產(chǎn)品需求來說則正好相反,這是因為我們已經(jīng)從其他產(chǎn)品中認(rèn)識到了這一點。”

盡管如此,市場分化仍然有影響。隨著由軟件所定義的設(shè)計越來越多(而不是利用通用硬件平臺將差異化編碼到軟件中),每個設(shè)計都變得與眾不同,并且終端客戶的要求也更為嚴(yán)格。

“每個不同類別的產(chǎn)品都面臨不同的挑戰(zhàn),”李說,“但對于系統(tǒng)級芯片封裝SiP來說,我們必須嚴(yán)格滿足客戶需求。這是所有先進封裝的趨勢。

下一步是開始構(gòu)建平臺,以便更快速地交換系統(tǒng)組件,并利用封裝增加所謂的“大規(guī)模定制(Mass Customization,MC)”方法。

STATS ChipPAC的全球產(chǎn)品營銷副總裁Scott Sikorski表示:“真正的機會是將所有功能集成到一個平臺上。這將推動下一個階段的增長。eWLB(嵌入式晶圓級球柵陣列)這種扇出型封裝可用于構(gòu)建那些已經(jīng)以不同方式構(gòu)建的芯片。”

企業(yè)采用這種封裝方案的速度還有待觀察。在過去的18個月里,人們對于fan-out的需求一直很高,但開發(fā)這類設(shè)備的能力有限。不過,最近這一情況發(fā)生了變化,因為封測代工廠OSAT提升了他們的產(chǎn)能。

Sikorski說:“現(xiàn)在更多OSAT企業(yè)具有了開發(fā)大量設(shè)備的能力,不久將有更多設(shè)備投入市場。”Sikorski指出,封裝作為一個集成平臺也開始受到關(guān)注。“由于你已經(jīng)擁有所有的基礎(chǔ)模塊,因此集成平臺是一種非常低成本的方法。最初,我們認(rèn)為這將是一種PoP(Package on Package)封裝形式,在芯片周圍存在一個通孔結(jié)構(gòu)。但是當(dāng)時我們認(rèn)為,供應(yīng)鏈還沒有準(zhǔn)備好。”

學(xué)習(xí)曲線

過去幾年的一大進步來自于在各種市場上使用先進封裝的經(jīng)驗。

“做封裝、測試和DFT的人現(xiàn)在成為了搖滾明星,”eSilicon營銷副總裁Mike Gianfagna說:“甚至封裝的復(fù)雜性也在增長。使用2.5D封裝技術(shù),必須考慮硅襯底、熱量和機械應(yīng)力以及更多的分析。因此,封裝和DFT團隊進入開發(fā)過程的時間更早一起,DFT甚至可以影響整個時間表。”

我們的目標(biāo)是在設(shè)計過程中增加更多的可預(yù)測性,而這需要時間。不過,企業(yè)高管和分析師認(rèn)為可預(yù)測性正在改善。

“這仍然不是常規(guī)的,因為任何新技術(shù)或技術(shù)節(jié)點都有學(xué)習(xí)曲線,”Gianfagna如是說,“幾乎在每一塊芯片上,我們都在首次嘗試某些新技術(shù)。但是,在識別問題,了解芯片、內(nèi)存、高性能I/O和基板之間的相互作用等方面,我們正在爭取做得更好。”

Cadence的engineering group director Brandon Wang說,所有主要的網(wǎng)絡(luò)公司現(xiàn)在都在采用2.5D設(shè)計。“明年將會推出新產(chǎn)品,”Wang說。“你將在其他芯片封裝中看到更多的傳感器,特別是MEMS芯片。盡管如此,這些設(shè)計的性質(zhì)是截然不同的。直到最近,許多設(shè)計(設(shè)計被分割 這種表述合理嗎?)都被分割得很細(xì),因此很難為它們創(chuàng)造出一套方法。但設(shè)計的方向是確定的,由于傳感器價格低廉,因此它們將成為更標(biāo)準(zhǔn)的設(shè)計單元。這更像是一種平臺化的方法,利用該方法你可以很快地獲得所需要的東西。”

要實現(xiàn)這一點,需要多個die的協(xié)同設(shè)計,其中傳感器參數(shù)與其余電子元件需同時進行調(diào)整。

“傳感器將無處不在,必須對它們進行協(xié)同優(yōu)化,”Wang說,“傳感器將變得更加以電氣為中心。電子設(shè)計師仍然專注于終端設(shè)備的產(chǎn)量,而平臺將使他們能夠?qū)W⒂陔姎庑阅懿⑴c傳感器平臺溝通。每個系統(tǒng)都將擁有傳感器,但你可以設(shè)計一個針對特定情況進行優(yōu)化的傳感器集線器(sensor hub)。這樣,如果你將5個傳感器集成為一個傳感器集線器,其價格不是單個傳感器的5倍,也許只有1.3倍。而且,它是一個標(biāo)準(zhǔn)的傳感器或傳感器集線器,所以你知道它的工作方式。”

對平臺上的關(guān)注是這一戰(zhàn)略的關(guān)鍵。這樣可以更容易地將異構(gòu)性添加到具有更強可預(yù)測性結(jié)果的設(shè)計中。但平臺也可以大大降低設(shè)計成本,因為它們具有經(jīng)濟上的規(guī)模效應(yīng),從而更具有競爭力。

ARM市場開發(fā)高級總監(jiān)Bill Neifert表示:“客戶正在尋求更多來自我們的指導(dǎo)和設(shè)計建議。去年我們提出了設(shè)計指導(dǎo),但不僅僅是關(guān)于處理器的,還關(guān)乎性能和功耗。 我們還有一個預(yù)先構(gòu)建的軟件平臺來幫助他們克服傳統(tǒng)的障礙。”

其中一個問題是,不再有一個最優(yōu)方法來完成某些工作。過去,工藝是由工藝過程的節(jié)點來度量的,對異構(gòu)性的強調(diào)大幅度增加了可能的選擇數(shù)目。并非所有功能都必須集成到單個die中,即使在同一工藝節(jié)點上,許多時候從一個代工廠到下一個代工廠,IP都會發(fā)生顯著變化。

“現(xiàn)在我們正在與主要合作伙伴一起參與到設(shè)計的各個方面。”Neifert說:“甚至包括早期RTL電路的設(shè)計,盡管更典型的情況是,RTL電路設(shè)計是在IP級而非子系統(tǒng)級上完成的。現(xiàn)在它包括從安全要求到安保的一切相關(guān)環(huán)節(jié)。我們試圖找出其中的薄弱環(huán)節(jié),這樣,當(dāng)我們把所有環(huán)節(jié)集成到一起之后,就沒有潛在問題了。”

上述情形僅僅是一個開始。EDA設(shè)計工具和流程的推出將在這些設(shè)備(前面幾段沒有設(shè)備相關(guān)的內(nèi)容,指代不明,譯成芯片?半導(dǎo)體設(shè)備?)中增加一個全新的控制級別。

“你將看到擁有更高精度、更小特征尺寸(的芯片),并且我們將開始以3D方式進行設(shè)計。”Mentor的Felton說:“你將能夠為基板‘假設(shè)’情況構(gòu)建藍圖,擁有包含熱驗證的芯片級模型。”

(學(xué)習(xí)曲線的)目標(biāo)是對不同的封裝方案進行早期分析,這對選擇基板、封裝類型、IP以及芯片內(nèi)部和芯片間的互連方式顯得尤其重要。

“用戶類型是各不相同的,” Felton說,“有的IC設(shè)計師和架構(gòu)師提出諸如堆疊die或PoP封裝類型,并將它們交給另一個團隊進行封裝設(shè)計。這需要專門的解決方案和流程。 使之從機械實現(xiàn)遷移到EDA設(shè)計工具上。”

結(jié)論

摩爾定律歷經(jīng)52年,單個die上的芯片設(shè)計和制造已經(jīng)可以非常容易地預(yù)測到了。整個生態(tài)系統(tǒng)也都已經(jīng)到位,它就像一臺精密調(diào)諧的機器。先進封裝需要時間才能達到同等水平的可預(yù)測性,但是現(xiàn)在有了足夠多的系統(tǒng)解決方案,而且有很多成功的封裝案例,先進封裝不再是一種巨大的賭博。隨著更多工具和可預(yù)測性被創(chuàng)造出來,它們的價格也將繼續(xù)下降,從而進一步支持fan-out和2.5D技術(shù)的實現(xiàn)。

大多數(shù)業(yè)內(nèi)人士認(rèn)為,少數(shù)幾家公司將繼續(xù)在最先進節(jié)點上縮減邏輯(尺寸),但越來越多的公司在將圍繞該邏輯的封裝中加入更多元素。未來是異構(gòu)的,最簡單的方法將是在一個封裝中(而非在單個die上)將這些元素集成起來。