郭京,沈華,段小虎

(中航工業(yè)西安航空計算技術研究所,陜西 西安 710068)

摘要:基于Xilinx芯片的FPGA集成了越來越多的可配置邏輯資源、各種各樣的外部總線接口以及豐富的內部RAM 資源。在FPGA的電路設計中,上電配置電路至關重要。其中,DONE信號上拉電阻阻值的選擇很容易被人忽略,錯誤的阻值選擇往往會導致意想不到的情況。通過采用4.7 kΩ電阻上拉DONE信號產(chǎn)生的試驗結果,來分析DONE信號上拉電阻必須為330 Ω的原因。

關鍵詞:FPGA;上拉電阻;DONE信號

中圖分類號:TP302.7文獻標識碼:ADOI: 10.19358/j.issn.1674-7720.2017.10.011

引用格式:郭京,沈華,段小虎.基于Xilinx芯片的FPGA的DONE信號上拉電阻阻值分析[J].微型機與應用,2017,36(10):37-39.

0引言

隨著半導體和芯片技術的飛速發(fā)展, 現(xiàn)在的現(xiàn)場可編程門陣列(FieldProgrammable Gate Array, FPGA)集成了越來越多的可配置邏輯資源、各種各樣的外部總線接口以及豐富的內部RAM 資源, 使其在國防、醫(yī)療、消費電子等領域得到了越來越廣泛的應用。但是FPGA 大多數(shù)是基于SRAM 工藝的, 具有易失性, 因此FPGA 通常使用外部存儲器件(如PROM) 存儲必需的配置信息, 防止設備掉電后FPGA丟失自我配置能力。但FPGA 配置在一定的條件和時間下才能成功完成, 隨著FPGA 容量的不斷攀升,配置時間也被大大加長, 上電時如不充分考慮FPGA的配置時序以及對其他器件的影響, 根據(jù)常規(guī)經(jīng)驗設計電路, 往往會影響系統(tǒng)其他外圍器件的正常工作, 嚴重時會導致整個系統(tǒng)的失效。因此, FPGA 的配置方式和上電時序已成為系統(tǒng)設計的重要一環(huán)[1]。本文主要分析在FPGA上電配置過程中,因DONE上拉電阻阻值的不同而引起的不同上電結果。

1FPGA的加載過程

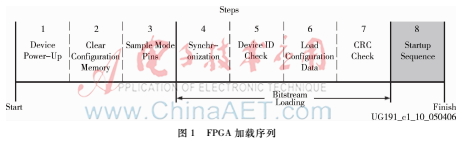

FPGA加載過程分為8個序列[1],如圖1所示。

在前7個步驟完成后,配置數(shù)據(jù)的CRC校驗完成,進入最后的Startup序列,Startup序列所需要處理的事件如圖2所示。

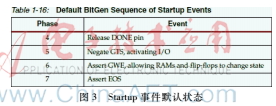

這7個事件的前后關系是可以在FPGA的目標碼bit文件生成選項中進行設置的,默認的設置順序如圖3所示。

所以,默認狀態(tài)下,F(xiàn)PGA在配置數(shù)據(jù)加載完并且通過CRC校驗后,依次完成以下工作:

(1)釋放DONE信號:配置數(shù)據(jù)加載期間FPGA驅動DONE信號為低,到Startup序列后FPGA將DONE信號置為高阻態(tài),靠外部上拉電阻將DONE信號拉為高。

(2)處理GTS事件:配置數(shù)據(jù)加載期間FPGA IO管腳為高阻態(tài)(或也可由FPGA的某個配置管腳將所有IO在配置數(shù)據(jù)加載期間設置為上拉,該管腳的名字通常為PUDC_B或HSWAPEN),到Startup序列后FPGA取消IO的高阻態(tài),使能其輸出。

(3)處理GWE事件:配置數(shù)據(jù)加載期間FPGA禁止RAM的寫入和flipflop狀態(tài)的改變,到Startup序列后使能RAM的寫入,并允許flipflop狀態(tài)發(fā)生改變。

默認狀態(tài)下DLL和DCI不作為Startup序列的一部分,由FPGA自行處理完成后進入Lock狀態(tài)。

2DONE信號上拉電阻與GTS事件

為了分析DONE信號上拉電阻阻值對上電配置的影響,本文將DONE信號上拉4.7 kΩ電阻來觀察造成的結果。使用一個離散量輸出作為GTS事件的標志,該離散量在VHDL源碼中賦為“0”,由于FPGA電路配置為在加載期間IO上拉,從而該離散量信號在GTS事件之前時為高電平,在GTS事件后變?yōu)榈碗娖剑撔盘柕碾娖阶兓蜆酥玖薌TS事件的發(fā)生,離散量無變化即為GTS未發(fā)生。FPGA采用XCF32P PROM Flash的CLKOUT作為配置時鐘CCLK的時鐘源。默認狀態(tài)下,該時鐘僅可輸出20 MHz或40 MHz時鐘,若使用MCS壓縮模式,該時鐘還可以輸出10 MHz時鐘。

當DONE信號上拉電阻阻值為4.7 kΩ時,經(jīng)過多種組合情況的測試,結果如表1所示。

通常而言,如果PCB走線較差,F(xiàn)PGA配置電路信號完整性不好,F(xiàn)PGA配置時鐘頻率較高時容易發(fā)生配置失敗,但這通常會使配置數(shù)據(jù)載入錯誤,造成CRC校驗錯誤,從而導致配置失敗。而在這樣配置環(huán)境中,即使采用40 MHz的配置時鐘,CRC校驗仍然不會發(fā)生錯誤,所以離散量不輸出并不是信號完整性較差引發(fā)的,肯定有著與GTS事件處理直接相關的原因。

進一步對GTS事件時配置電路的行為進行波形捕獲與分析,在不同的配置時鐘頻率下,使用示波器對該離散量、DONE信號、配置時鐘進行捕獲,獲得波形如圖4、圖5、圖6所示。

以上三幅圖中的T表示相應情況下的時鐘周期。總結分析如表2所示。

不同配置時鐘頻率下“DONE信號爬升時間”有所差異,DONE信號的爬升速度緩慢造成了GTS事件的失敗,在較低頻率的配置時鐘下,DONE信號需要較少時鐘周期即可為高,而在較高頻率的配置時鐘下,DONE信號需要較多時鐘周期才能升高。所以配置時鐘頻率較高時,發(fā)生GTS事件失敗的概率較高。

根據(jù)不同配置時鐘頻率下“DONE信號釋放到GTS事件時間”的差異,進一步得出GTS事件的發(fā)生需要對DONE信號的電平狀態(tài)進行回采,即FPGA在釋放DONE信號后,并不是在下一個時鐘周期立即執(zhí)行GTS事件,而是要在每個時鐘周期對DONE信號的狀態(tài)進行采集判斷,直至外部上拉電阻將DONE信號電平拉高之后才會開始執(zhí)行GTS事件。

根據(jù)GTS事件到配置時鐘終止時間,猜測XCF32P PROM Flash是根據(jù)FPGA的DONE信號電平狀態(tài)來決定何時終止CLKOUT配置時鐘的輸出,待其CE#管腳采集到DONE信號為高后,再給出7~8個配置時鐘周期,即終止配置時鐘。

至此,對GTS事件失敗的原因分析結果為:配置數(shù)據(jù)加載并校驗完成之后,F(xiàn)PGA釋放DONE信號,由外部上拉電阻將DONE信號拉為高,DONE信號開始爬升。FPGA對DONE信號的實際電平狀態(tài)進行回采,待其電平為高后執(zhí)行GTS事件。如果FPGA的DONE信號并未按照Xilinx手冊用330 Ω電阻上拉,而使用了4.7 kΩ電阻上拉,這就造成了DONE信號爬升太過緩慢,需要配置多個時鐘周期才可為高。這樣的話,在FPGA對DONE信號實際電平進行回采時,即有可能因為DONE信號有回溝而采集到混亂的DONE信號狀態(tài)(例如首先為高然后為低),這就可能造成GTS事件的失敗,從而造成FPGA 的IO管腳無法輸出,進而影響整個系統(tǒng)。

3分析結果的驗證

為驗證以上分析,需要加快DONE信號爬升速度,來觀測GTS事件失敗的情況。

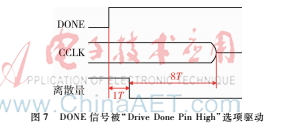

在FPGA的目標碼bit文件生成選項中,選擇“Drive Done Pin High”選項來使FPGA在配置數(shù)據(jù)加載并校驗完成之后,并不釋放DONE信號,而是主動將DONE信號驅動為高。選擇該選項后,DONE信號不再需要外部上拉電阻來驅動,而是由FPGA直接從低驅動為高,在這種情況下,示波器采集所獲波形如圖7所示。

在這種情況下,F(xiàn)PGA對DONE信號實際電平進行回采時,就不會再采集到DONE信號的不定態(tài),GTS事件不會再失敗。離散量也就輸出正常。

經(jīng)此選項后,在40 MHz配置時鐘下多次試驗,GTS事件也不會再失敗。

通過FPGA的目標碼bit文件生成選項可以更改GTS事件和GWE事件的前后關系。如果將GWE事件與GTS事件交換位置,則會發(fā)生GWE事件失敗而GTS事件成功的情況。這說明DONE信號釋放后的第一個事件會受到影響,再之后的事件由于DONE信號已爬升為高,因而不會再失敗。

4結論

Xilinx不直接對DONE信號進行驅高,而是由外部上拉電阻拉高,這樣可以讓多個FPGA的DONE信號連在一起,回采其信號,從而可使所有FPGA都加載完成之后,同步開始工作。

Xilinx要求使用330 Ω電阻對DONE信號進行上拉的原因是,該阻值可以保證在所允許的最高頻率的配置時鐘下,DONE信號仍可在一個時鐘周期內爬升為高,從而保證后續(xù)GTS事件的成功處理。

參考文獻

[1] 紀斌.Xilinx FPGA 上電時序分析與設計[J].電訊技術,2012,52(4):591-594.