ADRF6820是一款高度集成的解調(diào)器和頻率合成器,非常適合用于高級通信系統(tǒng)。 它內(nèi)置一個(gè)寬帶I/Q解調(diào)器、一個(gè)小數(shù)N/整數(shù)N分頻鎖相環(huán)(PLL)以及一個(gè)低相位噪聲多核壓控振蕩器(VCO)。 該多核VCO覆蓋2800MHz至5700MHz的基頻范圍。 本振(LO)輸出范圍為356.25 MHz至2850 MHz,可使用分頻器(2分頻、4分頻和8分頻)。

每個(gè)VCO內(nèi)核包含多個(gè)重疊子頻段,以覆蓋數(shù)百M(fèi)Hz的頻率范圍。 將寄存器0x44中的位0和寄存器0x45中的位7均設(shè)為0,PLL可自動(dòng)執(zhí)行VCO頻段校準(zhǔn)并支持選擇最佳VCO。

PLL鎖定過程包括兩個(gè)步驟:

1.通過內(nèi)部環(huán)路自動(dòng)選擇頻段(粗調(diào))。 在寄存器配置期間,PLL首先根據(jù)內(nèi)部環(huán)路進(jìn)行切換和配置。 隨后由一個(gè)算法驅(qū)動(dòng)PLL找到正確的VCO頻段。

2.通過外部環(huán)路細(xì)調(diào)。 PLL切換到外部環(huán)路。 鑒相器和電荷泵配合外部環(huán)路濾波器工作,形成一個(gè)閉環(huán),確保PLL鎖定到所需頻率。 校準(zhǔn)大約需要94,208個(gè)鑒頻鑒相器(PFD)周期;對于一個(gè)30.72 MHz fPFD,這相當(dāng)于3.07 ms。

校準(zhǔn)完成后,PLL的反饋操作使VCO鎖定于正確的頻率。 鎖定速度取決于非線性周跳行為。 PLL總鎖定時(shí)間包括兩個(gè)部分: VCO頻段校準(zhǔn)時(shí)間和PLL周跳時(shí)間。 VCO頻段校準(zhǔn)時(shí)間僅取決于PFD頻率;PFD頻率越高,鎖定時(shí)間越短。 PLL周跳時(shí)間由所實(shí)現(xiàn)的環(huán)路帶寬決定。 當(dāng)環(huán)路帶寬比PFD頻率窄時(shí),小數(shù)N分頻/整數(shù)N分頻頻率合成器就會發(fā)生周跳。 PFD輸入端的相位誤差積累過快,PLL來不及校正,電荷泵暫時(shí)沿錯(cuò)誤方向吸入電荷,使鎖定時(shí)間急劇縮短。 如果PFD頻率與環(huán)路帶寬的比值提高,周跳也會增加;對于給定PFD周期,提高環(huán)路帶寬會縮短周跳時(shí)間。

因此,當(dāng)使用自動(dòng)校準(zhǔn)模式時(shí),總鎖定時(shí)間對某些應(yīng)用來說可能太長。 本應(yīng)用筆記提出一種通過手動(dòng)選擇頻段來顯著縮短鎖定時(shí)間的方案,步驟如下:

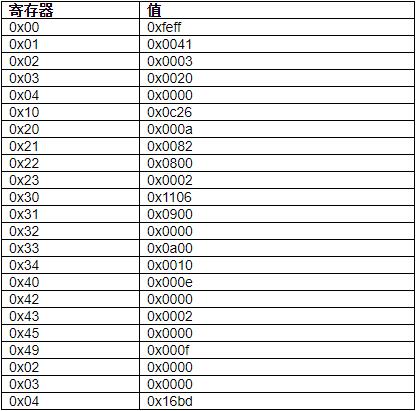

1.按照表1所示的寄存器初始化序列使器件上電。 默認(rèn)情況下,芯片以自動(dòng)頻段校準(zhǔn)模式工作。 根據(jù)所需的LO頻率設(shè)置寄存器0x02、寄存器0x03和寄存器0x04。

表1. 寄存器初始化序列

2.讀取鎖定檢測(LD)狀態(tài)位。 若LD為1,表明VCO已鎖定。

3.通過串行外設(shè)接口(SPI)回讀寄存器0x46的位[5:0]。 假設(shè)其值為A,將系統(tǒng)中所有需要的LO頻率對應(yīng)的寄存器值保存到EEPROM。 由此便可確定頻率和相關(guān)寄存器值的表格(參見表2)。

表2. 查找表

4.為縮短LD時(shí)間,將ADRF6820置于手動(dòng)頻段選擇模式,并用第3步收集到的數(shù)據(jù)手動(dòng)編程。 手動(dòng)編程步驟如下:

a)將寄存器0x44設(shè)置為0x0001: 禁用頻段選擇算法。

b)將寄存器0x45的位7設(shè)為1,從而將VCO頻段源設(shè)為已保存的頻段信息,而不是來自頻段計(jì)算算法。 用第3步記錄的寄存器值設(shè)置寄存器0x45中的位[6:0]。

c)通過寄存器0x22的位[2:0]選擇適當(dāng)?shù)腣CO頻率范圍(參見表3)。

表3. VCO頻率范圍

d)根據(jù)所需頻率更新寄存器0x02、寄存器0x03和寄存器0x04。 寄存器0x02設(shè)置分頻器INT值,即VCO頻率/PFD的整數(shù)部分;寄存器0x03設(shè)置分頻器FRAC值,即(VCO頻率/PFD ? INT) × MOD;寄存器0x04設(shè)置分頻器MOD值,即PFD/頻率分辨率。

e)監(jiān)視LD以檢查頻率是否鎖定。 例如,PFD = 30.72 MHz且LO = 1600 MHz。

表4. 手動(dòng)頻段校準(zhǔn)寄存器序列

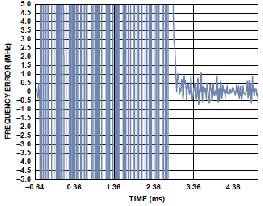

圖1和圖2分別顯示了自動(dòng)頻段校準(zhǔn)模式和手動(dòng)頻段校準(zhǔn)模式下的鎖定檢測時(shí)間。 圖2中,線1(鎖定檢測)上的高電平表示PLL已鎖定。 線2 (LE)代表LE引腳,是一個(gè)觸發(fā)信號。 注意:鎖定檢測時(shí)間必須從低到高讀取。

自動(dòng)頻段校準(zhǔn)模式下,鎖定時(shí)間約為4.5 ms;手動(dòng)頻段校準(zhǔn)模式下,鎖定時(shí)間約為360 μs。 數(shù)據(jù)的測量條件為20 kHz環(huán)路濾波器帶寬和250 μA電荷泵電流配置。

圖1. 自動(dòng)頻段校準(zhǔn)模式下的鎖定時(shí)間,用信號源分析儀測試

圖2. 手動(dòng)頻段校準(zhǔn)模式下的鎖定時(shí)間,用示波器測試

結(jié)論

利用手動(dòng)頻段選擇,鎖定時(shí)間從典型值4.5 ms縮短到典型值360 μs。 對于每個(gè)頻率,首先利用自動(dòng)頻段選擇確定最佳頻段值并予以保存。 因?yàn)樽罴杨l段值隨器件而異,因此須對每個(gè)ADRF6820執(zhí)行該程序。 VCO頻段無需因?yàn)闇囟茸兓隆?/p>