最近在學(xué)習(xí)RISCV相關(guān)的東西,發(fā)現(xiàn)了Berkeley一個(gè)很有意思的項(xiàng)目:HWACHA。這是一個(gè)使用RISCV開源處理器構(gòu)建的類vector的多核異構(gòu)系統(tǒng),可以用來(lái)做低算力的深度學(xué)習(xí)應(yīng)用。當(dāng)然HWACHA本身也是開源的,有興趣可以去github下載源碼跑跑看。這里還是從硬件設(shè)計(jì)的角度來(lái)分析下這種多核異構(gòu)系統(tǒng)的特點(diǎn)。

Summary:HWACHA使用了自定義的類Vector指令集,通過(guò)內(nèi)嵌調(diào)用的形式和RISCV ISA整合在一起。HWACHA的執(zhí)行類似于緊耦合的coprocessor,RISCV core負(fù)責(zé)循環(huán)的控制,Vector units負(fù)責(zé)主要的向量運(yùn)算。兩者通過(guò)特殊的指令進(jìn)行co-work,實(shí)現(xiàn)控制和運(yùn)算錯(cuò)拍的并行執(zhí)行。相比傳統(tǒng)的處理器Vector擴(kuò)展,HWACHA將integer和vector完全隔離,硬件設(shè)計(jì)相對(duì)簡(jiǎn)單且易于擴(kuò)展,可以提供良好的并行性。不過(guò)由于是獨(dú)立的指令集,需要和RISCV ISA一起聯(lián)合編譯,對(duì)compiler有特殊的要求。

HWACHA是Berkeley的一個(gè)research 項(xiàng)目,從2011年第一代起,幾乎每年都有流片,到V4架構(gòu)推出,已經(jīng)是第14款芯片了,好快的迭代速度。HWACHA項(xiàng)目的初衷是探索一個(gè)energy-efficient的Vector architecture,基于RISC open ISA,設(shè)計(jì)一種數(shù)據(jù)高并行的可擴(kuò)展結(jié)構(gòu)。

這里先簡(jiǎn)單介紹下vector的背景。向量計(jì)算(Vector)是一種特殊的單指令流多數(shù)據(jù)結(jié)構(gòu),主要面向科學(xué)運(yùn)算,加解密,建模分析等高強(qiáng)度的計(jì)算任務(wù)。例如ARM的SVE。相比于傳統(tǒng)的SIMD結(jié)構(gòu)(如ARM的Advanced SIMD擴(kuò)展),Vector的主要優(yōu)勢(shì)是良好的軟件可移植性,也就是說(shuō)相同的binary code,在不同規(guī)模的Vector機(jī)器上可以不經(jīng)改動(dòng)直接執(zhí)行,同時(shí)軟件編程中不需要考慮根據(jù)具體硬件執(zhí)行的寬度進(jìn)行數(shù)據(jù)重排。這種軟件透明的設(shè)計(jì)大大減輕了軟件設(shè)計(jì)和維護(hù)的代價(jià),因此在服務(wù)器領(lǐng)域應(yīng)用廣泛。

HWACHA的Vector指令集基本上類似于SVE,主要包括Vector寄存器堆VV0-VV255,Predicate寄存器堆VP0-VP15,以及向量控制寄存器VLEN。注意這里的vector寄存器有256個(gè)之多,大量的寄存器當(dāng)然有利于編譯器優(yōu)化,提升執(zhí)行性能,但是會(huì)對(duì)硬件設(shè)計(jì)主要是頻率帶來(lái)影響,后邊可以硬件為了支持這么大的寄存器尋址采取了特殊的機(jī)制。由于HWACHA是單獨(dú)的指令集,因此增加了一組標(biāo)量寄存器堆用作控制和標(biāo)量計(jì)算。這里比較特殊的是有獨(dú)立的地址寄存器堆VA0-VA31,這樣load和store就不會(huì)占用標(biāo)量寄存器號(hào),有利于更好的schedule計(jì)算和存儲(chǔ)。不過(guò)這樣就需要在指令編碼中有專用位來(lái)指定寄存器的類型。對(duì)傳統(tǒng)的32位指令編碼,這當(dāng)然是個(gè)問(wèn)題,會(huì)侵占指令編碼空間,不過(guò)HWACHA非常激進(jìn),直接采用了64位指令寬度,這樣一來(lái)編碼空間就不是問(wèn)題了。指令密度當(dāng)然會(huì)大不少,不過(guò)考慮到vector本身會(huì)以循環(huán)方式執(zhí)行,指令數(shù)目有限,那么這也不算是個(gè)很大的缺點(diǎn)。

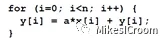

HWACHA的執(zhí)行方式是很有特點(diǎn)的。首先整個(gè)Vector Engine作為一個(gè)coprocessor,和主CPU之間是de-couple開的,通過(guò)特殊的指令和傳輸buffer進(jìn)行交互。而這種交互過(guò)程是interleave的,可以實(shí)現(xiàn)back2back的并行,因此從這個(gè)角度來(lái)看,又是couple在一起的。例如一個(gè)簡(jiǎn)單的for循環(huán)code:

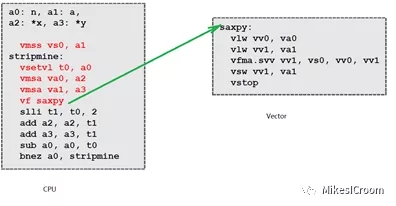

HWACHA的編譯器會(huì)將其分解為循環(huán)控制部分和向量執(zhí)行部分,前者在主CPU中執(zhí)行,后者在Vector engine中執(zhí)行。CPU通過(guò)一條特殊指令VF(Vector Fetch)來(lái)通知Vector engine開始執(zhí)行,VF的參數(shù)即為Vector執(zhí)行的起始PC。在后者執(zhí)行完成后,通過(guò)vstop(Vector Stop)指令來(lái)表示執(zhí)行暫停,等待下次VF的輸入。在Vector engine執(zhí)行的同時(shí),CPU繼續(xù)執(zhí)行,進(jìn)入下一拍循環(huán)進(jìn)行數(shù)據(jù)和控制準(zhǔn)備。這種方案可以提供CPU和Vector錯(cuò)開的并行執(zhí)行能力,同時(shí)控制和數(shù)據(jù)又能有效的隔離,一方面簡(jiǎn)化控制復(fù)雜度,另一方面Vector不受限于CPU的硬件結(jié)構(gòu)和帶寬,有很大的設(shè)計(jì)靈活性,比如HWACHA V4的一拖多結(jié)構(gòu):

CPU和Vector之間通過(guò)若干個(gè)Buffer進(jìn)行交互。當(dāng)CPU執(zhí)行到VF指令后,會(huì)將其push到VCMDQ中。Vector通過(guò)內(nèi)部的Scalar Unit從VF指定的PC開始取指執(zhí)行,取到的Vector指令會(huì)發(fā)送到Master sequencer中,由其負(fù)責(zé)分發(fā)到各個(gè)Vector unit中去執(zhí)行。每個(gè)Vector Unit就是一個(gè)in-order的Vector核,包括local sequencer負(fù)責(zé)內(nèi)部調(diào)度,Vector和Predicate寄存器堆,以及獨(dú)立的Vector Load&Store unit,通過(guò)Crossbar和片外存儲(chǔ)相連。在執(zhí)行過(guò)程中,每個(gè)Vector Unit都是獨(dú)立運(yùn)行的,只有指令(操作)從Master sequencer中統(tǒng)一取得。左邊還有一個(gè)Vector runahead Unit,應(yīng)該是負(fù)責(zé)提前計(jì)算一些執(zhí)行所需的信息,保證Vector Units的數(shù)據(jù)流的連貫性。整個(gè)架構(gòu)是一種特殊的SIMD形式,用較少的控制來(lái)驅(qū)動(dòng)大量的計(jì)算,而各個(gè)計(jì)算單元間又是獨(dú)立的,不需要像傳統(tǒng)SIMD指令那樣進(jìn)行同步。這樣控制當(dāng)然會(huì)簡(jiǎn)單,但同時(shí)也無(wú)法支持精確異常等控制流事件。不過(guò)考慮到Vector的主要應(yīng)用場(chǎng)景,這并不算是一個(gè)很大的問(wèn)題。

HWACHA的每個(gè)Vector Unit的結(jié)構(gòu)如上圖。Master Sequencer將譯碼后的指令分發(fā)給每個(gè)Unit的Lane sequencer,由后者進(jìn)行內(nèi)部schedule,包括dependency的檢查和處置。之前說(shuō)過(guò)HWACHA的Vector寄存器有256個(gè)之多,這么大的寄存器堆在實(shí)現(xiàn)上是很不友好的。為了平衡面積和時(shí)序,這里采用了4 BANK 單口SRAM來(lái)實(shí)現(xiàn)寄存器堆。這里就有一個(gè)問(wèn)題,指令通常有2~3個(gè)源操作數(shù),單口SRAM如何有效的進(jìn)行寄存器讀寫,特別是在幾個(gè)操作數(shù)處于同一個(gè)RAM BANK中?HWACHA采用一個(gè)稱為“Systolic Bank Execution”的機(jī)制,簡(jiǎn)單來(lái)說(shuō)就是指令按順序的訪問(wèn)RAM BANK0~3,指令i當(dāng)前cycle訪問(wèn)BANKk,如果操作數(shù)在這個(gè)BANK里,就取出來(lái),如果不在,就在下一個(gè)cycle訪問(wèn)BANKk+1。同時(shí)指令i+1在當(dāng)前cycle 訪問(wèn)BANKk-1。這樣的訪問(wèn)序列不停頓,指令會(huì)一直循環(huán)這個(gè)過(guò)程直到把所有的操作數(shù)都取到,就發(fā)送到執(zhí)行單元去執(zhí)行。寫回的數(shù)據(jù)也會(huì)進(jìn)入這個(gè)systolic的FIFO,直到它移動(dòng)到對(duì)應(yīng)的RAM BANK,再把數(shù)據(jù)寫回到寄存器堆中。這種繁瑣的機(jī)制更多的出于研究性質(zhì),用來(lái)探索采用SRAM實(shí)現(xiàn)寄存器的讀寫的可行性,而不論從性能上,還是硬件實(shí)現(xiàn)上都不是個(gè)友好的方案。通常還是采用多級(jí)可流水的,多讀口的registerfile實(shí)現(xiàn)更合適。

整個(gè)執(zhí)行單元的設(shè)計(jì)并沒(méi)有太多的特殊之處,該有的arithmetic unit都有了。比較有特點(diǎn)的是它把ALU放到了寄存器堆的BANK里,每個(gè)BANK都有一個(gè)。這樣的設(shè)計(jì)主要用來(lái)加速單cycle ALU的執(zhí)行,是對(duì)HWACHA SRAM寄存器堆結(jié)構(gòu)讀寫效率不高的缺陷的一種彌補(bǔ)。

整體來(lái)說(shuō),HWACHA是一個(gè)偏研究性質(zhì)的架構(gòu),很多問(wèn)題的解決并非從工程的思路出發(fā),選擇簡(jiǎn)潔高效的方案,而是更多地進(jìn)行多種可能性的探索。除去這些,HWACHA的控制數(shù)據(jù)de-couple的想法,以及Vector部分并行運(yùn)算的軟硬件協(xié)同支持,都很有特點(diǎn),同時(shí)HWACHA中指令集層面的部分思路,也已經(jīng)提交作為RISCV open ISA vector extension的標(biāo)準(zhǔn)。從這個(gè)角度來(lái)看,HWACHA的探索很有意義,也很成功。