近日,清華大學(xué)微電子所、未來芯片技術(shù)高精尖創(chuàng)新中心錢鶴、吳華強(qiáng)教授團(tuán)隊(duì)與合作者在《自然》在線發(fā)表了題為“Fully hardware-implemented memristor convolutional neural network”的研究論文,報(bào)道了基于憶阻器陣列芯片卷積網(wǎng)絡(luò)的完整硬件實(shí)現(xiàn)。

該存算一體系統(tǒng)在辦理卷積神經(jīng)網(wǎng)絡(luò)(CNN)時(shí)能效比前沿的圖形辦理器芯片(GPU)高兩個(gè)數(shù)質(zhì)級,可以說在一定程度上沖破了“馮諾依曼瓶頸”的限造:大幅提升算力的同時(shí),實(shí)現(xiàn)了以更小的功耗和更低的硬件成本完成復(fù)雜的計(jì)算。

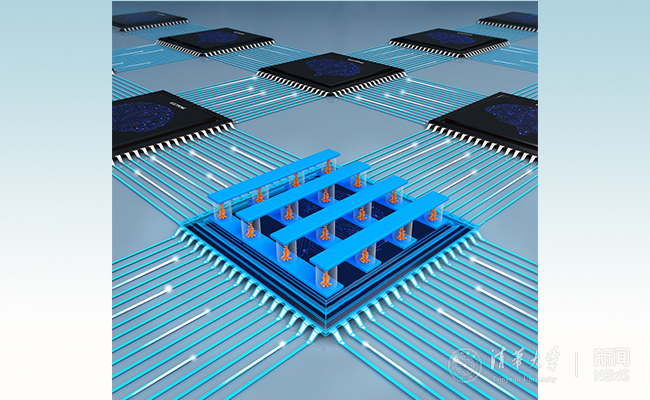

多個(gè)憶阻器陣列芯片協(xié)同工作示意圖。(圖自:清華新聞網(wǎng),下同)

基于憶阻器芯片的存算一體系統(tǒng)

什么是憶阻器?

憶阻器,全稱記憶電阻器(Memristor),是繼電阻、電容、電感之后的第四種電路基本元件,表示磁通與電荷之間的關(guān)系,最早由加州大學(xué)伯克利分校教授蔡少棠在1971年預(yù)言存在,惠普公司在2008年研制成功。

簡單來說,這種組件的的電阻會隨著通過的電流量而改變,而且就算電流停止了,它的電阻仍然會停留在之前的值,直到接受到反向的電流它才會被推回去,等于說能“記住”之前的電流量。

這種奇妙的效果,其實(shí)和神經(jīng)元突觸有相仿之處。再加上憶阻器還具有尺寸小、操作功耗低、可大規(guī)模集成(三維集成)等優(yōu)點(diǎn),難怪計(jì)算機(jī)科學(xué)家們在憶阻器身上看到了存算一體、低能耗類腦計(jì)算的前景。

人工神經(jīng)網(wǎng)絡(luò)近年來大放異彩,如果用憶阻器連接成陣列,作為人工神經(jīng)網(wǎng)絡(luò)的硬件,會有什么效果?

憶阻器陣列

當(dāng)前國際上的相關(guān)研究還停留在簡單網(wǎng)絡(luò)結(jié)構(gòu)的驗(yàn)證,或者基于少量器件數(shù)據(jù)進(jìn)行的仿真,基于憶阻器陣列的完整硬件實(shí)現(xiàn)仍然有很多挑戰(zhàn):器件方面,制備高一致、可靠的多值憶阻器陣列仍是挑戰(zhàn);系統(tǒng)方面,受憶阻器的阻變機(jī)理制約,器件固有的非理想特性(如器件間波動,器件電導(dǎo)卡滯,電導(dǎo)狀態(tài)漂移等)會導(dǎo)致計(jì)算準(zhǔn)確率降低;架構(gòu)方面,憶阻器陣列實(shí)現(xiàn)卷積功能需要以串行滑動的方式連續(xù)采樣、計(jì)算多個(gè)輸入塊,無法匹配全連接結(jié)構(gòu)的計(jì)算效率。

錢鶴、吳華強(qiáng)教授團(tuán)隊(duì)通過優(yōu)化材料和器件結(jié)構(gòu),成功制備出了高性能的憶阻器陣列。2017年5月,該課題組就曾在《自然通訊》報(bào)告稱,首次實(shí)現(xiàn)了基于1024個(gè)氧化物憶阻器陣列的類腦計(jì)算,將氧化物憶阻器的集成規(guī)模提高了一個(gè)數(shù)量級。這使芯片更加高效地完成人臉識別計(jì)算任務(wù),將能耗降低到原來的千分之一以下。

憶阻器神經(jīng)網(wǎng)絡(luò)

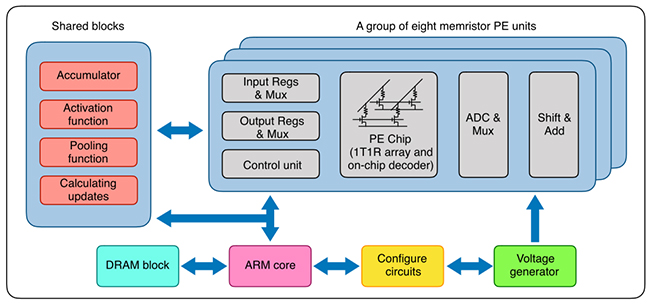

為解決器件非理想特性造成的系統(tǒng)識別準(zhǔn)確率下降問題,他們提出一種新型的混合訓(xùn)練算法,僅需用較少的圖像樣本訓(xùn)練神經(jīng)網(wǎng)絡(luò),并通過微調(diào)最后一層網(wǎng)絡(luò)的部分權(quán)重,使存算一體架構(gòu)在手寫數(shù)字集上的識別準(zhǔn)確率達(dá)到96.19%,與軟件的識別準(zhǔn)確率相當(dāng)。與此同時(shí),提出了空間并行的機(jī)制,將相同卷積核編程到多組憶阻器陣列中,各組憶阻器陣列可并行處理不同的卷積輸入塊,提高并行度來加速卷積計(jì)算。

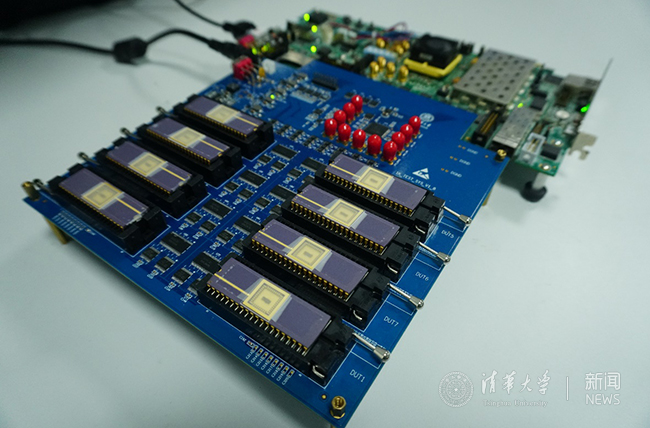

在此基礎(chǔ)上,該團(tuán)隊(duì)搭建了全硬件構(gòu)成的完整存算一體系統(tǒng),在系統(tǒng)里集成了8個(gè)包括2048個(gè)憶阻器的陣列,以提高并行計(jì)算的效率,并在該系統(tǒng)上高效運(yùn)行了卷積神經(jīng)網(wǎng)絡(luò)算法,成功驗(yàn)證了圖像識別功能,證明了存算一體架構(gòu)全硬件實(shí)現(xiàn)的可行性。

存算一體系統(tǒng)架構(gòu)

近年來,錢鶴、吳華強(qiáng)教授團(tuán)隊(duì)長期致力于面向人工智能的存算一體技術(shù)研究,從器件性能優(yōu)化、工藝集成、電路設(shè)計(jì)及架構(gòu)與算法等多層次實(shí)現(xiàn)創(chuàng)新突破,先后在《自然通訊》(Nature Communications)、《自然電子》(Nature Electronics)、《先進(jìn)材料》(Advanced Materials)等期刊以及國際電子器件會議 (IEDM)、國際固態(tài)半導(dǎo)體電路大會(ISSCC)等頂級學(xué)術(shù)會議上發(fā)表多篇論文。

團(tuán)隊(duì)合影

清華大學(xué)微電子所吳華強(qiáng)教授是本論文的通訊作者,清華大學(xué)微電子所博士生姚鵬是第一作者。該研究工作得到了國家自然科學(xué)基金委、國家重點(diǎn)研發(fā)計(jì)劃、北京市科委、北京信息科學(xué)與技術(shù)國家研究中心及華為技術(shù)有限公司等支持。