利用片上高速網(wǎng)絡(luò)(2D NoC)創(chuàng)新地實(shí)現(xiàn)FPGA內(nèi)部超高帶寬邏輯互連

2020-02-28

作者:Achronix資深現(xiàn)場(chǎng)應(yīng)用工程師 黃侖

來源:Achronix

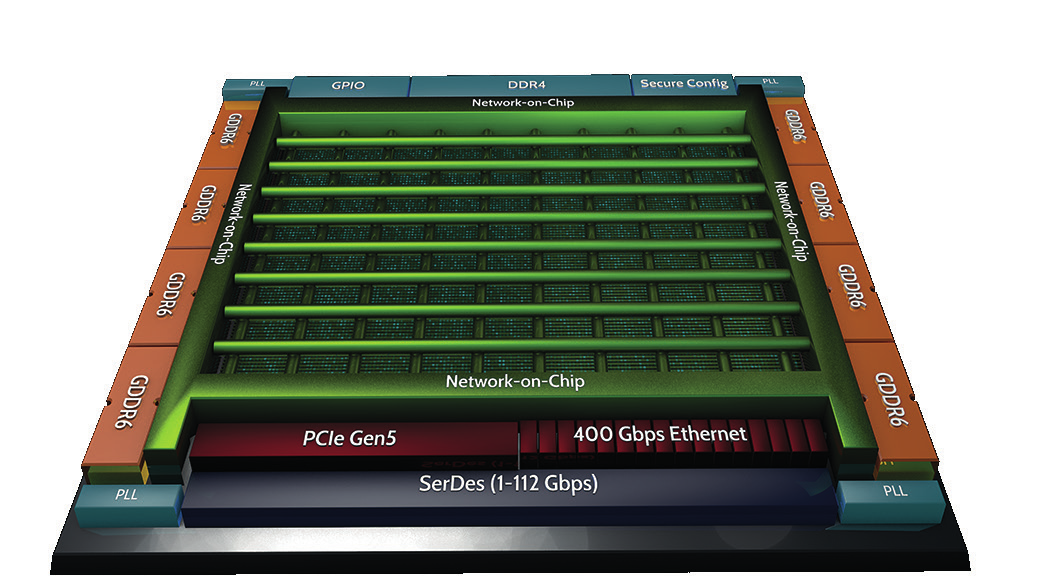

Achronix 最新基于臺(tái)積電(TSMC)的7nm FinFET工藝的Speedster7t FPGA器件包含了革命性的新型二維片上網(wǎng)絡(luò)(2D NoC)。2D NoC如同在FPGA可編程邏輯結(jié)構(gòu)上運(yùn)行的高速公路網(wǎng)絡(luò)一樣,為FPGA外部高速接口和內(nèi)部可編程邏輯的數(shù)據(jù)傳輸提供了超高帶寬(~27Tbps)。

圖1 Speedster 7t FPGA結(jié)構(gòu)圖

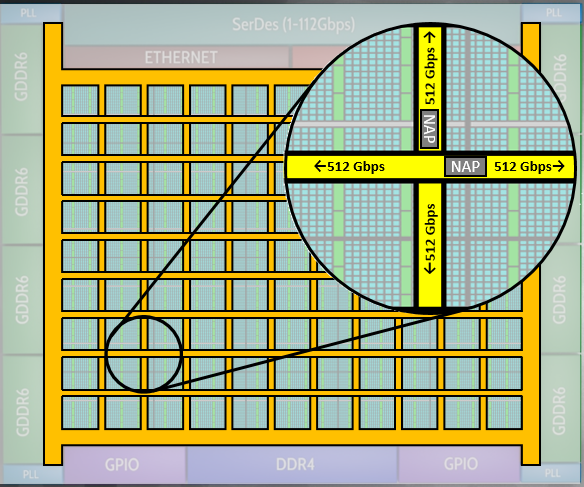

NoC使用一系列高速的行和列網(wǎng)絡(luò)通路在整個(gè)FPGA內(nèi)部分發(fā)數(shù)據(jù),從而在整個(gè)FPGA結(jié)構(gòu)中以水平和垂直方式分發(fā)數(shù)據(jù)流量。NoC中的每一行或每一列都有兩個(gè)256位的、單向的、行業(yè)標(biāo)準(zhǔn)的AXI通道,可以在每個(gè)方向上以512Gbps(256bit x 2GHz)的傳輸速率運(yùn)行。

NoC為FPGA設(shè)計(jì)提供了幾項(xiàng)重要優(yōu)勢(shì),包括:

·提高設(shè)計(jì)的性能。

·減少邏輯資源閑置,在高資源占用設(shè)計(jì)中降低布局布線擁塞的風(fēng)險(xiǎn)。

·減小功耗。

·簡(jiǎn)化邏輯設(shè)計(jì),由NoC去替代傳統(tǒng)的邏輯去做高速接口和總線管理。

·實(shí)現(xiàn)真正的模塊化設(shè)計(jì)。

本文用一個(gè)具體的FPGA設(shè)計(jì)例子來展現(xiàn)NoC在FPGA內(nèi)部邏輯互連中發(fā)揮的重要作用。本設(shè)計(jì)主要是實(shí)現(xiàn)三重?cái)?shù)據(jù)加密解密算法(3DES)。該算法是DES加密算法的一種模式,它是對(duì)于每個(gè)數(shù)據(jù)塊應(yīng)用三次DES加密算法,通過增加DES的密鑰長(zhǎng)度增加安全性。

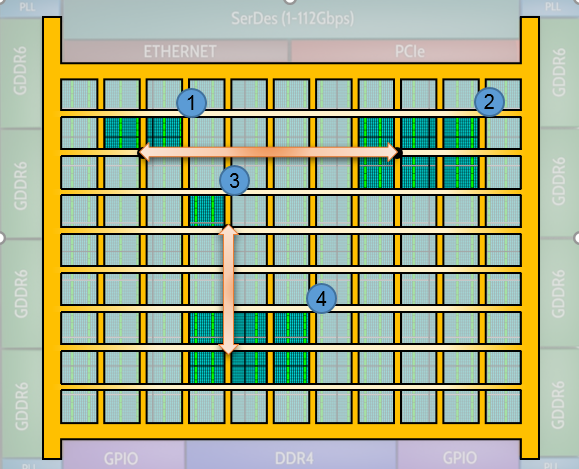

在該FPGA設(shè)計(jì)中,我們將輸入輸出管腳放在的FPGA上下左右四個(gè)方向上。上面管腳進(jìn)來的數(shù)據(jù)經(jīng)過邏輯1進(jìn)行解密然后通過藍(lán)色的走線送到邏輯2加密以后從下面的管腳送出。左邊管腳進(jìn)來的數(shù)據(jù)經(jīng)過邏輯3進(jìn)行解密然后通過紅色的走線送到邏輯4加密以后從右邊的管腳送出。如圖2 所示。

圖2 3DES設(shè)計(jì)(沒有用NoC)后端布局布線圖

本設(shè)計(jì)遇到的問題如下:

·加密和解密模塊中間的連線延時(shí)太長(zhǎng),如果不增加流水寄存器(pipeline),設(shè)計(jì)性能會(huì)收到很大限制。但是由于連接總線位寬是256位,增加幾級(jí)流水寄存器又會(huì)占用很多額外的寄存器資源。

·上下模塊之間的連接總線和左右模塊之間的連接總線出現(xiàn)了交叉,如果設(shè)計(jì)再復(fù)雜一點(diǎn)有可能會(huì)遇到布局布線局部擁塞,會(huì)大大增加工具布局布線時(shí)間。

上面兩個(gè)問題也是廣大FPGA設(shè)計(jì)者在復(fù)雜FPGA設(shè)計(jì)中或多或少會(huì)遇到的問題,導(dǎo)致的原因有可能是設(shè)計(jì)比較復(fù)雜,也有可能是硬件平臺(tái)的限制,或者設(shè)計(jì)必須連接不同位置的外圍Hard IP導(dǎo)致。

NoC的出現(xiàn)讓我們上面遇到的問題迎刃而解。NoC為FPGA邏輯內(nèi)部互連提供了雙向288bit的原始數(shù)據(jù)模式(Raw data mode)。 用戶可以通過這288bit的信號(hào)進(jìn)行邏輯直連或者自定義協(xié)議互連。

圖3 利用2D NoC進(jìn)行內(nèi)部邏輯互連

在NoC的每個(gè)交叉點(diǎn)上都有兩個(gè)網(wǎng)絡(luò)接入點(diǎn)(NAP),用戶只要簡(jiǎn)單地通過例化NAP的原語或者宏定義就可以將自己的邏輯接入到NoC并進(jìn)行互連。

圖4 網(wǎng)絡(luò)接入點(diǎn)NAP

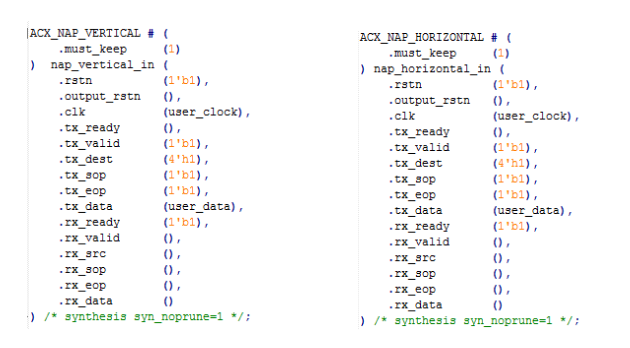

圖5 例化NAP宏定義示例

這樣通過在3DES加密和解密模塊上分別例化NAP,就可以實(shí)現(xiàn)3DES加密和解密模塊之間的NoC互連。

圖6 3DES設(shè)計(jì)(利用NoC)后端布局布線圖

這樣在簡(jiǎn)化用戶設(shè)計(jì)的同時(shí),設(shè)計(jì)性能有了很大的提高,從之前的260MHz提高到了750MHz。 圖6中可以看到之前邏輯之間大量的連接總線已經(jīng)看不到,總線的連接都由NoC接管,在后端布局布線圖中只能看到綠色時(shí)鐘走線和白色模塊內(nèi)部的邏輯走線。

本文主要想通過這樣一個(gè)例子給廣大FPGA設(shè)計(jì)者展示如何利用NoC來進(jìn)行FPGA內(nèi)部邏輯的互連,從而給廣大FPGA設(shè)計(jì)者提供另一種考慮問題的思路。在傳統(tǒng)的FPGA設(shè)計(jì)中出現(xiàn)了性能無法提升,布局布線擁塞的時(shí)候,是否可以考慮利用Achronix新一代的Speedster7t FPGA來簡(jiǎn)化和加速用戶的設(shè)計(jì)。

本公眾號(hào)今后也將會(huì)陸續(xù)推出關(guān)于二維片上網(wǎng)絡(luò)(NoC)的系列文章,比如NoC技術(shù)的發(fā)展,NoC性能評(píng)測(cè)以及與傳統(tǒng)互連架構(gòu)的對(duì)比,Speedster7t FPGA中NoC的技術(shù)參數(shù)以及調(diào)用方法,關(guān)于NoC的各種參考設(shè)計(jì)等等,敬請(qǐng)期待。