Achronix創(chuàng)新的機(jī)器學(xué)習(xí)處理器(MLP)突破傳統(tǒng)FPGA時(shí)序性能瓶頸

2020-04-27

作者:楊宇,Achronix資深現(xiàn)場(chǎng)應(yīng)用工程師

來源:Achronix

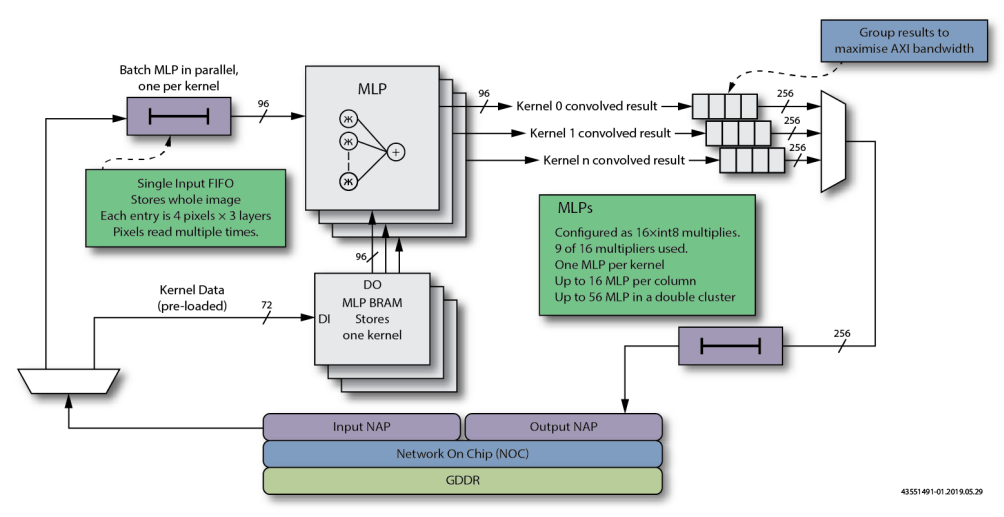

MLP_Conv2D是功能齊全的設(shè)計(jì),可將2D輸入圖像與多個(gè)內(nèi)核同時(shí)進(jìn)行卷積。 該設(shè)計(jì)充分利用了MLP和BRAM模塊,每個(gè)MLP一個(gè)周期執(zhí)行12個(gè)int8乘法。此外,MLP列和BRAM塊均等級(jí)聯(lián)以有效地將圖像數(shù)據(jù)傳遞,從而允許同時(shí)處理多個(gè)內(nèi)核。

該設(shè)計(jì)使用NoC接入點(diǎn)(NAP)從片上網(wǎng)絡(luò)(NoC)讀取或?qū)懭霐?shù)據(jù)。NoC連接到Speedster7t器件中的GDDR6控制器再到外部存儲(chǔ)器。

AlexNet

盡管最初為AlexNet圖像和內(nèi)核大小配置了MLP_Conv2D設(shè)計(jì),但是2D卷積是一個(gè)通用過程,因此可以重新配置該設(shè)計(jì)并使其適應(yīng)許多不同的2D方法。

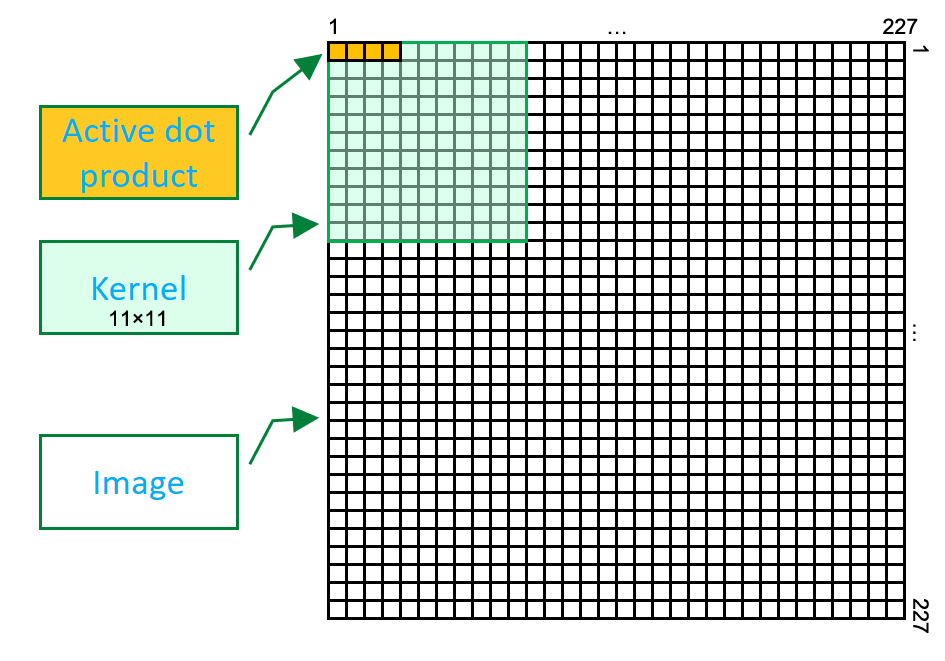

2D卷積的一般原理是在圖像(實(shí)際上是另一個(gè)2D矩陣)上傳遞內(nèi)核(2D矩陣)。對(duì)于每次計(jì)算,內(nèi)核均以輸入圖像的像素為中心,并對(duì)每個(gè)內(nèi)核值(稱為權(quán)重)與其當(dāng)前對(duì)齊的像素執(zhí)行乘法運(yùn)算。這些乘法的總和給出了原始圖像像素的特定卷積結(jié)果。然后將內(nèi)核移至下一個(gè)像素,并重復(fù)該過程。

經(jīng)過訓(xùn)練的內(nèi)核,2D卷積生成一個(gè)輸出結(jié)果圖像,突出顯示輸入圖像的特定特征,例如垂直線,水平線,變化角度的對(duì)角線和變化半徑的曲線。然后可以將這些特征輸入到其他處理層(包括其他2D卷積),然后可以將其標(biāo)識(shí)為(通常在軟件中)為特定對(duì)象。

因此,二維卷積處理不應(yīng)被視為圖像識(shí)別的完整解決方案,而應(yīng)被視為處理操作鏈中的單個(gè)關(guān)鍵組件。

乘法密度

2D卷積的挑戰(zhàn)是所需的乘法數(shù)量,這就是MLP中專用的乘法器陣列。對(duì)于AlexNet配置,每個(gè)內(nèi)核為11×11= 121個(gè)權(quán)重值。但是,卷積實(shí)際上是3D的,因?yàn)檩斎雸D像具有三層(RGB),因此一組內(nèi)核有121×3 = 363個(gè)乘法來產(chǎn)生單個(gè)輸出結(jié)果。AlexNet輸入圖像為227×227;但是,此圖像的stride為4(在計(jì)算之間內(nèi)核移動(dòng)了四個(gè)像素)。此過程導(dǎo)致輸出結(jié)果矩陣為54×54 = 2916個(gè)結(jié)果。因此,對(duì)于一幅圖像需要363×2916 = 1,058,508次乘法;即處理一個(gè)圖像需要進(jìn)行一百萬次以上的累加運(yùn)算。其中單個(gè)Kernel進(jìn)行2D卷積的動(dòng)態(tài)示意圖如下:

圖表 1 單個(gè)Kernel進(jìn)行2D卷積的動(dòng)態(tài)示意圖

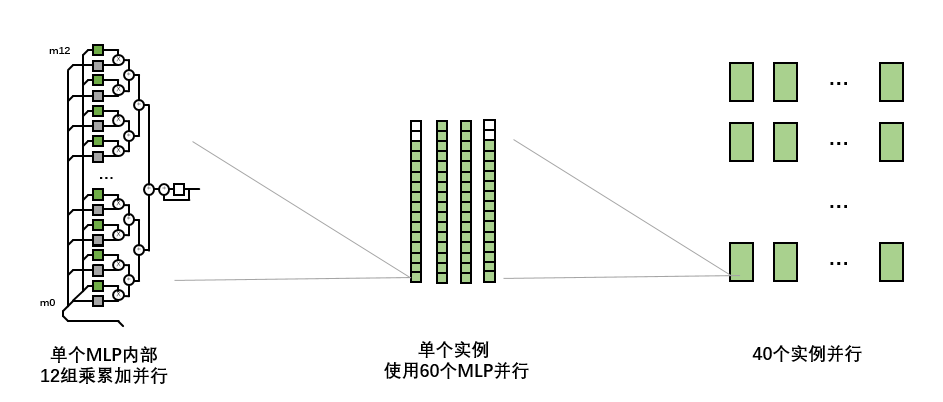

對(duì)于MLP_Conv2D,其設(shè)計(jì)旨在一次處理一幅圖像中的60個(gè)內(nèi)核,單次執(zhí)行超過6000萬次乘法累加操作。

性能

MLP_Conv2D設(shè)計(jì)可以以750 MHz的頻率運(yùn)行。單個(gè)MLP能夠在137 μs內(nèi)對(duì)具有11×11內(nèi)核的單個(gè)227×227 RGB輸入圖像進(jìn)行卷積,相當(dāng)于每秒15.4GOPS(包含乘和加)。 但一個(gè)MLP_Conv2D實(shí)例由60個(gè)并行運(yùn)行的MLP構(gòu)成,可以同時(shí)對(duì)60個(gè)輸入圖像進(jìn)行卷積,相當(dāng)于924GOPS。 最后,將多達(dá)40個(gè)MLP_Conv2D實(shí)例化到單個(gè)器件中,每個(gè)實(shí)例都通過自己的NAP將數(shù)據(jù)傳輸?shù)紾DDR6存儲(chǔ)器,從而實(shí)現(xiàn)了組合高達(dá)37 TOPS的性能-相當(dāng)于每秒處理28,8000張圖像(本設(shè)計(jì)主要針對(duì)卷積核)。

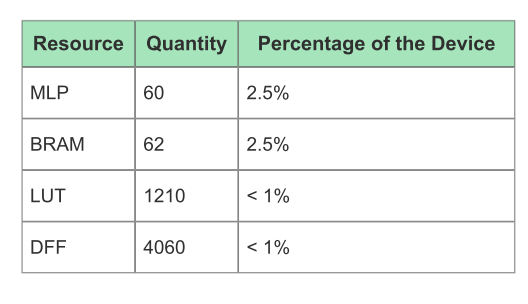

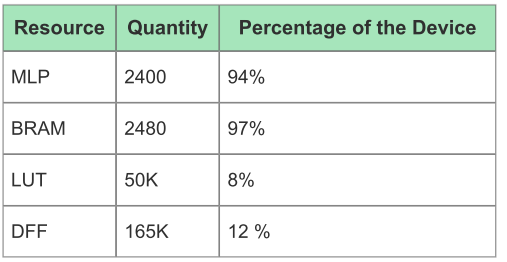

資源

MLP_Conv2D圍繞MLP和BRAM塊功能而設(shè)計(jì),并使用它們各自的內(nèi)部級(jí)聯(lián)走線。 同樣,NAP允許直接從外部存儲(chǔ)器路由數(shù)據(jù)互聯(lián)。這些功能可實(shí)現(xiàn)最小的附加邏輯或路由要求,利用率表如下:

圖表 2 單個(gè)MLP_Conv2D實(shí)例資源使用

圖表 3 并行40個(gè)MLP_Conv2D實(shí)例資源使用

圖表 4 MLP_Conv2D框圖

數(shù)據(jù)流:?jiǎn)蝹€(gè)MLP

每個(gè)MLP都有一個(gè)鄰近的BRAM。 在此設(shè)計(jì)中BRAM用于存儲(chǔ)內(nèi)核并將其多次傳遞到MLP。 初始化時(shí),將從輸入NAP中讀取不同的內(nèi)核,并將其寫入相應(yīng)的BRAM。 BRAM在寫側(cè)配置為72位,而讀取設(shè)置為144位。在操作期間,僅將96位用作內(nèi)核權(quán)重,即讀取為4個(gè)權(quán)重×3層×8位。初始圖像數(shù)據(jù)從NAP讀取到輸入FIFO中,該輸入FIFO用于將圖像存儲(chǔ)為一系列行。盡管此輸入存儲(chǔ)器被列為FIFO,但仍可作為可重復(fù)讀取的FIFO,因?yàn)榭梢远啻螐闹凶x取行。該存儲(chǔ)器配置為144位寬,僅使用96位,由兩個(gè)BRAM72K組成。每個(gè)字由4個(gè)像素×3層×8位組成。初始化時(shí),將讀取足夠的行以匹配內(nèi)核中的行數(shù)加上垂直跨步所需的行數(shù)。即

一旦加載了初始數(shù)據(jù)和內(nèi)核,便開始計(jì)算。

從輸入FIFO中讀取第一條圖像行,并讀取與內(nèi)核水平大小匹配的圖像數(shù)據(jù)像素?cái)?shù)量。在讀取這些像素時(shí),將讀取匹配的內(nèi)核權(quán)重。MLP將這些96位流的每一個(gè)乘以12個(gè)int8值并累加結(jié)果。輸入FIFO前進(jìn)到第二行,重復(fù)此過程,直到內(nèi)核的所有行都與輸入圖像左上角的適當(dāng)像素相乘。在此過程中,MLP積累了結(jié)果;現(xiàn)在,該結(jié)果是圖像與內(nèi)核卷積的左上角的2D卷積。該結(jié)果以16位結(jié)果的形式從MLP輸出。重復(fù)此過程,輸入FIFO跨行超前STRIDE參數(shù)設(shè)置的像素?cái)?shù)(對(duì)于當(dāng)前設(shè)計(jì),STRIDE固定為4)。在每個(gè)處理周期包括在內(nèi)時(shí),都會(huì)生成另一個(gè)結(jié)果,直到水平地獲取了適當(dāng)數(shù)量的結(jié)果為止。

然后,將輸入FIFO下移STRIDE行數(shù),然后重復(fù)該過程以生成輸入圖像中下一組線的卷積結(jié)果。當(dāng)輸入FIFO向下移動(dòng)時(shí),不再需要FIFO中的初始行,因此與MLP計(jì)算并行時(shí),將加載下一組用于輸入圖像的STRIDE行。考慮外部存儲(chǔ)源的帶寬要求時(shí),可以看到映像和內(nèi)核僅從內(nèi)存中讀取一次。然后,它們可以從各自的BRAM中重新使用,從而減少了外部存儲(chǔ)器帶寬的總體負(fù)擔(dān),其過程參考圖表1。

數(shù)據(jù)流:多個(gè)MLP

MLP的一個(gè)顯著特點(diǎn)是能夠?qū)?shù)據(jù)和結(jié)果從一個(gè)MLP或BRAM級(jí)聯(lián)到同一列中。 MLP_Conv2D通過將MLP及其關(guān)聯(lián)的BRAM放在列組中來利用這些級(jí)聯(lián)路徑。在將BRAM加載到內(nèi)核時(shí),級(jí)聯(lián)路徑用于將數(shù)據(jù)流水線傳輸?shù)矫總€(gè)BRAM,并且使用BRAM塊地址模式選擇要寫入內(nèi)核的BRAM。

在計(jì)算過程中,輸入的圖像數(shù)據(jù)將在MLP的列中級(jí)聯(lián),以便每個(gè)MLP在其下一個(gè)鄰居之后的一個(gè)周期接收到圖像數(shù)據(jù)。同時(shí),控制內(nèi)核讀取的BRAM讀取地址以一個(gè)周期的延遲級(jí)聯(lián)到BRAM列中。這樣,每個(gè)MLP在其先前的MLP之后一個(gè)周期接收相同的圖像數(shù)據(jù)和相同的內(nèi)核讀取地址。每個(gè)MLP的計(jì)算差異在于,其關(guān)聯(lián)的BRAM將具有不同的內(nèi)核數(shù)據(jù)。結(jié)果是一個(gè)圖像并行地與多個(gè)內(nèi)核卷積。并行卷積的數(shù)量稱為BATCH。

數(shù)據(jù)流:計(jì)算結(jié)果

如前所述,每個(gè)MLP為內(nèi)核和圖像部分的每個(gè)卷積生成16位結(jié)果。

MLP排列在16列中,因此從該列中生成一個(gè)256位字,該字由該列中每個(gè)MLP的結(jié)果組成。然后將此256位字寫入輸出NAP。 這種安排導(dǎo)致卷積結(jié)果作為同一圖像的圖層存儲(chǔ)在內(nèi)存中;因此,當(dāng)三層或RGB存儲(chǔ)在單個(gè)輸入字中時(shí),匹配輸入字排列。

然后,由于可以在完整的256位結(jié)果上的16個(gè)并行實(shí)例中執(zhí)行激活功能,因此該安排允許將涉及的結(jié)果并行處理到激活層中。同樣,一旦256位結(jié)果通過輸出NAP寫回到存儲(chǔ)器中,則可以將結(jié)果讀回到另一個(gè)2D卷積電路中。

圖表 5 MLP_Conv2D布局示意圖

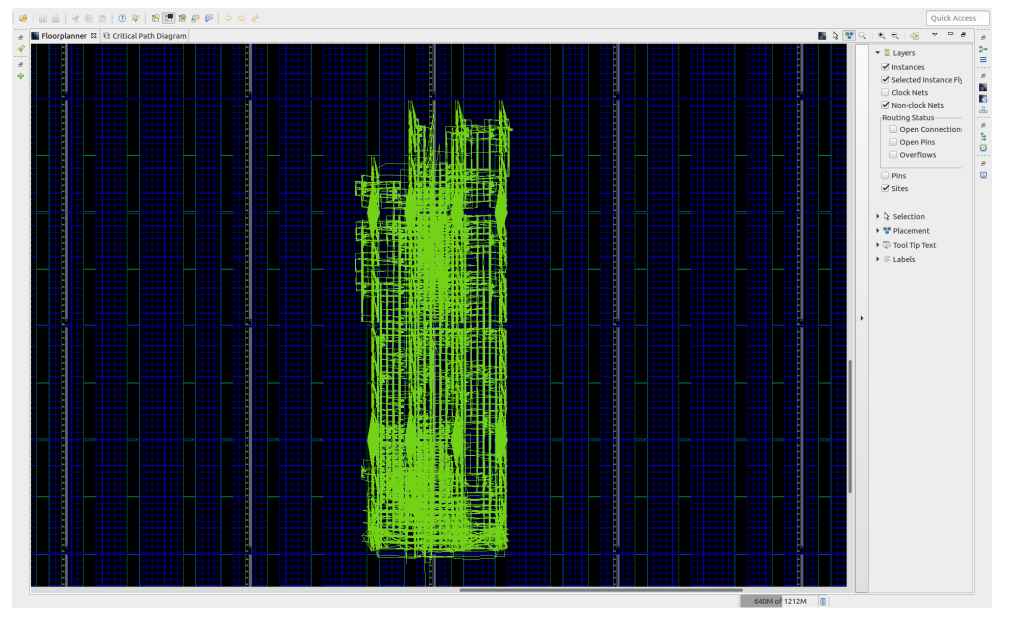

布局

在Speedster7t架構(gòu)中,每個(gè)NAP對(duì)應(yīng)32個(gè)MLP。該設(shè)計(jì)經(jīng)過優(yōu)化,可使用兩個(gè)NAP,一個(gè)用于讀取,一個(gè)用于寫入,因此可以對(duì)應(yīng)64個(gè)MLP。

但是,輸入和輸出FIFO需要兩個(gè)BRAM 72K存儲(chǔ)塊才能創(chuàng)建一個(gè)256位寬的組合存儲(chǔ)器。因此,這些存儲(chǔ)器將消耗64個(gè)可用位置中的四個(gè)用于數(shù)據(jù)I / O。

設(shè)計(jì)被安排為使用與兩個(gè)NAP相關(guān)聯(lián)的四列MLP。但是,第一列和最后一列都使用14個(gè)MLP,剩下兩個(gè)MLP位置分別用于輸入和輸出FIFO。中間兩列使用所有16個(gè)可用的MLP。在平面圖中,各列的排列方式是使第一列(底部具有輸入FIFO存儲(chǔ)器)與NAP相鄰,以改善時(shí)序。

下面顯示了一個(gè)實(shí)例,即使用了60個(gè)MLP(Batch=60)的設(shè)計(jì)實(shí)際布局圖(突出顯示了路線):

圖表 6 60個(gè)MLP布局圖

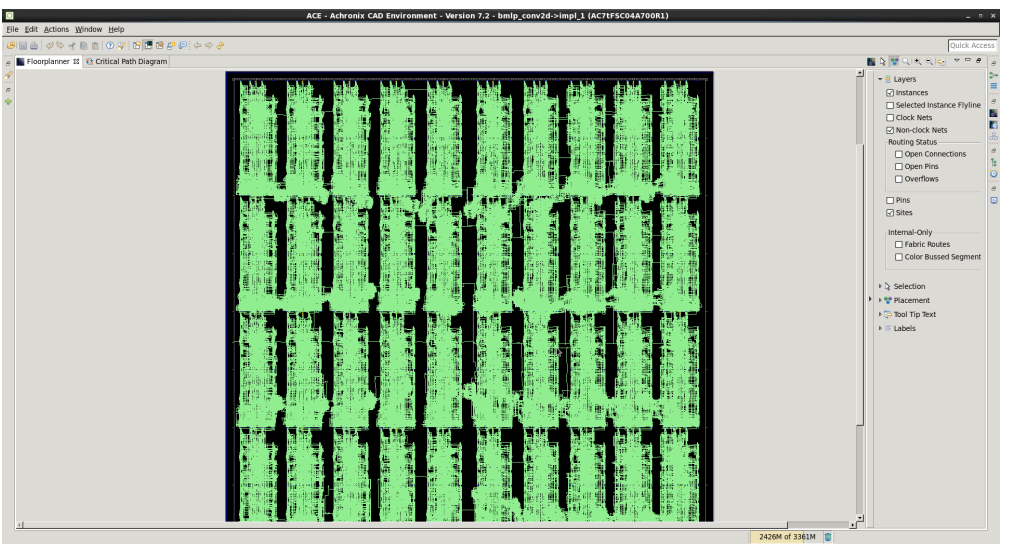

在全芯片構(gòu)建中使用40個(gè)實(shí)例時(shí),盡力使每個(gè)實(shí)例都使用NAP與內(nèi)存進(jìn)行通信。結(jié)果,F(xiàn)Max仍能達(dá)到750MHz,并使用掉芯片中的所有80個(gè)NAP以及94%的MLP和BRAM72K。

圖表 7 2400個(gè)MLP布局圖

下一期將舉例介紹MLP的浮點(diǎn)架構(gòu)和性能,敬請(qǐng)期待。