用硅IGBT的工程師們很多曾經(jīng)有過并聯(lián)器件的使用經(jīng)歷,它不僅能降低成本還能減小整體系統(tǒng)分布電感。那么對(duì)于新一代的半導(dǎo)體器件SiC而言,是否一樣可以并聯(lián)使用呢?以下就以4個(gè)英飛凌6mohm的SiC模塊的硬并聯(lián)為例,來一起看看實(shí)現(xiàn)的可行性。

任何的同一料號(hào)開關(guān)器件并聯(lián),均流總是最重要的目的,這關(guān)系到整個(gè)系統(tǒng)的最終功率等級(jí),所以如何做到均流就會(huì)是一個(gè)挑戰(zhàn)。一般我們會(huì)按動(dòng)態(tài)均流和靜態(tài)均流分別討論它。動(dòng)態(tài)均流和系統(tǒng)設(shè)計(jì)有很大的關(guān)系,包括門極驅(qū)動(dòng),母排結(jié)構(gòu),PCB布線,甚至功率器件和負(fù)載擺放的位置都會(huì)影響均流效果。而靜態(tài)均流和器件本身以及結(jié)構(gòu)的幾何形態(tài)關(guān)系密切,得益于如今市場(chǎng)上大部分的功率半導(dǎo)體是正溫度系數(shù)的,所以靜態(tài)均流比較容易實(shí)現(xiàn),對(duì)器件批次的參數(shù)差異要求不多,文章最后會(huì)給出蒙特卡洛分析來評(píng)估。

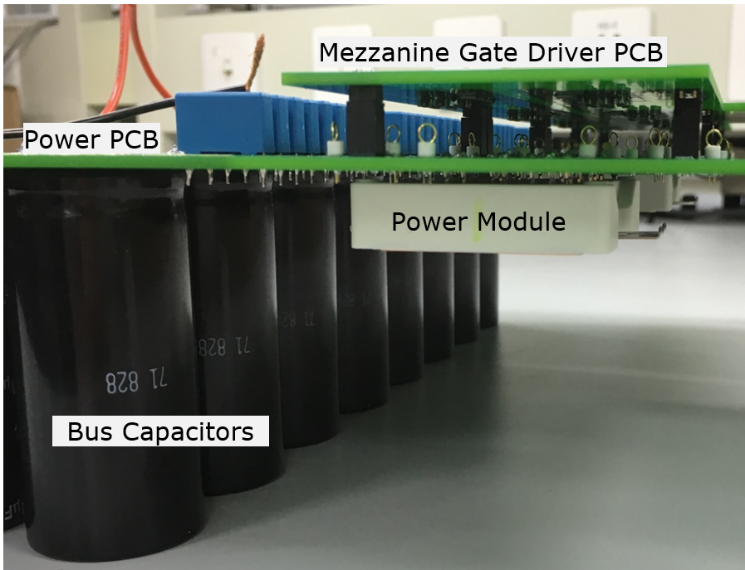

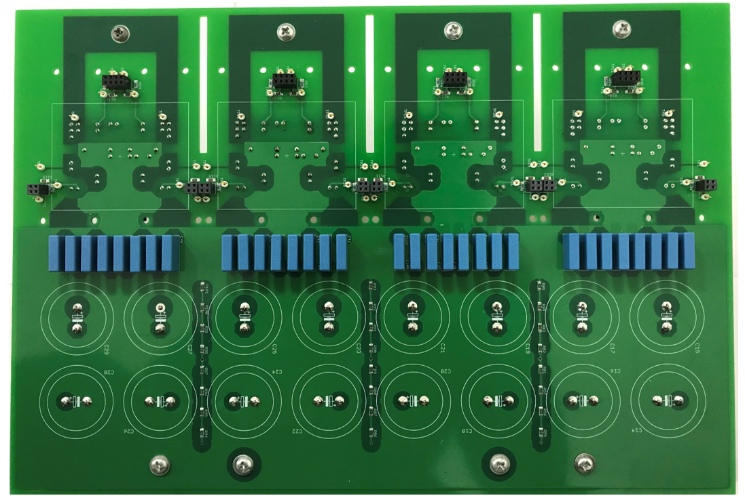

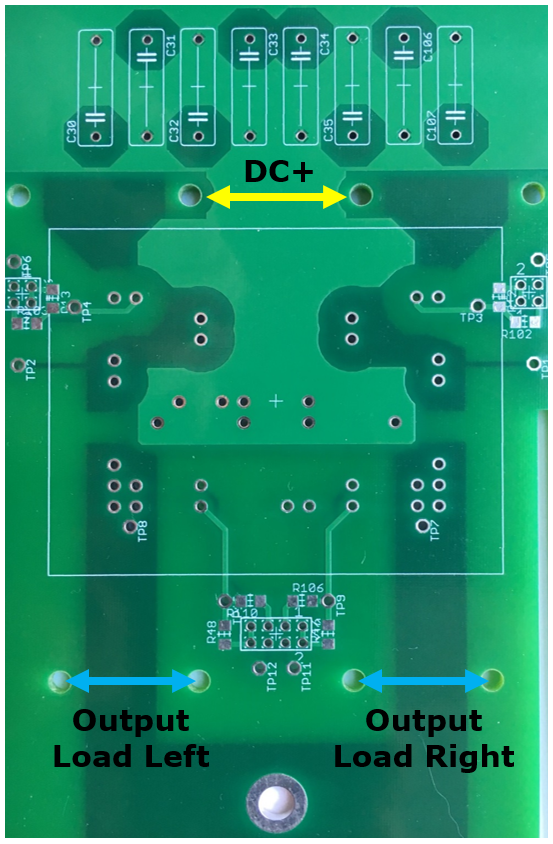

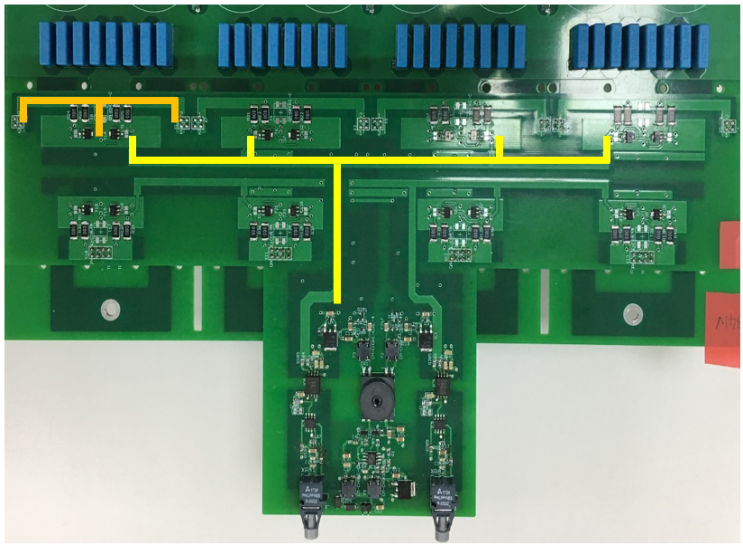

首先我們來討論一下整體結(jié)構(gòu)。由于要實(shí)現(xiàn)最小的電流回路,整個(gè)系統(tǒng)做成了分開的主功率板和驅(qū)動(dòng)電路板,用接插針來連結(jié)兩塊板子,如圖1所示。這樣的好處是4路驅(qū)動(dòng)到4個(gè)并聯(lián)模塊的距離相等。再來看一下主功率板的布局如圖2。用多層PCB來實(shí)現(xiàn)多層母線的結(jié)構(gòu),這樣的雜散電感很小,每路只有大約19nH,4個(gè)并聯(lián)后總的雜散電感不超過5nH。可以看到整個(gè)主功率板超級(jí)對(duì)稱,這對(duì)并聯(lián)應(yīng)用是最重要的,沒有之一。如果看不清楚,沒關(guān)系,請(qǐng)參考圖3單路的高清放大圖,上排的孔是用來套超細(xì)柔性探頭測(cè)橋臂電流;下排的孔是留來測(cè)負(fù)載電流的。這些孔在實(shí)驗(yàn)階段很好用,當(dāng)然在正式的設(shè)備量產(chǎn)板上是要去掉的,去掉后母排疊層區(qū)域面積變大,系統(tǒng)的雜散電感會(huì)進(jìn)一步減小的。

圖1 雙層結(jié)構(gòu)的電路設(shè)計(jì)

圖2 主功率板的布局

圖3 單個(gè)主回路

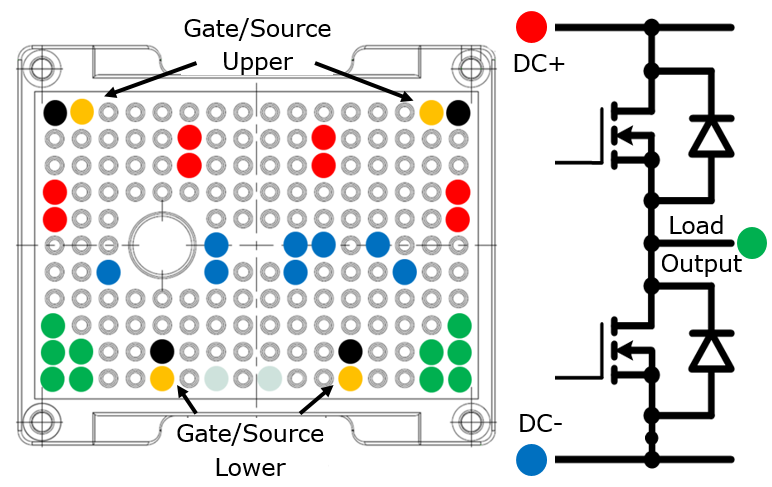

我們?cè)賮砜匆幌逻@個(gè)4并聯(lián)的驅(qū)動(dòng)。圖4是這個(gè)模塊的管腳布局圖,這個(gè)模塊的上下橋模塊每個(gè)都擁有兩路gate,兩路source,且他們?cè)谀K內(nèi)部是電氣相連的。這樣做不僅可以減小門極的寄生電感,還能改善模塊內(nèi)部SiC芯片的電流分布。鑒于這樣的模塊門極結(jié)構(gòu),外圍的驅(qū)動(dòng)電路也應(yīng)做到與之相配,也就是說接到兩個(gè)G、S也要對(duì)稱,以保證左右兩邊的開關(guān)時(shí)間高度一直。可以用圖5這樣的樹形結(jié)構(gòu),橘黃色是到左右兩邊的驅(qū)動(dòng)信號(hào),黃色是驅(qū)動(dòng)板至4路SiC模塊的驅(qū)動(dòng)信號(hào)。經(jīng)實(shí)測(cè),4并聯(lián)8組驅(qū)動(dòng)信號(hào)之間的延時(shí)誤差不超過5ns。

圖4 模塊管腳布局

圖5 門極驅(qū)動(dòng)的樹形結(jié)構(gòu)

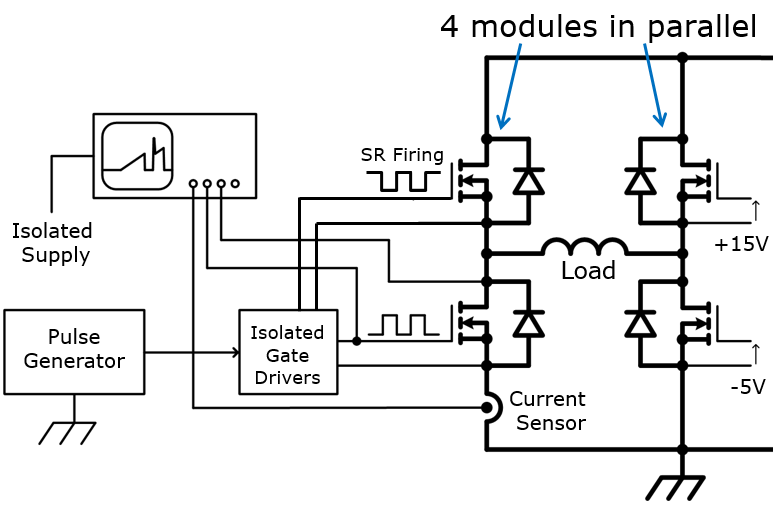

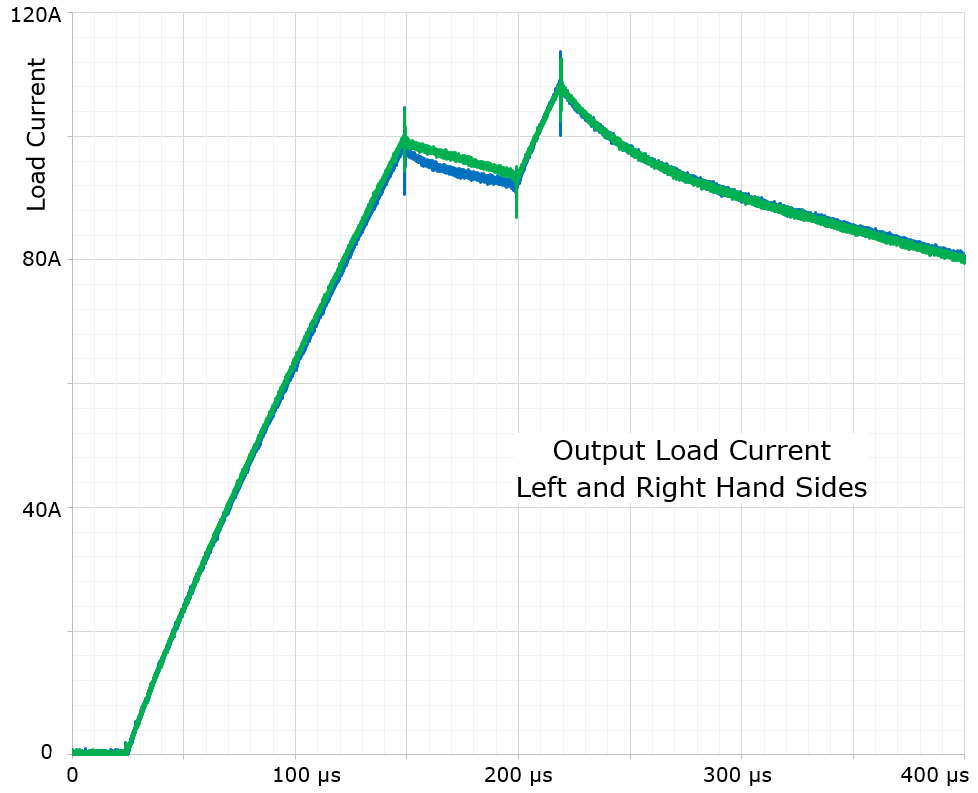

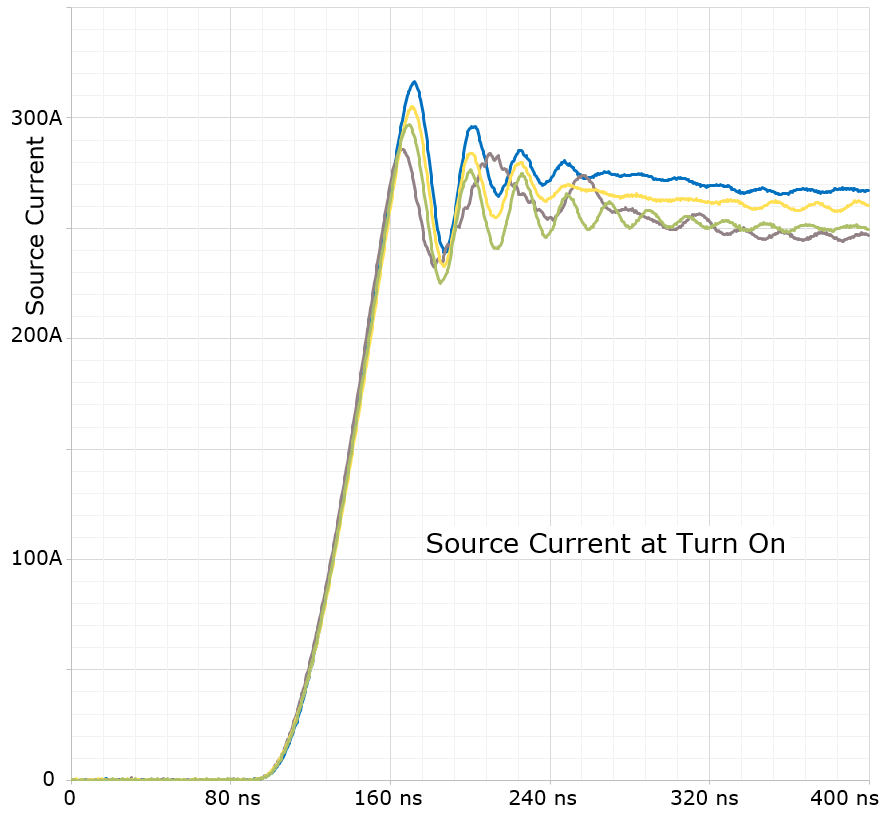

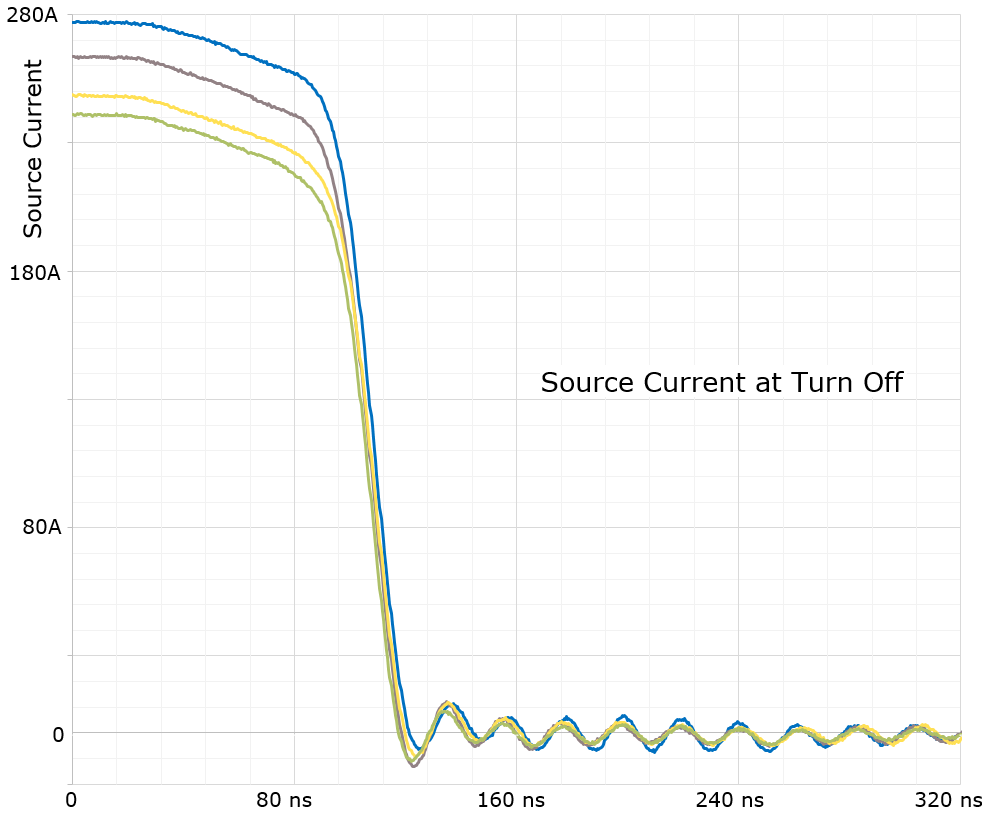

這么對(duì)稱的母排和驅(qū)動(dòng),實(shí)際測(cè)量中均流到底好不好呢?接下來,讓我們一起見證一下結(jié)果。需要說明的是測(cè)試所用的雙脈沖測(cè)試電路結(jié)構(gòu)是全橋的,并非常規(guī)用的半橋模式,原理如圖6。如此做的好處是可以減小半橋測(cè)試時(shí)負(fù)載電感對(duì)回路的電磁場(chǎng)影響。各個(gè)器件的門極信號(hào)給定也在圖中有顯示。由于SiC器件的體二極管導(dǎo)通壓降大且偏差也大,所以在續(xù)流是可以使用同步整流模式,但要留出一定的死區(qū)時(shí)間,對(duì)SiC器件而言一般不超過1us。圖7是單個(gè)模塊左右兩側(cè)的負(fù)載電流,可以看出兩者的均流度非常好。我們不僅要對(duì)每個(gè)模塊的左右電流均流度進(jìn)行確認(rèn),還要對(duì)不同模塊同一側(cè)電流進(jìn)行比較,這樣能保證器件并聯(lián)后達(dá)到最大的輸出電流。圖8和圖9分別是4個(gè)并聯(lián)模塊的開通和關(guān)斷電流,上升和下降的斜率一致性非常高,而且沒有什么振蕩。改變溫度,母線電壓和門極電阻后,均流的趨勢(shì)幾乎是一樣的。

圖6 全橋雙脈沖測(cè)試

圖7 單個(gè)模塊左右兩側(cè)的負(fù)載電流

圖8 開通電流

圖9 關(guān)斷電流

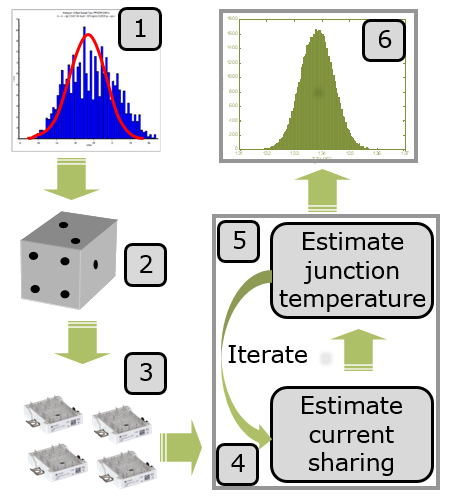

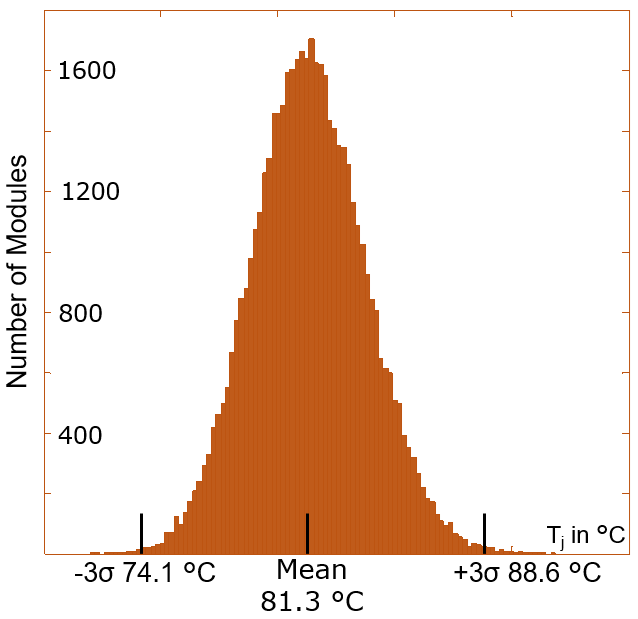

以上的這些測(cè)試結(jié)果都是針對(duì)數(shù)量有限的模塊的,那么對(duì)于批量的產(chǎn)品而言,均流又怎樣呢?最后,祭出了蒙特卡洛來進(jìn)行熱分析。這個(gè)理論簡(jiǎn)單地說就是反復(fù)地隨機(jī)取樣,以得到最終事件概率。圖10所示,用在本次模塊并聯(lián)分析中就是從一個(gè)50000個(gè)不同損耗的樣本庫中,隨機(jī)抽出4個(gè)進(jìn)行組合,然后進(jìn)行電流與溫度的迭代,獲得該組并聯(lián)時(shí)的溫度差。多次重復(fù)進(jìn)行這樣的隨機(jī)抽取,把所有的溫度差按出現(xiàn)的次數(shù)繪成柱狀圖就是圖11。

圖10 蒙特卡洛過程

圖11 并聯(lián)溫度偏差

結(jié)束語

SiC器件的并聯(lián)肯定是可行的,但最最關(guān)鍵的一個(gè)詞就是“對(duì)稱”。“對(duì)稱”能從根本上解決各類振蕩和不均流問題。另外,使用同步整流還有助于續(xù)流時(shí)的均流,特別對(duì)二極管損耗占比偏高的應(yīng)用大益。

參考資料:

Infineon AN 2017-41. Evaluation Board for CoolSiC? Easy1B half-bridge modules.

Infineon AN 2017-04. Advanced Gate Drive Options for Silicon- Carbide (SiC) MOSFETs using EiceDRIVER?.

Infineon AN2014-12. EiceDRIVER? 1EDI Compact Family. Technical description.

Infineon AN2018-09. Guidelines for CoolSiC? MOSFET gate drive voltage window

Infineon AN2017-14. Evaluation Board EVAL-1EDI20H12AH-SIC.

Infineon AN2007-04. How to calculate and minimize the dead time requirement for IGBT’s properly.

Infineon AN2017-46. CoolSiC? 1200 V SiC MOSFET Application Note