使用網(wǎng)絡(luò)處理器來設(shè)計(jì)通信系統(tǒng),所設(shè)計(jì)的系統(tǒng)結(jié)構(gòu),和設(shè)計(jì)時所采用的設(shè)計(jì)方法,與傳統(tǒng)的方法相比都很不相同。影響最大的是設(shè)計(jì)工作的重點(diǎn),設(shè)計(jì)人員的注意力將從硬件線路和通信協(xié)議的細(xì)節(jié)的考慮中,轉(zhuǎn)向軟件、服務(wù)以及最終用戶的技術(shù)要求方面。也就是說,設(shè)計(jì)將是以軟件為中心,以通信服務(wù)為中心,和以最終用戶的技術(shù)要求為注意的集中點(diǎn)。設(shè)計(jì)公司將一改過去集中注意于硬件設(shè)計(jì)的傳統(tǒng),轉(zhuǎn)而將注意力集中于用戶所需要的服務(wù)方面,并考慮如何使用軟件來實(shí)現(xiàn)用戶所需要的服務(wù)。

這些變化與進(jìn)展在相當(dāng)大程度上應(yīng)該歸功于網(wǎng)絡(luò)處理單元(NPU, network processing unit)的推動。在這種情況下,系統(tǒng)設(shè)計(jì)人員如果對于網(wǎng)絡(luò)處理器能夠運(yùn)用自如,那么就可以充分了解網(wǎng)絡(luò)處理器的作用,并且能夠感覺到,與使用網(wǎng)絡(luò)處理器隨之而來的潛在自由空間。系統(tǒng)設(shè)計(jì)人員也才有可能最大限度地發(fā)揮網(wǎng)絡(luò)處理器的潛能。

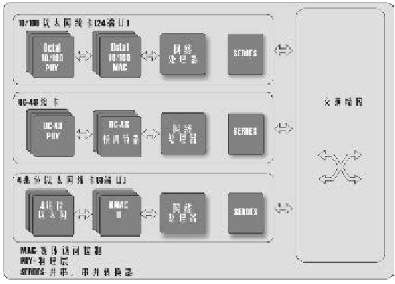

附圖是系統(tǒng)原理圖,它顯示出網(wǎng)絡(luò)處理器在系統(tǒng)設(shè)計(jì)中所處的重要位置。NPU 一般位于物理層(MAC 或幀調(diào)節(jié)器)線路和交換結(jié)構(gòu)之間。在圖中并串行 / 串并行轉(zhuǎn)換器(SERDES)在 NPU 和交換結(jié)構(gòu)造之間起接口作用。

NPU 的運(yùn)行速度有待提高

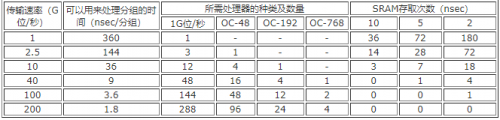

表 1 給出了在不同的數(shù)據(jù)傳輸速率條件下,網(wǎng)絡(luò)處理器處理一個 40 字節(jié)的分組(最小的通信分組)所需要的時間。例如,在數(shù)據(jù)傳輸速率為 1G 位 / 秒時,網(wǎng)絡(luò)處理器可以有 360 ns 的時間來處理此分組。在這段時間內(nèi),NPU 必須對分組進(jìn)行檢查,語法分析,以及必要的編輯和查表(有時對于分組的內(nèi)容需要按照不同的策略采取不同的處理措施,有的繼續(xù)向前傳送,有的要送去排隊(duì),有的需要作標(biāo)記;一般說來,對于一個分組可能要進(jìn)行 2 到 3 種數(shù)據(jù)庫的查表處理)。對于即使是比較低的傳輸速率 1G 位 / 秒,網(wǎng)絡(luò)處理器也只有 360 ns 來完成上述作業(yè);如果傳輸速率為 100G 位 / 秒,對于每個分組就只有 3.6 ns 的時間來進(jìn)行處理了。

從目前情況來看,價格適中的 SRAM,存取時間為 10 nsec,有望提高到 5 nsec。如果將一個 10 nsec 的 SRAM 用于 1G/ 秒的數(shù)據(jù)流,在留給處理分組的 360 nsec 時間窗口內(nèi),只能對存儲器進(jìn)行 36 次的存取。如果用于 10 G 位 / 秒的數(shù)據(jù)流,存取次數(shù)將減少到只能進(jìn)行 3 次了;即使是采用 5 nsec 的 SRAM,也只能進(jìn)行 7 次存取。

從表 1 所給出的數(shù)據(jù)可以看出,為了有效地提高數(shù)據(jù)處理速率,只能將處理步驟分段,并采用流水線的方式來進(jìn)行處理,或者采用多個處理機(jī)來并行處理(即多個處理機(jī)同時對不同分組進(jìn)行處理)。這種解決辦法,對于策略查表存儲器,和內(nèi)容尋址存儲器(CAM)都適用。例如,對于 40 G 位 / 秒的數(shù)據(jù)流,采用 10 nsec 的存儲器,在允許的時間內(nèi)一次存取也進(jìn)行不了。這時,設(shè)計(jì)人員必須采用許多并行的存儲器陳列。

網(wǎng)絡(luò)處理器可以按照它們對于數(shù)據(jù)處理的速率來進(jìn)行分類。在表 1 的中間部分列出了對于一定的數(shù)據(jù)速率,需要采用的網(wǎng)絡(luò)處理器種類和數(shù)量。例如,對于 2.5 G 位 / 秒的數(shù)據(jù)流,需要使用 3 個 1G 位 / 秒的處理器來進(jìn)行處理。而對于 100 G 位 / 秒的數(shù)據(jù)流,則需要 144 個這樣的處理器。對于這樣的數(shù)據(jù)流,也許改為采用 12 個 OC-192 處理器,或兩個 OC-768 處理器更合適一些。

表 1 對網(wǎng)絡(luò)處理器處理速率的要求(以每分組 40 字節(jié)為例)

網(wǎng)絡(luò)處理單元的作用及如何實(shí)現(xiàn)通信系統(tǒng)的設(shè)計(jì)

除了實(shí)際處理分組需要時間以外,將分組從網(wǎng)絡(luò)一方轉(zhuǎn)移進(jìn)來,和將數(shù)據(jù)轉(zhuǎn)移到交換結(jié)構(gòu)一方去也去要花費(fèi)時間。表 2 給出的分?jǐn)倳r間是總時間的 25%。以上數(shù)字對于 MAC 接口是很符合實(shí)際的假設(shè),但是對于交換結(jié)構(gòu)接口,由于分段(segmentation)的效率一般只有 50%,因此在計(jì)算時需要留下 100%的速度余度,才能跟得上通信線路的速度。

表 2 對于網(wǎng)絡(luò)媒體 / 交換結(jié)構(gòu)接口的要求

從表 2 可以看出,對于 10G 位 / 秒的傳輸速率,如果采用 32 位單數(shù)據(jù)速率(SDR)總線,則總線必須工作在 391MHz。而對于 40G 位 / 秒的傳輸速率,假定采用 64 位 SDR 總線,總線必須工作在 781MHz。表 3 總結(jié)了對分組緩沖存儲器的要求。分組緩沖存儲器至少必須具有 3 倍用通信線路的速度的傳輸速率(300%的速度余度)。表 3 中分門別類地給出了這一要求。例如,對于 10G 位 / 秒的傳輸速率,如果采用的是 64 位的雙倍數(shù)據(jù)速率(DDR)緩沖存儲器,則需要工作在 313MHz 以上的頻率。

表 3 對分組緩沖存儲器的要求

網(wǎng)絡(luò)處理單元(NPU)的結(jié)構(gòu)問題

網(wǎng)絡(luò)處理器和中央處理單元(CPU)不同。網(wǎng)絡(luò)處理器需要對它所需要進(jìn)行處理自行抽象提取。它必須能夠識別字段(field),分組(packet),和數(shù)據(jù)流(flow)。它必須對于它所需要進(jìn)行的處理功能,例如:語法分析,編輯,搜尋,和調(diào)度等,具有特殊的運(yùn)算能力。

在程序編制模型方面,網(wǎng)絡(luò)處理器和 CPU 并沒有根本的不同:它也是一個可以儲存程序的微編碼機(jī)。但是在數(shù)據(jù)的模型方面則有很大的區(qū)別。NPU 處理的是一種恒定的連續(xù)數(shù)據(jù)流(一種數(shù)據(jù)流結(jié)構(gòu)),因此不需要將數(shù)據(jù)從一個大容量存儲器中移進(jìn)移出。如上所述,網(wǎng)絡(luò)處理器為了滿足一定的數(shù)據(jù)速率,絕對地需要并行處理,或流水線(pipelined)結(jié)構(gòu),或者兩種方式同時都需要采用。

另一個問題是網(wǎng)絡(luò)處理器的可編程性能。一個極端是使它具有最大的可編程性,因而使它具有最大的靈活性,也可以在最大程度上適應(yīng)未來的發(fā)展變化(即使它可以通過新開發(fā)的軟件使系統(tǒng)改變或升級,而不是當(dāng)要求改變系統(tǒng)時就更新硬件)。這種方式的缺點(diǎn)是,為了完成一項(xiàng)作業(yè)需要執(zhí)行許多個指令,因而可能導(dǎo)致缺乏凈空(headroom)。

另一種折衷方式,稱為“適當(dāng)程度的可編程性”。這種方式提供一定程度的可編程性以適應(yīng)變化的需要,或者說使處理器具有一定的靈活性。但是它不能適應(yīng)完全的重新編程的需要。和 RISC 型的 CPU 類似(RISC 采用簡約的有效指令集,以提高 CPU 速度);而 NPU 則通過提供適當(dāng)?shù)目删幊绦裕沟孟到y(tǒng)設(shè)計(jì)人員能夠犧牲某些靈活性,去提高運(yùn)行速度,換取更多的性能凈空。

對于運(yùn)行在載體網(wǎng)絡(luò)核心的交換機(jī)和路由器,速度的要求高于一切。這些在網(wǎng)際間工作的裝置,不需要進(jìn)行復(fù)雜的分組處理功能,只是要求將分組以最大的線速度向前傳送。與此相反,在企業(yè)網(wǎng)的邊沿,線速度明顯地比較低,而交換機(jī)對分組的處理能力卻要求相當(dāng)?shù)母摺@纾瑢τ诙鄥f(xié)議標(biāo)記交換機(jī),它處于網(wǎng)絡(luò)的邊沿,需要對某些數(shù)據(jù)流進(jìn)行識別并相應(yīng)地對某些分組予以標(biāo)記。

交換機(jī)的設(shè)計(jì)人員可以根據(jù)這些不同的要求,以及交換機(jī)所處的位置,為預(yù)計(jì)在企業(yè)網(wǎng)邊沿使用的交換機(jī)選擇可以充分編程的 NPU。而對于將應(yīng)用在網(wǎng)絡(luò)核心部位的交換機(jī),則應(yīng)該選擇編程能力有限,但是具有較高速度的 NPU。

網(wǎng)絡(luò)處理器的實(shí)現(xiàn)方式

網(wǎng)絡(luò)處理器的實(shí)現(xiàn)方式大體上可以分為三種。一種是采用專用的 ASIC 或 FPGA(后者往往功能不夠完整,或者性能不夠理想)。這種方式就是依靠“硬件”的方式,它具有最高的性能,但是靈活性也最差(因?yàn)樵O(shè)計(jì)決策是熔制在硅的體內(nèi))。此外,ASIC 的開發(fā)過程比較長,一次性的、不可重復(fù)使用的投入的費(fèi)用也比較高。

另一種方式是將許多個 RISC CPU 做在一塊芯片上,采用對稱多重處理的運(yùn)行方式(使用微編碼將通用 CPU 轉(zhuǎn)變成為專用的網(wǎng)絡(luò)處理器)。這種實(shí)現(xiàn)方式,由于 NPU 的一切行為幾乎都是通過軟件實(shí)現(xiàn)的,因此靈活性最高。這種方式所需要的開發(fā)時間比較短,它展現(xiàn)在設(shè)計(jì)人員面前的形象是設(shè)計(jì)人員十分熟悉的編程模型。然而,隨著軟件復(fù)雜性的增加,這種方式的費(fèi)用也在增長。由于嚴(yán)重地依賴軟件,這種方式實(shí)現(xiàn)的系統(tǒng),與采用專用 ASIC 實(shí)現(xiàn)的系統(tǒng)相比性能較差,所消耗的功率也較多。

介乎上述二者之間的一種實(shí)現(xiàn)方式是流水線方式,它采用一些具有不同功能的專用處理器,組成“裝配線”型式的數(shù)據(jù)流構(gòu)造。采用流水線方式實(shí)現(xiàn)的系統(tǒng),性能接近用 ASIC 實(shí)現(xiàn)的系統(tǒng),而在編程的靈活性方面又和多處理器實(shí)現(xiàn)的系統(tǒng)相差不多。

衡量 NPU 技術(shù)水平的尺度

設(shè)計(jì)人員十分關(guān)心的一個問題是技術(shù)水平。衡量技術(shù)水平,可以從幾個不同的層次加以分析。

* 在芯片層次,人們關(guān)心的問題是:在一個芯片上究竟可以容納多大的處理能力?根據(jù)當(dāng)前的技術(shù)水準(zhǔn),在一個芯片上可以做成 10G 位 / 秒的 NPU。

* 在線路卡(line-card)層次,問題在于:一張線路卡可以安置多少塊芯片?同樣重要的是:使用一個小型交換結(jié)構(gòu)或一個共用的總線,究竟可以將多少塊芯片放在一個線路卡上,正常地并行運(yùn)行?現(xiàn)在看來,可以在一張卡上安置足夠的處理能力,使之達(dá)到 100G 位 / 秒的傳輸要求。

* 在機(jī)架或機(jī)箱層次,問題在于,一個機(jī)架或機(jī)箱,通過一個交換結(jié)構(gòu)可以容納多少張線路卡進(jìn)行信息傳遞?現(xiàn)在看來一個機(jī)架實(shí)現(xiàn)數(shù)太拉(1012)位的傳輸能力是可能的。

* 在機(jī)房層次,問題在于,究竟多大規(guī)模的機(jī)架簇群可以連接在一起仍然能夠進(jìn)行有效的通信?目前在這個層次上,還沒有把握說清楚,但是一些新建的機(jī)房已經(jīng)把目標(biāo)瞄準(zhǔn)在數(shù)拍它(1015)帶寬的水平。

評價一個 NPU 不能只看單個 NPU 的工作能力,還要看它的互操作性。一個 10G 位 / 秒的 NPU,并不一定比一個 9G 位 / 秒的 NPU 優(yōu)越。它還決定于互操作性:如果 9G 位 / 秒的 NPU,能夠十分容易地和其它的 NPU 連接在一起,實(shí)現(xiàn)更強(qiáng)得多的交換能力,那么選用它,不失為明智的選擇。

設(shè)計(jì)人員如何才能發(fā)揮多處理器的優(yōu)勢?不論是并行結(jié)構(gòu)或者是串行結(jié)構(gòu),都可以采用;也可以采用混合結(jié)構(gòu),即串 - 并排列的結(jié)構(gòu)。重要的問題在于需要考慮:負(fù)荷的平衡(注意不使任何一個 NPU 超載);作業(yè)的劃分;保持分組流的順序不亂;維持服務(wù)質(zhì)量;以及對 NPU 之間通信業(yè)務(wù)量的控制。

衡量 NPU 性能的指標(biāo)

如何正確地評估不同的 NPU?關(guān)鍵的指標(biāo)之一是:處理分組的速度(即每秒處理多少百萬個分組或稱為 Mpps)。另一個指標(biāo)是:在一定的分組傳遞速率下,處理每個分組時,允許進(jìn)行的查表次數(shù)(一般每處理一個分組允許進(jìn)行 2 次查表)。當(dāng)然在進(jìn)行處理時可以利用的存儲器的規(guī)模也是一項(xiàng)重要指標(biāo)。此外,及時不斷的提高速度也是十分重要的。許多處理策略也需要進(jìn)行周期性的更新。有些 NPU 具有能以很高的速度向前傳送的性能,但是更新處理策略,或更改某些參數(shù)時,卻需要耗用數(shù)毫秒,甚至數(shù)秒的時間才能完成。比較理想的 NPU,更新策略,更改參數(shù)的時間最好在數(shù)微秒的時間范圍內(nèi);這一點(diǎn)對于用在路由頻繁跳變的場合特別重要。

“凈空”也是需要的。凈空可以看作是在保持線傳送速度不降低的情況下,可能增加的處理功能(或可能增加的處理復(fù)雜問題的能力);處理復(fù)雜問題的能力(即在一個時鐘周期內(nèi),用一個指令,包括轉(zhuǎn)移這樣的控制指令,可以完成多少處理功能)是另一重要的事項(xiàng)。

設(shè)計(jì)人員應(yīng)該考慮的其它問題還有:等待時間,排隊(duì)和調(diào)度的效率,分組存儲(以及分段)的效率,在硅體內(nèi)多重熔制的效率,芯片的大小,以及這些問題對于總體系統(tǒng)的影響(包括對于消耗功率和成本的影響)等等。

發(fā)展趨勢

隨著設(shè)計(jì)人員逐漸習(xí)慣于使用 NPU 進(jìn)行系統(tǒng)設(shè)計(jì),幾種時尚可能會流行。下面列出今后幾年將會出現(xiàn)的趨向。

* 今日的系統(tǒng)設(shè)計(jì)越來越趨向于從眾多的制造商那里采購 ASIC 和 IC。這些芯片中有許多都是各廠商自家獨(dú)有的產(chǎn)品,與它們相關(guān)聯(lián)的軟件也都是各廠商自行開發(fā)的。它們之間往往缺乏互操作性。預(yù)計(jì)今后幾年設(shè)計(jì)人員會越來越對商品化的 IC 感興趣,并且 NPU 的發(fā)展毫無疑問將會進(jìn)一步助長這種傾向的發(fā)展。在硬件方面的發(fā)展趨勢是越來越多地采用現(xiàn)成的商品 IC,軟件也在朝這個方向發(fā)展,例如一些專門的協(xié)議棧開發(fā)商正在提供越來越多的商品軟件部件。以這些 ASIC 和 IC,以及商品軟件部件為基礎(chǔ)的增值服務(wù)業(yè)務(wù)也將會發(fā)展,并且可能成為交換機(jī)供應(yīng)商引以為榮的特點(diǎn)和具有真正競爭力的象征。

* 在市場范圍內(nèi),操作系統(tǒng)的供應(yīng)商將會趨向聯(lián)合和統(tǒng)一,設(shè)計(jì)人員采用標(biāo)準(zhǔn)操作系統(tǒng)的可能性會越來越大。

* 從長遠(yuǎn)看,可能會出現(xiàn)一系列標(biāo)準(zhǔn)的硬件平臺,例如標(biāo)準(zhǔn)的機(jī)架,標(biāo)準(zhǔn)的背板等。設(shè)計(jì)人員可能會從許多廠商中選擇一種線卡,買來插入標(biāo)準(zhǔn)機(jī)架。

* 在軟件方面,可能會出現(xiàn)一些標(biāo)準(zhǔn)的軟件集(操作系統(tǒng),協(xié)議軟件棧,管理控制軟件等)。系統(tǒng)設(shè)計(jì)人員將利用這些即插即用的部件組成系統(tǒng),并且增加一些可以提供不同服務(wù)內(nèi)容的線卡。

如果這些趨向成為現(xiàn)實(shí),標(biāo)準(zhǔn)接口問題將會成為十分重要的課題。例如,為了開發(fā)一種以太網(wǎng)的線卡,設(shè)計(jì)人員可能會選擇一種物理層(PHY)芯片、MAC 芯片、網(wǎng)絡(luò)處理器以及并串 / 串并轉(zhuǎn)換器等(參看附圖)來進(jìn)行設(shè)計(jì)開發(fā)。為了簡化設(shè)計(jì)業(yè)務(wù),縮短開發(fā)時間,這些芯片必須具有明確清晰的接口,應(yīng)該使設(shè)計(jì)人員不需要再花費(fèi)力氣提供連接的邏輯線路,就可以完成任務(wù)。

NPU 時代

網(wǎng)絡(luò)處理器將成為網(wǎng)絡(luò)中各個系統(tǒng)的重要組成部分,但是目前它還不很成熟。它們將在以下幾個方面取得重大進(jìn)步:在它們能夠處理的分組的復(fù)雜程度和所具有的智能方面;在可以下載的程序規(guī)模大小方面;隨著線速度的增加在每個時鐘周期內(nèi)能夠處理的一個分組或多個分組的綜合能力方面。

NPU 的性能正在按照統(tǒng)一的性能指標(biāo)穩(wěn)步提高。經(jīng)過一段時間以后,使用網(wǎng)絡(luò)處理器來設(shè)計(jì)開發(fā)通信系統(tǒng)的方法學(xué),估計(jì)將會和軟件的開發(fā)一樣,也會出現(xiàn)并取得發(fā)展進(jìn)步。