開源LIDAR原型制作平臺(tái)

2020-06-29

作者:ADI公司 - István Csomortáni,F(xiàn)PGA設(shè)計(jì)工程師;Dragos Bogdan,軟件開發(fā)工程經(jīng)理;Cristian Orian,系統(tǒng)設(shè)計(jì)工程師;Andrei Cozma,工程經(jīng)理

來源:ADI

摘要

本文探討ADI公司新推出且擁有廣泛市場(chǎng)的LIDAR原型制作平臺(tái),以及它如何通過提供完整的硬件和軟件解決方案,使得用戶能夠建立其算法和自定義硬件解決方案的原型,從而幫助客戶縮短產(chǎn)品開發(fā)時(shí)間;詳細(xì)介紹模塊化硬件設(shè)計(jì),包括光接收和發(fā)送信號(hào)鏈、FPGA接口,以及用于長(zhǎng)距離感測(cè)的光學(xué)器件;介紹系統(tǒng)分區(qū)決策,以凸顯良好的系統(tǒng)設(shè)計(jì)、接口定義和合適的模塊化分級(jí)的重要性;描述開源LIDAR軟件堆棧的組件和平臺(tái)定制的API,顯示客戶在產(chǎn)品開發(fā)期間如何受益,以及如何將這些產(chǎn)品集成到其最終的解決方案中。

簡(jiǎn)介

隨著自動(dòng)駕駛汽車和機(jī)器人從想象逐漸變?yōu)楝F(xiàn)實(shí),汽車和工業(yè)客戶開始尋求新的環(huán)境感知解決方案,力圖讓這些機(jī)器能夠自動(dòng)導(dǎo)航。LIDAR是該領(lǐng)域中發(fā)展最快的技術(shù)之一,隨著它越來越成熟和可靠,其應(yīng)用范圍也變得更加廣泛,帶來了巨大的市場(chǎng)機(jī)遇。許多初創(chuàng)企業(yè)和知名傳感器公司都致力于開發(fā)更加精準(zhǔn)、功耗低、尺寸小,且更加經(jīng)濟(jì)高效的LIDAR傳感器,但在設(shè)計(jì)系統(tǒng)硬件、實(shí)施軟件基礎(chǔ)設(shè)施以和系統(tǒng)中的所有組件通信時(shí),他們都遇到了同樣的挑戰(zhàn)。正是在這些區(qū)域,ADI能夠通過軟件參考設(shè)計(jì)和開源軟件堆棧提供價(jià)值,令客戶能夠輕松將ADI LIDAR產(chǎn)品系列、軟件模塊和HDL IP集成到其產(chǎn)品和IC中,從而縮短上市時(shí)間。

系統(tǒng)架構(gòu)

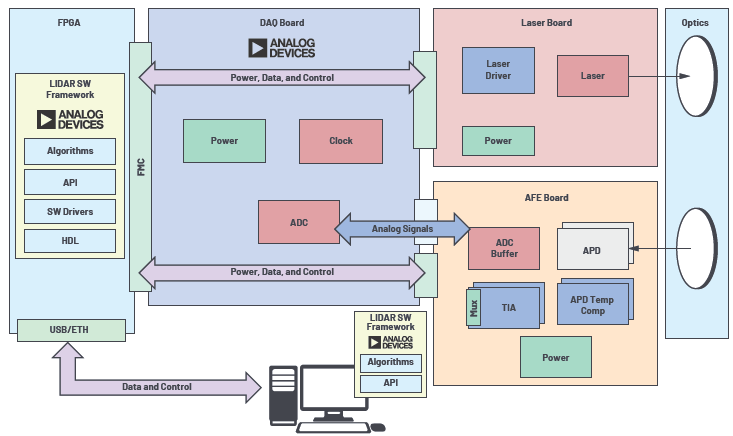

客戶在開發(fā)自己的LIDAR傳感器時(shí),系統(tǒng)設(shè)計(jì)中會(huì)存一些不同之處:接收和發(fā)送光學(xué)器件、激光器的數(shù)量和方向、激光發(fā)射模式、激光束控制,以及光接收元件的數(shù)量。但是,不管做出什么選擇,在接收信號(hào)鏈和激光器驅(qū)動(dòng)信號(hào)要求方面,所有傳感器都高度相似。基于這些假設(shè),ADI公司設(shè)計(jì)出模塊化LIDAR原型制作平臺(tái)AD-FMCLIDAR1-EBZ,以期讓客戶能夠使用他們自己的硬件輕松配置或更換器件;該平臺(tái)根據(jù)特定的應(yīng)用要求設(shè)計(jì),但仍可以用作整個(gè)系統(tǒng)。該系統(tǒng)可以分為三個(gè)不同的電路板,每個(gè)都配備標(biāo)準(zhǔn)化的數(shù)字和模擬接口:

? 數(shù)據(jù)采集(DAQ)電路板,包含高速JESD204B ADC、對(duì)應(yīng)的時(shí)鐘和電源。此電路板上有一個(gè)符合FMC要求的接口,可以連接至用戶首選的FPGA開發(fā)板。它充當(dāng)系統(tǒng)的基板,通過用于在這些板和FPGA之間路由控制和反饋信號(hào)的數(shù)字連接器,以及用于傳輸模擬信號(hào)的同軸電纜,將另外兩個(gè)板連接至這個(gè)板。

? 包含雪崩光電探測(cè)器(APD)的光傳感器和整個(gè)信號(hào)鏈的模擬前端(AFE)電路板,信號(hào)鏈用于調(diào)諧APD輸出信號(hào),以便能饋入DAQ板上的ADC。

? 包含激光器和驅(qū)動(dòng)電路的激光器板。

和以往一樣,在系統(tǒng)設(shè)計(jì)中,模塊化意味著靈活性,但它也有一些缺點(diǎn),比如復(fù)雜性增加、性能下降和成本增加,在決定系統(tǒng)分區(qū)時(shí)必須全面評(píng)估這些缺點(diǎn)。在這種情況下,系統(tǒng)被分成三個(gè)板,原因如下:

? 無論使用哪種模擬前端,選擇哪種激光器解決方案,ADC和時(shí)鐘很可能保持不變。

? 模擬前端硬件設(shè)計(jì)和尺寸根據(jù)所選的APD、整體的系統(tǒng)接收靈敏度,以及選擇的光學(xué)器件而變化。

? 激光器板設(shè)計(jì)和尺寸根據(jù)所選的照明解決方案和光學(xué)器件而變化。

? 對(duì)于接收器和發(fā)射器的位置和方向,系統(tǒng)提供很大的靈活性,以便它們彼此對(duì)應(yīng)或和其他目標(biāo)對(duì)應(yīng),因此使用柔性電纜來傳輸數(shù)字信號(hào),使用同軸電纜來傳輸兩個(gè)電路板之間的模擬信號(hào)。

圖1.LIDAR平臺(tái)系統(tǒng)設(shè)計(jì)。

圖2.產(chǎn)品開發(fā)周期。

包含硬件設(shè)計(jì)的軟件堆棧以分層方法為基礎(chǔ),以少數(shù)幾個(gè)層級(jí)區(qū)分為適用于特定操作系統(tǒng)的驅(qū)動(dòng)和接口、系統(tǒng)特定的API和應(yīng)用層。這使得堆棧的上層可以保持不變,無論軟件是在嵌入式目標(biāo)上運(yùn)行,還是在通過網(wǎng)絡(luò)或USB連接與系統(tǒng)通信的PC上運(yùn)行。如圖2所示,在不同的產(chǎn)品開發(fā)階段,這一點(diǎn)非常有用,因?yàn)檫@意味著將系統(tǒng)連接至PC以簡(jiǎn)化開發(fā)時(shí),在原型制作期間開發(fā)的同樣的應(yīng)用軟件可輕松部署到嵌入式系統(tǒng)中,甚至無需觸碰低層接口。

硬件設(shè)計(jì)

LIDAR傳感器通過測(cè)量光脈沖到達(dá)目標(biāo)并返回的時(shí)間來計(jì)算與目標(biāo)之間的距離。測(cè)量時(shí)間時(shí),以ADC 采樣數(shù)據(jù)為增量, 這里ADC采樣速率決定了系統(tǒng)對(duì)接收的光脈沖采樣時(shí)的分辨率。公式1顯示如何根據(jù)ADC采樣速率計(jì)算距離。

其中:

LS為光的速度,3 × 108 m/s

fS為ADC采樣速率

N為光脈沖生成至返回接收期間ADC樣本的數(shù)量

假設(shè)系統(tǒng)使用AD9094JESD204B四通道ADC的1 GHz采樣速率,那么每個(gè)樣本結(jié)果相當(dāng)于15厘米距離。因此,系統(tǒng)中不能存在采樣不確定性,因?yàn)槿魏螛颖静淮_定性都可能導(dǎo)致巨大的距離測(cè)量誤差。傳統(tǒng)上,LIDAR系統(tǒng)以并行ADC為基礎(chǔ),這種ADC本身提供零采樣不確定性。隨著接收通道的數(shù)量不斷增加,功率和PCB尺寸的要求越來越嚴(yán)格,這些ADC類型不能很好地?cái)U(kuò)展。另一選項(xiàng)是使用具備高速串行輸出的ADC,例如JESD204B,以解決并行ADC存在的問題。這種選項(xiàng)的數(shù)據(jù)接口復(fù)雜度更高,因此難以實(shí)現(xiàn)零采樣不確定性。

圖3.DAQ板時(shí)鐘和數(shù)據(jù)路徑。

圖4.AFE板信號(hào)鏈。

LIDAR DAQ板提供了解決這些挑戰(zhàn)的方案,通過展示為在Subclass 1模式下運(yùn)行的JESD204B數(shù)據(jù)采集系統(tǒng)的電源、時(shí)鐘和數(shù)據(jù)接口設(shè)計(jì)來確保確定性延遲,以實(shí)現(xiàn)零采樣不確定性,同時(shí)利用JESD204B接口提供的所有優(yōu)勢(shì),令時(shí)鐘方案的功耗達(dá)到最低。要在Subclass 1模式下運(yùn)行JESD204B,系統(tǒng)總共要用到5個(gè)時(shí)鐘:

? ADC采樣時(shí)鐘:驅(qū)動(dòng)ADC信號(hào)采樣過程。

? ADC和FPGA SYSREF:源同步、高壓擺率時(shí)序分辨率信號(hào),用于重置器件時(shí)鐘分頻器,以確保獲得確定性的延遲。

? FPGA全局時(shí)鐘(也稱為內(nèi)核時(shí)鐘或器件時(shí)鐘):驅(qū)動(dòng)JESD204B PHY層和FPGA邏輯的輸出。

? FPGA參考時(shí)鐘:生成JESD204B收發(fā)器所需的PHY層內(nèi)部時(shí)鐘;需要等于,或是器件時(shí)鐘的整數(shù)倍。

所有時(shí)鐘都由一個(gè)AD9528 JESD204B時(shí)鐘生成器生成,因此可以確保它們彼此都同步。 圖3顯示了時(shí)鐘方案,以及與FPGA的數(shù)據(jù)接口。

AFE板接收光學(xué)反射信號(hào),將其轉(zhuǎn)化成電子信號(hào),然后傳輸給DAQ板上的ADC。這個(gè)板可能是整個(gè)設(shè)計(jì)中靈敏度最高的部分,因?yàn)樗旌闲盘?hào)調(diào)節(jié)電路(使用16通道APD陣列生成的微安電流信號(hào)),將光學(xué)信號(hào)轉(zhuǎn)化成電子信號(hào),并采用為同樣的APD供電所需的–120 V至–300 V大電壓電源。16個(gè)電流輸出被饋送至4個(gè)低噪聲四通道互阻增益放大器(TIA)LTC6561,帶有一個(gè)內(nèi)部4合1復(fù)用器,用于選擇之后向其中一個(gè)ADC輸入端饋送的輸出通道。要特別注意TIA的輸入部分,以實(shí)現(xiàn)所需的信號(hào)完整度和通道隔離等級(jí),使得APD生成的極低電流信號(hào)中不會(huì)摻雜更多噪聲,從而最大化系統(tǒng)的SNR和對(duì)象檢測(cè)率。AFE板的設(shè)計(jì)顯示,要實(shí)現(xiàn)最高信號(hào)質(zhì)量,最好的方法是讓APD和TIA之間的線路長(zhǎng)度盡可能短,并在TIA輸入之間增加橢圓孔,以最大化通道間隔離;此外,在部署信號(hào)調(diào)節(jié)電路時(shí),要保證該電路不會(huì)干擾板上的其他電源電路。另一項(xiàng)重要特性是能夠測(cè)量APD的溫度,以補(bǔ)償APD信號(hào)輸出的變化,這種變化是因?yàn)樵谡_\(yùn)行期間APD溫度上升導(dǎo)致的。提供幾個(gè)旋鈕來控制信號(hào)鏈的偏置和APD偏置,這些偏置轉(zhuǎn)化成APD靈敏度,從而最大化ADC輸入范圍,以實(shí)現(xiàn)最大SNR。圖4顯示了AFE板信號(hào)鏈的框圖。

激光器板生成波長(zhǎng)為905 nm的光學(xué)脈沖。它使用四個(gè)激光器,這些激光器同時(shí)驅(qū)動(dòng),以增加光束強(qiáng)度,實(shí)現(xiàn)更長(zhǎng)的測(cè)量距離。此激光器使用由FPGA載波板生成的具備可編程脈寬和頻率的PWM信號(hào)來控制。這些信號(hào)在FPGA上生成,以LVDS從FPGA傳輸至激光器板,經(jīng)過DAQ板以及連接DAQ和激光器板的扁平電纜期間,不易受到噪聲影響。驅(qū)動(dòng)信號(hào)可以返回至其中一個(gè)ADC通道,以獲得飛行時(shí)間參考。采用外部電源為激光器供電。其設(shè)計(jì)符合國際標(biāo)準(zhǔn)IEC 60825-1:2014和IEC 60825-1:2007中關(guān)于Class 1級(jí)激光器產(chǎn)品的要求。

圖5.激光器板信號(hào)鏈。

圖6.HDL設(shè)計(jì)框圖。

AFE和激光器板都需要光學(xué)器件,以實(shí)現(xiàn)長(zhǎng)距離測(cè)量。事實(shí)證明,該系統(tǒng)可在60米范圍內(nèi)測(cè)量,使用快速軸準(zhǔn)直器1,幫助激光二極管將垂直FoV縮小到1°,同時(shí)在保持水平視場(chǎng)不變的情況下,在接收側(cè)放置一個(gè)非球面透鏡。

HDL參考設(shè)計(jì)

HDL設(shè)計(jì)包含連接硬件的主要接口,其邏輯電路實(shí)現(xiàn)了將來自JESD鏈接的數(shù)據(jù)傳輸至系統(tǒng)存儲(chǔ)器,驅(qū)動(dòng)激光器,同步接收器和發(fā)射器以準(zhǔn)確測(cè)量飛行時(shí)間,并且在所有組件上設(shè)計(jì)了通信接口。圖6顯示了HDL設(shè)計(jì)的簡(jiǎn)化框圖。ADI的HDL參考設(shè)計(jì)采用了通用架構(gòu)使得框架可擴(kuò)展,且更容易連接另一個(gè)FPGA端口。該設(shè)計(jì)使用ADI公司的JESD204B框架2,以及多個(gè)SPI和GPIO接口來接收來自AD9094 ADC的數(shù)據(jù),以及控制該原型機(jī)平臺(tái)上的所有器件。

JESD204鏈接配置用于支持4個(gè)數(shù)據(jù)轉(zhuǎn)換器(M),這些轉(zhuǎn)換器使用線路速率為10 Gbps的4條路線來實(shí)現(xiàn)8位轉(zhuǎn)換器分辨率。器件時(shí)鐘與高速收發(fā)器的參考時(shí)鐘相同,被設(shè)置為250 MHz,由DAQ板提供。該鏈接在Subclass 1模式下運(yùn)行,確保高速轉(zhuǎn)換器和FPGA之間具備確定性延遲。

對(duì)于LIDAR系統(tǒng),最大的挑戰(zhàn)在于如何同步各種功能和發(fā)射脈沖,以及如何處理從高速ADC接收的必要數(shù)量的數(shù)據(jù)。為了解決這一挑戰(zhàn),HDL設(shè)計(jì)中包含了一個(gè)IP,用于提供生成激光器脈沖所需的邏輯,控制TIA的內(nèi)部多路復(fù)用器,以及為DMA提供背壓。所有這些控制函數(shù)都與發(fā)射脈沖同步,以便系統(tǒng)無需保存所有原始高速量化數(shù)據(jù)流。如此,大幅降低系統(tǒng)的總數(shù)據(jù)速率。

軟件

定義LIDAR平臺(tái)的軟件堆棧的幾個(gè)關(guān)鍵點(diǎn)包括自由和開源。用戶因此能夠“自由運(yùn)行、復(fù)制、分發(fā)、學(xué)習(xí)、變更和改善軟件,”3 包括從Linux?內(nèi)核到用戶域的工具,以及與此相關(guān)的所有代碼。

圖7.軟件堆棧。

內(nèi)核中使用的軟件驅(qū)動(dòng)器會(huì)啟動(dòng)硬件組件,向用戶顯示所有可用功能。這些驅(qū)動(dòng)器大部分都是工業(yè)I/O (IIO) Linux子系統(tǒng)的組成部分。4這些驅(qū)動(dòng)器都與平臺(tái)無關(guān),所以無需改變硬件,包括與FPGA供應(yīng)商相關(guān)的部分(例如,從Xilinx? FPGA遷移至Intel?)。

為了簡(jiǎn)化軟件接口IIO器件開發(fā),ADI開發(fā)出了libiio庫。5該庫提取硬件的低層詳情,提供簡(jiǎn)單但完整的編程接口,可供高級(jí)項(xiàng)目使用。多種可用的libiio后端(例如,本地、網(wǎng)絡(luò)、USB、串行端)支持在本地使用IIO器件,以及遠(yuǎn)程在不同操作系統(tǒng)上運(yùn)行的應(yīng)用(包括,Linux、Windows?、macOS?)中使用該器件。

ADI開發(fā)的IIO示波器就是這樣一項(xiàng)應(yīng)用示例,它使用libiio連接IIO器件,可在系統(tǒng)評(píng)估階段使用。該工具可在不同模式下捕捉和圖示數(shù)據(jù)(例如,時(shí)域、頻域、星座圖、交互相關(guān))、發(fā)送數(shù)據(jù)以及允許用戶查看和修改被檢測(cè)器件的設(shè)置。

圖8.顯示LIDAR數(shù)據(jù)的IIO示波器捕捉窗口。

雖然libiio提供低層編程接口,但在大多數(shù)情況下,用戶期望使用平臺(tái)相關(guān)的集合了低層驅(qū)動(dòng)器調(diào)用的API,來展示一組功能,用于訪問和配置各種系統(tǒng)參數(shù)和流數(shù)據(jù)。因此,LIDAR原型制作平臺(tái)采用特定的API,以及適用于常用框架和編程語言(例如C/C++、MATLAB?或Python?)的配套組件,6使用戶能夠使用其首選的編程語言與系統(tǒng)連接,集中精力研發(fā)對(duì)客戶而言極具價(jià)值的算法和應(yīng)用。

結(jié)論

對(duì)于系統(tǒng)設(shè)計(jì),在建立架構(gòu)和做出設(shè)計(jì)決定時(shí),存在一定程度的模糊性。這代表著系統(tǒng)構(gòu)建完成后無法正常工作或運(yùn)行的風(fēng)險(xiǎn),會(huì)導(dǎo)致重復(fù)的設(shè)計(jì)周期,增加開發(fā)成本,以及延長(zhǎng)產(chǎn)品上市時(shí)間。參考設(shè)計(jì)以預(yù)設(shè)計(jì)的、針對(duì)彼此交互操作的系統(tǒng)為基礎(chǔ),與從頭開始的自定義專用設(shè)計(jì)相比,其風(fēng)險(xiǎn)降低,整體可預(yù)測(cè)性和可靠性提高。在規(guī)劃過程中使用參考設(shè)計(jì)作為起點(diǎn),有助于更快將新設(shè)計(jì)推向市場(chǎng),并確保出現(xiàn)更少的意外和問題。系統(tǒng)設(shè)計(jì)人員總是尋求通過參考平臺(tái)來驗(yàn)證其設(shè)計(jì)方案,以降低風(fēng)險(xiǎn)和提高可靠性。啟動(dòng)項(xiàng)目時(shí),使用清晰標(biāo)準(zhǔn)的設(shè)計(jì)選項(xiàng)有助于推動(dòng)規(guī)劃過程的實(shí)施。可通過使用通用語言來幫助協(xié)調(diào)目標(biāo),鼓勵(lì)多個(gè)職能部門相互合作和參與來實(shí)現(xiàn),并且?guī)椭?jiǎn)化在各設(shè)計(jì)目標(biāo)之間評(píng)估和取舍的難度。LIDAR原型制作平臺(tái)試圖通過提供開源硬件和軟件設(shè)計(jì)來滿足這些需求,這些設(shè)計(jì)可以提供初始系統(tǒng)架構(gòu)階段的參考。硬件平臺(tái)和軟件堆棧可用于整個(gè)產(chǎn)品開發(fā)階段,從初始系統(tǒng)評(píng)估、開發(fā),到集成到最終產(chǎn)品中。參考設(shè)計(jì)的內(nèi)容(例如工程圖紙和BOM)可構(gòu)建、合法、本地化的系統(tǒng)設(shè)計(jì)提供了一個(gè)良好的開端。可以幫助縮短設(shè)計(jì)周期,且可能在整個(gè)過程中幫助節(jié)省資金。模塊化硬件設(shè)計(jì)支持使得各種配置選項(xiàng)滿足特定的應(yīng)用要求,而基于行業(yè)標(biāo)準(zhǔn)框架和編程語言,搭配應(yīng)用示例的開源軟件堆棧則允許客戶側(cè)重于開發(fā)應(yīng)用,為產(chǎn)品注入價(jià)值,無需將精力耗費(fèi)在堆棧的低層。

參考文獻(xiàn)

1 快速軸準(zhǔn)直透鏡。FISBA,2019年。

2 JESD204接口框架。ADI公司,2019年。

3 自由軟件是什么?Free Software Foundation, Inc.,2019年。

4 Linux Driver Implementer的API指南。ADI公司,2019年。

5 關(guān)于libiio。ADI公司,2019年。

6 “PyADI-IIO:ADI Python接口,適用于配備工業(yè)I/O驅(qū)動(dòng)器的硬件。”GitHub, Inc.,2020年。

Michael Hennerich和Robin Getz。“ADI公司如何看待自由和開源軟件。”《模擬對(duì)話》,第44卷第3期,2010年3月。

作者簡(jiǎn)介

István Csomortáni是ADI公司的FPGA設(shè)計(jì)工程師,負(fù)責(zé)支持基于FPGA的參考設(shè)計(jì)的設(shè)計(jì)與開發(fā)。他擁有工業(yè)自動(dòng)化與信息技術(shù)學(xué)士學(xué)位及集成電路設(shè)計(jì)碩士學(xué)位。他從2012年開始進(jìn)入ADI公司工作,負(fù)責(zé)為高速轉(zhuǎn)換器和RF收發(fā)器提供各種系統(tǒng)級(jí)參考設(shè)計(jì)支持。

Dragos Bogdan目前是SDG部的小型嵌入式軟件開發(fā)團(tuán)隊(duì)負(fù)責(zé)人,為各種類型的平臺(tái)和組件增加開源裸機(jī)和Linux支持。Dragos于2011年加入ADI公司擔(dān)任軟件工程師。2010年到2011年間,他在Pergamon RD公司從事用于打印設(shè)備的嵌入式硬件和軟件的開發(fā)工作。在此之前,他曾參加National Instruments和Continental Automotive的實(shí)習(xí)生項(xiàng)目。他擁有克盧日-納波卡科技大學(xué)電子學(xué)學(xué)士學(xué)位和自動(dòng)化碩士學(xué)位。

Cristian Orian是ADI公司的系統(tǒng)設(shè)計(jì)工程師,負(fù)責(zé)評(píng)估平臺(tái)的硬件開發(fā)工作。他擁有電子學(xué)博士學(xué)位。其工作領(lǐng)域還涉及電源設(shè)計(jì)。

Andrei Cozma是ADI公司工程設(shè)計(jì)經(jīng)理,負(fù)責(zé)支持系統(tǒng)級(jí)參考設(shè)計(jì)的設(shè)計(jì)與開發(fā)。他擁有工業(yè)自動(dòng)化與信息技術(shù)學(xué)士學(xué)位及電子與電信博士學(xué)位。他參與過電機(jī)控制、工業(yè)自動(dòng)化、軟件定義無線電和電信等不同行業(yè)領(lǐng)域的項(xiàng)目設(shè)計(jì)與開發(fā)。