在半導(dǎo)體產(chǎn)業(yè)的黃金時(shí)代,當(dāng)戈登·摩爾還在為自己的公司制定路線圖時(shí),平面尺寸的縮小就帶來了功耗、性能和面積/成本的同步進(jìn)步(PPAC)。但隨著時(shí)間的推移,登納德平面尺寸縮小定律對功耗的幫助受阻,而材料工程開始應(yīng)用于半導(dǎo)體制造,以促進(jìn)功耗、性能和面積/成本的持續(xù)提高。其中,高K值金屬柵極就是一個(gè)最有力的例證。

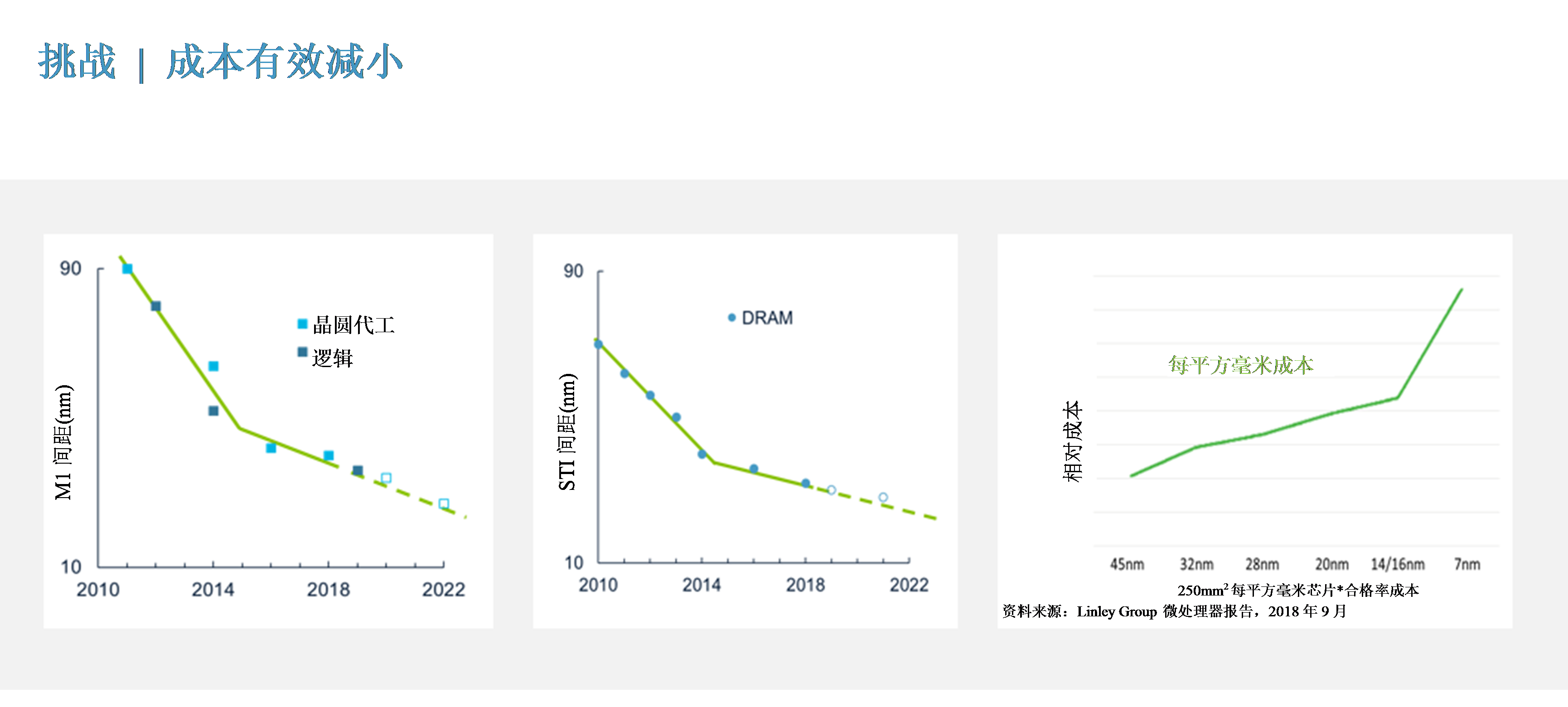

目前,工程師們普遍承認(rèn)這種矛盾:設(shè)計(jì)工程師對功耗和性能進(jìn)行優(yōu)化,而工藝工程師則進(jìn)行積極的2D尺寸縮小來減少面積和成本。無論邏輯還是存儲(chǔ)器,尤其是當(dāng)業(yè)界生產(chǎn)圖形縮小至8nm 以下時(shí),設(shè)計(jì)的進(jìn)步?jīng)]有與工藝創(chuàng)新有機(jī)地結(jié)合。盡管節(jié)點(diǎn)命名尺寸在縮小,但特征尺寸的縮小速度卻不及以往。此外,我們也看到成本降低的速度在急劇放緩(見圖1)。

圖1:芯片設(shè)計(jì)的復(fù)雜性導(dǎo)致特征尺寸縮小放緩和成本上升

為什么尺寸縮小并沒按應(yīng)有的速度不斷進(jìn)步呢?為什么高端硅成本依然如此昂貴?答案就在于芯片設(shè)計(jì)的復(fù)雜性--如今的芯片設(shè)計(jì)層數(shù)繁多,各層之間還必須無縫連接。

以DRAM為例。一個(gè)DRAM器件大約有7個(gè)關(guān)鍵圖形層,每層各不相同(見圖2)。除了淺溝槽隔離(STI)層、電容、位線和字線的物理結(jié)構(gòu)不同,還有些層的長寬比很高,這使得上一層與下一層對準(zhǔn)的難度越來越大。這些不同特征圖形必須要完好地成像并對準(zhǔn)才能確保器件的正常工作。然而,這些截然不同的圖形層的同時(shí)縮小,給工藝的實(shí)現(xiàn)帶來了更大的復(fù)雜性。一旦工藝不能滿足要求,圖形邊緣平整性誤差(EPE)會(huì)增加電阻、降低性能,最終導(dǎo)致良率損失和器件故障。

圖2: DRAM各自不同的器件層中生成對圖形縮小和對準(zhǔn)的挑戰(zhàn)

因此,在路線圖受阻下,我們需要一個(gè)“新戰(zhàn)略”來改善芯片性能、功率、面積成本以及產(chǎn)品走向市場的時(shí)間(PPACt)。“新戰(zhàn)略”包括:

·新的計(jì)算架構(gòu)

·芯片上新器件和3D結(jié)構(gòu)

·新型材料

·持續(xù)2D尺寸縮小的新方法(本博客主題)

·異構(gòu)設(shè)計(jì)和先進(jìn)封裝

從設(shè)備的角度來看,我們需要做的不僅僅是引進(jìn)新的薄膜或改進(jìn)刻蝕之類的單項(xiàng)工藝。我們還需要全盤綜合考慮,并根據(jù)每個(gè)器件需求開發(fā)出相應(yīng)的配套技術(shù)。

這種從單項(xiàng)工藝到材料集成解決方案的演進(jìn)也可以幫助客戶削減工藝步驟、減少研發(fā)成本和時(shí)間,最終加快產(chǎn)品上市的速度。以下是我在今年早些時(shí)候召開的SPIE高級光刻會(huì)議上發(fā)布的三項(xiàng)創(chuàng)新技術(shù),這些技術(shù)展示了如何通過使用先進(jìn)圖形成像的整體方法讓芯片制造商在多方面受益。

直角側(cè)壁掩膜技術(shù)

直角側(cè)壁掩膜技術(shù)是對兩次自對準(zhǔn)圖形成像(SADP)和四次自對準(zhǔn)圖形成像(SAQP)的應(yīng)用。側(cè)壁沉積和側(cè)壁刻蝕很挑戰(zhàn),原因之一就是所用的材料相對柔軟,頂部和底部易弧化(不易形成直角)。這會(huì)導(dǎo)致不均勻性和間距漂移,進(jìn)而造成光刻套準(zhǔn)誤差和垂直偏差EPE--在更小的工藝節(jié)點(diǎn)上,這類波動(dòng)問題會(huì)更為嚴(yán)重。

芯片制造商通常會(huì)通過增加額外的工藝步驟來解決波動(dòng)問題,這也將增加成本和復(fù)雜性。此外,盡管額外的硬掩模刻蝕和核心掩膜刻蝕工藝可減少來自第一次側(cè)壁刻蝕的波動(dòng)性,但也會(huì)降低設(shè)計(jì)人員想要的關(guān)鍵尺寸(CD)的實(shí)現(xiàn)。換言之,解決EPE的工藝步驟同時(shí)伴隨著性能的妥協(xié),會(huì)降低對設(shè)計(jì)結(jié)果的控制水平。

應(yīng)用材料公司開發(fā)的一項(xiàng)新工藝就能夠優(yōu)化側(cè)壁材料,使其能更適應(yīng)刻蝕工藝,從而實(shí)現(xiàn)更好的對準(zhǔn)效果(見圖3)。這項(xiàng)工藝首先使用CVD工藝以類似ALD的精度沉積非晶硅,然后用我們的Centris? Sym3?刻蝕系統(tǒng)進(jìn)行圖形成像,和VeritySEM?系統(tǒng)測量。我們提供的解決方案能讓芯片制造商在使用傳統(tǒng)的工藝步驟的同時(shí),還能保持圖形成像的保真度,通過去除不必要的沉積和刻蝕步驟將SAQP步驟數(shù)從15個(gè)縮減至11個(gè)。整體有助于客戶用更經(jīng)濟(jì)高效的方式實(shí)現(xiàn)圖形尺寸減小。

圖3:與傳統(tǒng)工藝相比,應(yīng)用材料公司獨(dú)特的側(cè)壁材料能實(shí)現(xiàn)更好的均勻性和對準(zhǔn)效果

橫向刻蝕技術(shù)

應(yīng)用材料公司開發(fā)的另一項(xiàng)獨(dú)特技術(shù)被稱為橫向刻蝕。在使用傳統(tǒng)的光刻和刻蝕工藝的時(shí)候,設(shè)計(jì)人員只能以有限的緊密度將各種特征結(jié)合在一起。這在水平方向上稱為最小線空距,在垂直方向上稱為頂?shù)缀穸取.?dāng)使用EUV時(shí),目前最小線空距約為36nm,而頂?shù)缀穸燃s為40nm。如果這些線空距對設(shè)計(jì)方案而言尺寸太大,芯片制造商就不得不投資額外的圖形成像步驟--要么是增加掩模切斷或選擇性掩模,要么增加EUV光刻-刻蝕步驟。而唯一的替代方案是繼續(xù)使用較大的芯片面積,但這會(huì)增加芯片面積/成本比。

刻蝕歷來是自上而下進(jìn)行的。但應(yīng)用材料公司開發(fā)了一項(xiàng)創(chuàng)新型的橫向刻蝕技術(shù),它能夠進(jìn)行45度角的刻蝕,為設(shè)計(jì)人員帶來了新的自由度(見圖4)。通過控制刻蝕方向,我們就能在保持縱向掩膜厚度下,橫向收縮CD。事實(shí)證明,我們已能實(shí)現(xiàn)橫向CD獨(dú)立縮小下縱向膜厚約20nm。

圖4:應(yīng)用材料公司的創(chuàng)新型橫向刻蝕技術(shù)可將EUV掩模數(shù)減少50%甚至更多

橫向刻蝕可以讓設(shè)計(jì)人員減少工藝步驟,讓各項(xiàng)特征結(jié)合更緊密,從而增加面積密度,惠及更多器件的應(yīng)用。我們將這一工藝與我們的Producer? Precision? CVD碳和硅硬掩模、Sym3 刻蝕以及PROVision?電子束測量和缺陷控制進(jìn)行協(xié)同優(yōu)化,以實(shí)現(xiàn)先進(jìn)圖形成像解決方案,使設(shè)計(jì)人員有機(jī)會(huì)將EUV掩模數(shù)減少50%甚至更多。

選擇性工藝技術(shù)

我們在SPIE高級光刻會(huì)議上發(fā)布的第三項(xiàng)技術(shù)是一種選擇性材料沉積工藝。該工藝可解決EPE的問題,通過控制不同器件層之間的位錯(cuò)來改善圖形縮小效果。與傳統(tǒng)沉積不同,選擇性加工(沉積/刻蝕)工藝用于消除EPE,從而設(shè)計(jì)規(guī)則上尺寸得到減少并降低掩模數(shù)。

要使選擇性沉積有效減少EPE,有兩大關(guān)鍵挑戰(zhàn)必須設(shè)法克服。第一,晶圓表面必須足夠清潔,以便實(shí)現(xiàn)所需材料(而非其他材料)上進(jìn)行選擇性沉積。晶圓上的任何缺陷都會(huì)損害選擇性。第二個(gè)挑戰(zhàn),是有效地控制選擇性沉積的材料,這種材料不僅會(huì)垂直生長,而且還會(huì)水平生長。由于上述挑戰(zhàn),大多數(shù)選擇性沉積僅限于在很薄的層上進(jìn)行。

應(yīng)用材料公司利用Endura沉積平臺、Producer Selectra選擇性刻蝕技術(shù)以及PROVision?電子束測量和缺陷檢測技術(shù)開發(fā)出了一項(xiàng)協(xié)同優(yōu)化的選擇性加工解決方案。我們已經(jīng)在圖5所示的通孔工藝流程中演示了這一工藝。我們首先從金屬層開始,進(jìn)行材料選擇性生長;隨后進(jìn)行填充和平坦化;接下來進(jìn)行氮化鈦(TiN)硬掩模傳統(tǒng)工藝處理,通孔光刻膠層積;然后繼續(xù)通孔光刻,再轉(zhuǎn)入刻蝕。當(dāng)我們在一個(gè)方向上進(jìn)行刻蝕時(shí),它對定義溝槽的TiN起到掩膜作用。我們新開發(fā)的材料具有刻蝕高選擇。這意味著通孔會(huì)被完美刻蝕成一個(gè)矩形,該矩形定義了兩個(gè)金屬層彼此交錯(cuò)的位置。這種技術(shù)通過最大限度地?cái)U(kuò)大通孔尺寸來消除EPE,也消除了與互連尺寸減小相關(guān)的問題。

圖5:視頻顯示了結(jié)合Applied材料工程能力的通孔流程,目的是減少掩模數(shù)并改善EPE。

如果設(shè)計(jì)人員通孔版圖比光刻的最低分辨率高,他們就必須采用多次光刻-刻蝕的通孔工藝。使用我們的新工藝,客戶可以定義一個(gè)較大的通孔,并僅在兩個(gè)金屬層之間的交叉處建立通孔。這樣,我們就能將底部和頂部器件層完美對準(zhǔn),從而節(jié)省工藝步驟,并實(shí)現(xiàn)大工藝寬容度低阻抗通孔(見圖6)。

VLSIresearch董事長兼首席執(zhí)行官Dan Hutcheson表示:“真正的創(chuàng)新之處在于,與傳統(tǒng)的多重圖形成像多次圖像合成切割掩模方法相比,應(yīng)用材料公司能夠建立新的通孔工藝,從而減少EPE引起的良率損失并降低成本,同時(shí)還能因單通孔節(jié)約0.7納米。除了提高良率外,減少EPE還能增加每片晶圓的收入,因?yàn)樾酒目煽啃院托阅芫刑嵘酒膮s更低。”

圖6:與傳統(tǒng)工藝相比,具有完全選擇性的自對準(zhǔn)加工可降低電阻、增加良率并減少掩模數(shù)

總而言之,這一“新戰(zhàn)略”為我們帶來了加快推進(jìn)行業(yè)路線圖的新工具,包括從全局角度應(yīng)對尺寸減小的挑戰(zhàn),以求同時(shí)解決PPACt的各項(xiàng)問題。通過協(xié)同優(yōu)化應(yīng)用材料公司廣泛的技術(shù),我們可以提供新的材料來實(shí)現(xiàn)新的圖形尺寸減小,讓經(jīng)濟(jì)高效的縮放能夠在不影響設(shè)計(jì)的前提下繼續(xù)推進(jìn)。歡迎步入材料化圖形成像時(shí)代!

作者簡介:

Regina Freed是應(yīng)用材料公司圖形成像技術(shù)全球執(zhí)行總監(jiān)。她擁有超過20年半導(dǎo)體行業(yè)經(jīng)驗(yàn),負(fù)責(zé)邏輯/存儲(chǔ)器件光刻、測量及缺陷檢測工藝的研發(fā)。