從家庭控制中智能門鈴和安全攝像頭的存在檢測,到零售應(yīng)用中用于庫存的對象計數(shù),再到工業(yè)應(yīng)用中物體和存在檢測,越來越多的網(wǎng)絡(luò)邊緣應(yīng)用正在不斷推動新型AI解決方案面市。根據(jù)IHS Markit(現(xiàn)Omida)的預(yù)測,2018-2025年物聯(lián)網(wǎng)設(shè)備數(shù)量將達到400億,截至2022年,所有企業(yè)產(chǎn)生的數(shù)據(jù)中近50%會在傳統(tǒng)數(shù)據(jù)中心或云端以外的地方進行處理。

但與此同時,市場一方面要求設(shè)計人員開發(fā)出性能比以往更高的解決方案;另一方面,延遲、帶寬、隱私、功耗和成本問題又限制了他們依賴云的計算資源來執(zhí)行分析。如何解決系統(tǒng)對于日益嚴(yán)格的功耗(毫瓦級)和小尺寸(5mm2到100mm2)要求?如何能夠快速獲得相應(yīng)的硬件和軟件工具、參考設(shè)計、演示示例和設(shè)計服務(wù)?萊迪思公司為此做出了有益的嘗試。

Lattice sensAI再獲重大更新

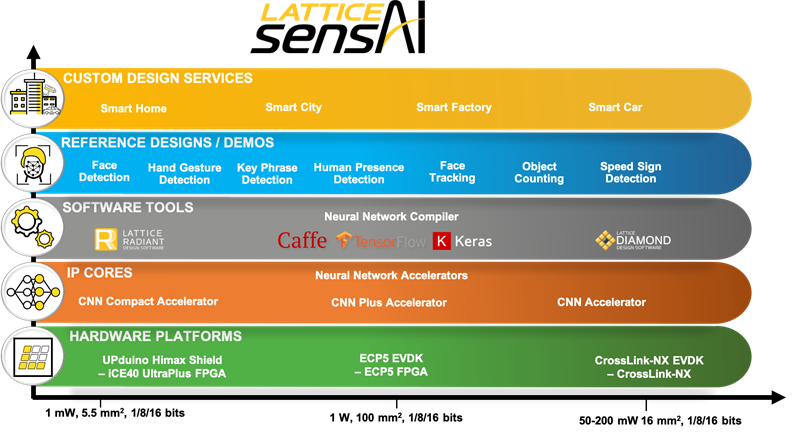

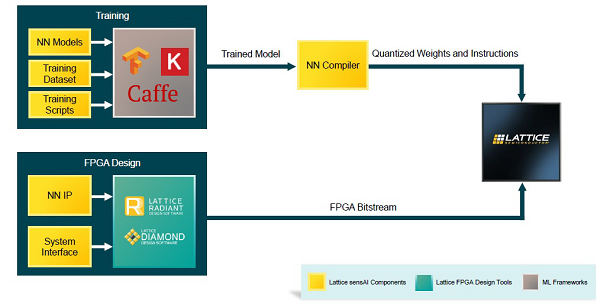

作為萊迪思推出的業(yè)界第一款用于網(wǎng)絡(luò)邊緣設(shè)備端AI處理的完整解決方案集合,sensAITM提供了供開發(fā)人員評估、開發(fā)和部署基于FPGA的機器學(xué)習(xí)/人工智能解決方案所需的全部資源,包括模塊化硬件平臺、演示示例、參考設(shè)計、神經(jīng)網(wǎng)絡(luò)IP核、軟件開發(fā)工具和定制化設(shè)計服務(wù)。

圖1:sensAI架構(gòu)框圖

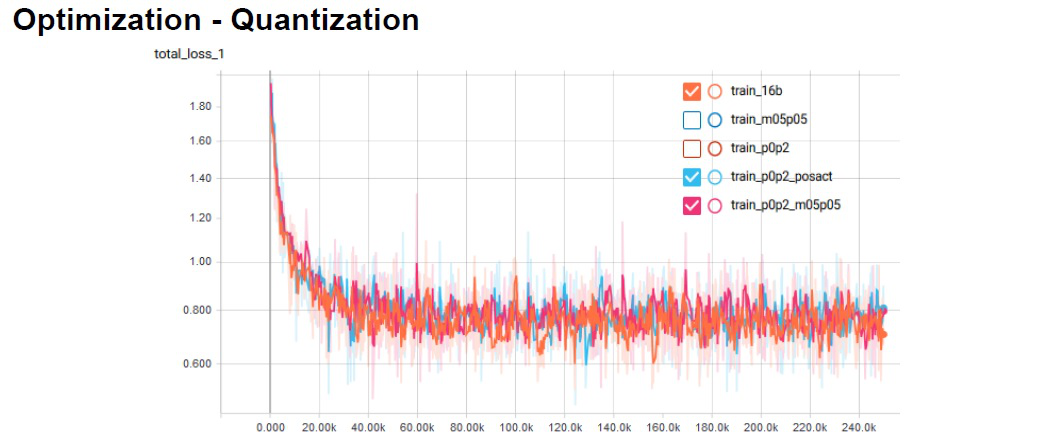

2019年上半年,sensAI通過更新迎來10倍性能提升,這是由多個優(yōu)化促成的,包括通過更新CNN IP和神經(jīng)網(wǎng)絡(luò)編譯器、新增8位激活量化、智能層合并以及雙DSP引擎等特性。而最令人感到興奮的是它新增并優(yōu)化了用于快速實現(xiàn)網(wǎng)絡(luò)邊緣常見AI應(yīng)用的參考設(shè)計,為關(guān)鍵詞檢測、人臉識別、人員偵測、人員計數(shù)等賦予了更強大的特性。

圖2:在訓(xùn)練過程中支持8位量化可在神經(jīng)網(wǎng)絡(luò)模型訓(xùn)練過程中實現(xiàn)更高的精度

為了演示關(guān)鍵詞檢測系統(tǒng)的功能,工程師使用了搭載iCE40 UltraPlus FPGA的HiMax HM01B0 UPduino shield開發(fā)板。該開發(fā)板有兩個直連到FPGA的I2S麥克風(fēng)、用于FPGA設(shè)計的外部閃存、權(quán)重激活存儲器、以及LED指示燈用以指示是否檢測到關(guān)鍵詞。用戶可以直接對麥克風(fēng)說話,一旦檢測到關(guān)鍵詞,LED就會亮起。

圖3:關(guān)鍵詞檢測演示系統(tǒng)

圖4左側(cè)是針對低功耗運行進行優(yōu)化、采用CMOS圖像傳感器的人員偵測演示,通過VGG8網(wǎng)絡(luò)提供64 x 64 x 3的分辨率,該系統(tǒng)以每秒5幀的速率運行,使用iCE40 UltraPlus FPGA功耗僅為7mW;右側(cè)是性能經(jīng)優(yōu)化的人員計數(shù)應(yīng)用演示,同樣也使用CMOS圖像傳感器,通過VGG8網(wǎng)絡(luò)提供128 x 128 x 3的分辨率。該演示以每秒30幀的速率運行,使用ECP5-85K FPGA功耗為850mW。

圖4:這些參考設(shè)計展示了sensAI提供的功耗與性能可選方案

Lattice人員識別參考設(shè)計方案也應(yīng)用于售賣機上檢測人員的出現(xiàn),喚醒售賣機的內(nèi)核。通過減少非人員靠近造成的誤觸發(fā),或人員路過造成的誤觸發(fā),達到減小功耗的目的。

2020年5月,sensAI又成功升級至3.0版本。

在此前支持ECP5/ECP5-5G和iCE40 UltraPlus 模塊化硬件平臺的基礎(chǔ)上,新推出的sensAI 3.0版本支持CrossLink-NX?系列FPGA,運行sensAI軟件的CrossLink-NX FPGA比之前版本降低了一半的功耗,同時實現(xiàn)性能翻倍,從而為監(jiān)控/安防、機器人、汽車和計算領(lǐng)域的智能視覺應(yīng)用帶來功耗和性能上的再次突破。同時,它還擁有定制化卷積神經(jīng)網(wǎng)絡(luò)CNN IP并新增支持MobileNet v2、SSD和ResNet模型,這些靈活的加速器IP可簡化常見CNN網(wǎng)絡(luò)的實現(xiàn),經(jīng)優(yōu)化后可更加充分利用FPGA的并行處理能力,開發(fā)人員可輕松編譯經(jīng)過訓(xùn)練的神經(jīng)網(wǎng)絡(luò)模型并將其下載到CrossLink-NX FPGA中。

圖6:sensAI支持多種AI算法模型

CrossLink-NX FPGA采用28nm FD-SOI工藝制造,與同類FPGA競品相比,功耗可降低75%。在CrossLink-NX FPGA上運行解決方案時,sensAI可提供多達2.5Mb的分布式內(nèi)存、RAM塊以及額外的DSP資源,MIPI I/O提供瞬時啟動的性能可在不到3ms的時間內(nèi)完成自我配置,而整個器件的配置也只需8ms。在基于CrossLink-NX的對象計數(shù)演示中,——基于VGG的對象計數(shù)演示擁有10幀/秒的性能,功耗僅為200mW。

當(dāng)AI遇見超低功耗FPGA

擁有5K LUT的iCE40 UltraPlus FPGA可實現(xiàn)網(wǎng)絡(luò)邊緣實時在線的智能應(yīng)用所需的神經(jīng)網(wǎng)絡(luò)模式匹配。其擁有5280個4輸入LUT、自定義I/O、多達80Kb和1Mb的嵌入式存儲器,睡眠電流低至75uA,工作電流僅為1-10mA,功耗低至1mW,硬件平臺尺寸小至5.5mm2。為了滿足各類應(yīng)用的需求,還采用了包括從專為電子消費品和IoT設(shè)備優(yōu)化的超小尺寸2.15 mm x 2.50 mm x 0.45 mm WLCSP封裝,到低成本應(yīng)用的0.5mm間距7x7mm QFN封裝在內(nèi)的多種封裝選項。

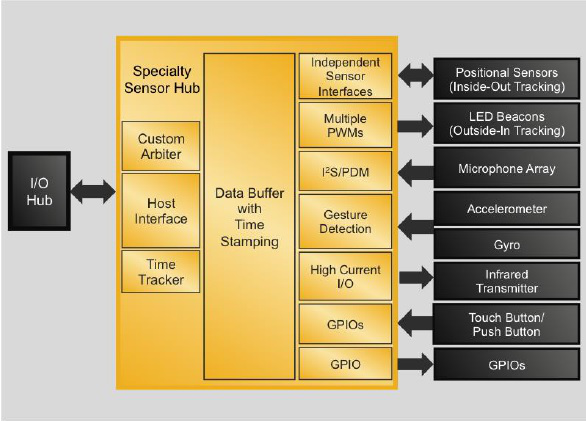

功耗優(yōu)化遙遙領(lǐng)先的原因,得益于其采用的分布式異構(gòu)處理(Distributed Heterogenous Processing, DHP)架構(gòu)。由于不使用云端執(zhí)行算法,而是使用內(nèi)置的數(shù)字信號處理器(DSP)執(zhí)行重復(fù)的數(shù)字處理任務(wù),因此大幅減少了功耗極大的應(yīng)用處理器(AP)的計算負載,從而實現(xiàn)更長時間的睡眠模式以延長電池使用時間。另一方面,內(nèi)置的神經(jīng)網(wǎng)絡(luò)軟IP和編譯器實現(xiàn)了靈活的機器學(xué)習(xí)/人工智能應(yīng)用,消除了云端智能應(yīng)用帶來的延遲,降低了整個系統(tǒng)解決方案的成本。

圖7:iCE40 UltraPlus采用的分布式異構(gòu)處理(DHP)架構(gòu)

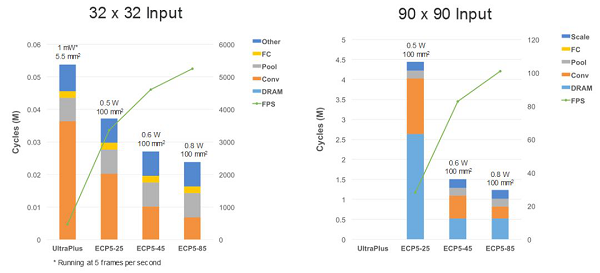

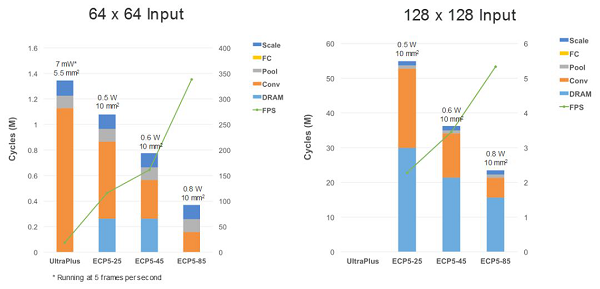

圖8和圖9描述了不同F(xiàn)PGA之間存在的資源差異如何影響到人臉檢測和人員檢測應(yīng)用的性能和功耗。圖8左側(cè)的32x32輸入示例中,橙色部分代表卷積層上運行的周期。在四個示例中,UltraPlus的乘法器數(shù)量最少,其他三片ECP5 FPGA的乘法器數(shù)量依次遞增。隨著乘法器數(shù)量的增加,卷積層所需的周期數(shù)減少;右側(cè)的90x90輸入示例中,在每個柱形圖的底部有大面積的藍色區(qū)域。這是由于設(shè)計更為復(fù)雜,需要占用外部DRAM,性能就有所折中。

圖8:在UltraPlus和ECP5 FPGA上實現(xiàn)入門級和提高級人臉檢測時的性能、功耗和占用面積

人員偵測應(yīng)用的情況類似,兩組分別采用了64x64輸入和128x128輸入的情況。同樣,較多的乘法器會減少卷積層的負擔(dān),而依賴DRAM則會影響性能。

圖9:在UltraPlus和ECP5 FPGA上實現(xiàn)簡單和復(fù)雜人員檢測時的性能、功耗和占用面積

其實,設(shè)計AI模型的最常見做法就是使用處理器,可能是GPU或者DSP,也有可能是微控制器(MCU)。不過,低端MCU可能連簡單的AI模型也無法處理,高性能處理器又可能會違反設(shè)備的功耗和成本要求,但這正是低功耗FPGA發(fā)揮作用的地方。與增強處理器來處理算法的方式不同,萊迪思iCE40 UltraPlus FPGA可以作為MCU的協(xié)處理器,處理MCU無法解決的復(fù)雜任務(wù)之余,將功耗保持在要求范圍內(nèi)。

另一種思路是將低功耗FPGA作為單獨運行的、完整的AI引擎,此時FPGA中的DSP就起到了關(guān)鍵作用。即便網(wǎng)絡(luò)邊緣設(shè)備沒有其他的計算資源,也可以在不超出功耗、成本或電路板尺寸預(yù)算的情況下添加AI功能,更何況它們還擁有支持快速演進算法所需的靈活性和可擴展性。

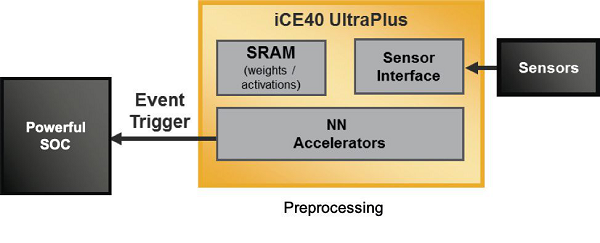

無論采取哪種方法,都意味著設(shè)計人員可以采用萊迪思sensAI以及一片低功耗的iCE40 UltraPlus FPGA對傳感器數(shù)據(jù)進行預(yù)處理,從而最大程度地降低了向SoC或云端傳輸數(shù)據(jù)進行分析的成本。例如,如果是用在智能門鈴上,sensAI會初步讀取來自圖像傳感器的數(shù)據(jù)。如果判斷為不是人,比如說是一只貓,那么系統(tǒng)就不會喚醒SoC或連接到云端作進一步處理。因此,這種方法可以最大程度降低數(shù)據(jù)傳輸成本和功耗。如果預(yù)處理系統(tǒng)判斷門口的對象是人,則喚醒SoC作進一步處理。這能極大減少系統(tǒng)需要處理的數(shù)據(jù)量,同時降低功耗要求,這對于實時在線的網(wǎng)絡(luò)邊緣應(yīng)用來說至關(guān)重要。

圖10:基于iCE40 UltraPlus FPGA的sensAI會預(yù)處理傳感器數(shù)據(jù)以判斷該數(shù)據(jù)是否需要發(fā)送到SoC作進一步處理

結(jié)語:

萊迪思的FPGA具有獨特的優(yōu)勢,可以滿足網(wǎng)絡(luò)邊緣設(shè)備快速變化的市場需求。設(shè)計人員可以在不依賴云端的情況下,快速為網(wǎng)絡(luò)邊緣設(shè)備提供更多計算資源的其中一個方法是使用FPGA中本身的并行處理能力來加速神經(jīng)網(wǎng)絡(luò)性能。此外,通過使用針對低功耗運行而優(yōu)化的低密度、小尺寸封裝FPGA,設(shè)計人員可以滿足新的消費和工業(yè)應(yīng)用對功耗和尺寸的嚴(yán)格限制。