先進(jìn)的集成電路封裝正在迅速發(fā)展,其技術(shù)是“超越摩爾定律”上突出的技術(shù)亮點(diǎn)。在每個(gè)節(jié)點(diǎn)上,芯片微縮將變得越來(lái)越困難,越來(lái)越昂貴,工程師們想到將多個(gè)芯片放入先進(jìn)的封裝中,以其作為芯片縮放的替代方案。

首先,讓我們了解高級(jí)IC封裝中不斷出現(xiàn)的基本術(shù)語(yǔ)。以下是在下一代IC封裝技術(shù)中使用的10個(gè)最常見(jiàn)的術(shù)語(yǔ)的簡(jiǎn)要概述:

1、2.5 D封裝

在2.5D的封裝中,模具被堆放或并排放置在一個(gè)隔片的頂部,基于硅通孔(TSV)。基座是一個(gè)交互器,提供芯片之間的連接。作為傳統(tǒng)2D IC封裝技術(shù)的一個(gè)增量步驟,2.5D封裝使更細(xì)的線(xiàn)條和空間成為可能。

2.5D封裝通常用于ASIC、FPGA、GPU和內(nèi)存立方體。2008年,Xilinx將其大型FPGA劃分為4個(gè)更小、產(chǎn)量更高的芯片,并將這些芯片連接到一個(gè)硅接口上。2.5D封裝就此誕生,并最終在高帶寬內(nèi)存(HBM)處理器集成中流行起來(lái)。

2、3D堆疊封裝

在3D IC封裝中,邏輯模塊堆疊在內(nèi)存模塊上,而不是創(chuàng)建一個(gè)大型的系統(tǒng)片上(SoC),并且模塊通過(guò)一個(gè)主動(dòng)交互器連接。與2.5D封裝通過(guò)導(dǎo)電凸起或TSV將組件堆疊在交互器上不同,3D封裝采用多層硅晶片與使用TSV的組件一起嵌入。

TSV是2.5D和3D集成電路封裝技術(shù)中的關(guān)鍵實(shí)現(xiàn)技術(shù)。半導(dǎo)體行業(yè)一直在使用HBM技術(shù)將DRAM封裝在3D IC中。

Cu TSV在Si芯片間垂直互連的使用

Intel的Lakefield的FOVEROS是3D封裝典型例子,他們把硅片有邏輯的疊加在一起,也兼容常見(jiàn)的PoP封裝內(nèi)存,此外還有Co-EMIB,徹底混合EMIB和FOVEROS。

3、Chiplet

Chiplet是另一種3D IC封裝形式,可使CMOS設(shè)備與非CMOS設(shè)備實(shí)現(xiàn)異構(gòu)集成。換句話(huà)說(shuō),它們是更小的SoC,中文的意思就是小芯片。這是將復(fù)雜功能進(jìn)行分解,然后開(kāi)發(fā)出多種具有單一特定功能,可相互進(jìn)行模塊化組裝的“小芯片”,如實(shí)現(xiàn)數(shù)據(jù)存儲(chǔ)、計(jì)算、信號(hào)處理、數(shù)據(jù)流管理等功能,并最終以此為基礎(chǔ),建立一個(gè)“小芯片”的芯片網(wǎng)絡(luò)。

這分解芯片的想法可以提高產(chǎn)量和比單片模具更低的成本。Chiplets允許設(shè)計(jì)者利用各種各樣的IP而不必考慮它們是在哪個(gè)節(jié)點(diǎn)或技術(shù)上制造;它們可以在硅、玻璃和層壓板等多種材料上建造。

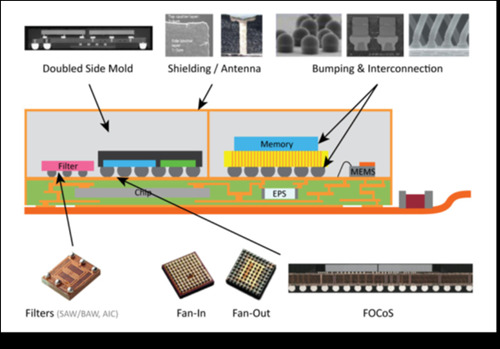

4、Fan-Out扇出封裝

Fan-Out封裝是使用環(huán)氧模具復(fù)合材料完全嵌入模具,這樣就省去了晶片碰撞、熔煉、倒裝芯片組裝、清洗、下填分配和固化等工藝流程。扇出封裝的連接在芯片表面呈扇形展開(kāi),以方便更多的外部I/O。這反過(guò)來(lái)又消除了對(duì)交互器的需求,并簡(jiǎn)化了異構(gòu)集成的實(shí)現(xiàn)。

Fan-Out技術(shù)提供了一個(gè)比其他封裝類(lèi)型具有更多I/O的小尺寸封裝。2016年,iPhone7上的16nm A10處理器和天線(xiàn)開(kāi)關(guān)模組使用了扇出晶圓級(jí)封裝(Fan-out Wafer Level Packaging,簡(jiǎn)稱(chēng)FoWLP)技術(shù),取代了傳統(tǒng)PCB,從而一舉成為科技明星。而A10的制造商臺(tái)積電是FoWLP技術(shù)的領(lǐng)先者。在臺(tái)積電內(nèi)部,他們把FoWLP稱(chēng)作InFoWLP,其中In代表integrated,也就是集成的意思。

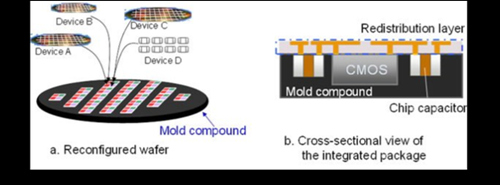

5、扇出型晶圓級(jí)封裝(FOWLP)

扇出型晶圓級(jí)封裝是一大改進(jìn),為晶圓模提供了更多的外部接觸空間。將芯片嵌入環(huán)氧模塑料內(nèi),然后在晶片表面制造高密度重分布層(RDL)和焊料球,形成重組晶片。

通常,它首先將前端處理的晶圓片分割成單個(gè)晶圓片,然后將晶圓片在載體結(jié)構(gòu)上分隔開(kāi),填充間隙以形成再生晶圓片。FOWLP在封裝和應(yīng)用板之間提供了大量的連接。此外,基板本質(zhì)上比模具大,所以模具間距更寬松。

硅膠倒裝芯片嵌入到玻璃襯底中,然后RDL在芯片上扇動(dòng),形成一個(gè)貫穿玻璃的通道

6、異構(gòu)集成

將單獨(dú)制造的組件集成到更高級(jí)別的組裝中的方式,使得功能和操作特性都會(huì)得到提升。它使半導(dǎo)體器件制造商能夠?qū)?lái)自不同制造工藝流程的功能部件組合成一個(gè)單一的復(fù)合器件。

為何要用異構(gòu)集成?

1.研發(fā)成本越來(lái)越高

芯片行業(yè)是典型的人才密集和資金密集型高風(fēng)險(xiǎn)產(chǎn)業(yè),如果沒(méi)有大量用戶(hù)攤薄費(fèi)用,芯片成本將直線(xiàn)上升。華為曾向媒體透露7nm的麒麟980研發(fā)費(fèi)用遠(yuǎn)超業(yè)界預(yù)估的5億美元,紫光展銳的一名工作人員則對(duì)記者表示,5G Modem研發(fā)費(fèi)用在上億美元,光流片就相當(dāng)費(fèi)錢(qián),還有團(tuán)隊(duì)的持續(xù)投入,累計(jì)參與項(xiàng)目的工程師有上千人。

2. 設(shè)計(jì)成本也不斷上漲,每一代至少增加30~50%的設(shè)計(jì)成本

業(yè)界人士指出:此前迭代無(wú)需考慮新工藝問(wèn)題,只需了解65nm比90nm小多少,可以直接把90nm上的設(shè)計(jì)拿到65nm工藝上,重新設(shè)計(jì)一下馬上就能做,整個(gè)過(guò)程一年半載即可完成。但現(xiàn)在7nm和16nm有很多不一樣的地方,不能把16nm的設(shè)計(jì)直接放到7nm上,從架構(gòu)到設(shè)計(jì)到后端都要做很多改變。

異構(gòu)集成類(lèi)似于封裝內(nèi)系統(tǒng)集成(SiP);主要指將多個(gè)單獨(dú)制造的部件封裝到一個(gè)芯片上,而不是在單個(gè)襯底上集成多個(gè)基片。這增強(qiáng)了功能性,可以對(duì)采用不同工藝、不同功能、不同制造商制造的組件進(jìn)行封裝。通過(guò)這一技術(shù),工程師可以像搭積木一樣,在芯片庫(kù)里將不同工藝的小芯片組裝在一起。異構(gòu)集成背后的總體思想是將在系統(tǒng)級(jí)別上變化的多個(gè)組件組合到同一個(gè)封裝中。

不過(guò),異構(gòu)集成在延續(xù)摩爾定律的同時(shí)也面臨可靠性、散熱、測(cè)試難度等多方面的挑戰(zhàn)。

7、高帶寬存儲(chǔ)器(HBM)

如今,GDDR5經(jīng)過(guò)這么多年的發(fā)展已然來(lái)到了一個(gè)瓶頸,光靠頻率提升來(lái)提供更大的顯存位寬已經(jīng)沒(méi)有太大空間,而這勢(shì)必會(huì)反過(guò)來(lái)影響到GPU的性能發(fā)揮。相對(duì)于傳統(tǒng)的GDDR5顯存來(lái)說(shuō),HBM無(wú)疑是更加先進(jìn)。

HBM是一種標(biāo)準(zhǔn)化的堆疊內(nèi)存技術(shù),它為堆棧內(nèi)以及內(nèi)存和邏輯之間的數(shù)據(jù)提供了寬通道。基于HBM的封裝將內(nèi)存堆在一起,并使用TSV將它們連接起來(lái),這樣創(chuàng)建了更多的I/O和帶寬。

HBM也是一種JEDEC標(biāo)準(zhǔn),它垂直集成了多個(gè)層次的DRAM組件,這些組件與應(yīng)用程序處理器、GPU和SoC一起在封裝中。HBM主要在高端服務(wù)器和網(wǎng)絡(luò)芯片的2.5D封裝中實(shí)現(xiàn);它現(xiàn)在已經(jīng)發(fā)展到HBM2技術(shù),新一代技術(shù)解決了原始HBM版本中的容量和時(shí)鐘速率限制問(wèn)題。

這是一張AMD演示的內(nèi)存架構(gòu)圖,我們可以清楚的看到HBM實(shí)際結(jié)構(gòu),尤其是四層DRAM疊在最底層die之上,雖然AMD一直也沒(méi)有給出HBM本體的具體制作過(guò)程,但是不難想象4層絕不是HBM未來(lái)發(fā)展的極限,而隨著層數(shù)的增加,位寬勢(shì)必還會(huì)迎來(lái)進(jìn)一步的遞增。

8、中介層

中介層用于多芯片模具或板子的封裝,相當(dāng)于一個(gè)導(dǎo)管,在一個(gè)封裝里通過(guò)電子信號(hào)實(shí)現(xiàn)傳導(dǎo)。通過(guò)中介層可以完成很多運(yùn)算和數(shù)據(jù)交流,相當(dāng)于連接多個(gè)芯片和同一電路板之間的橋梁。使系統(tǒng)更小,更省電,更大帶寬。它可以將信號(hào)傳播到更寬的中心間距,也可以將信號(hào)連接到主板上的不同溝槽上。

中介層可由硅和有機(jī)材料制成,作為多個(gè)模具、模具和基板之間的橋梁。Silicon interposer是一種成熟的技術(shù),由于其較高的I/O密度和TSV形成能力,它在2.5D和3D IC芯片封裝中發(fā)揮著關(guān)鍵作用。

9、再分配層(RDL)

再分配層是銅金屬連接線(xiàn)或封裝中電連接的一部分。再分配層是由金屬或聚合物介質(zhì)材料層創(chuàng)建,用于將模具堆疊在封裝上,以及提供通過(guò)interposer連接的芯片之間的通信,從而減輕大型芯片組的I/O間距。它們已經(jīng)成為2.5D和3D封裝解決方案中不可或缺的環(huán)節(jié)。

10、硅通孔(TSV)

TSV是2.5D和3D封裝解決方案中的關(guān)鍵實(shí)現(xiàn)技術(shù),它提供了通過(guò)模具硅片的垂直互連。它在里面填充了銅。TSV是一種通過(guò)整個(gè)芯片厚度的電子連接,它可以創(chuàng)建從芯片一側(cè)到另一側(cè)的最短路徑。

這些孔洞從晶圓片的正面蝕刻到一定深度,然后通過(guò)沉積導(dǎo)電材料(通常是銅)將它們隔離并填充。芯片制作完成后,晶圓從背面開(kāi)始變薄,露出晶圓背面的孔和金屬,以完成TSV互連。