從HBM存儲器到3D NAND芯片,硬件市場上有許多芯片是用英文稱為TSV構(gòu)建的,TSV是首字母縮寫,意為“通過硅通孔”并翻譯為via硅的事實(shí),它們垂直地穿過的芯片和允許在它們之間垂直互通。在本文中,我們將告訴您它們是什么,它們?nèi)绾喂ぷ饕约八鼈兊挠猛尽?/p>

在硬件世界中,經(jīng)常用與速度有關(guān)的術(shù)語來談?wù)撍词欠袷莾?nèi)存的帶寬,處理器的時(shí)鐘周期,處理器每秒執(zhí)行某種類型的計(jì)算的次數(shù)等等,但是我們很少問自己這些芯片如何相互通信以及這是否重要。

在本文中,我們將討論一種稱為TSV的技術(shù),該技術(shù)可用于相互通信的芯片。

什么是硅或TSV通路?

如果我們看大多數(shù)主板,可以看到兩件事:第一,芯片之間的大多數(shù)連接都是水平的,這意味著板上發(fā)送芯片間信號的路徑是水平通信的。

PCB

然后是CPU的情況,這些CPU放置在我們稱為插座的插入器的頂部,并且處理器在這些插入器上垂直連接。

SocketCPU

但是通常,在99%的時(shí)間中,我們觀察到通常沒有相互垂直連接的芯片,盡管事實(shí)上芯片和處理器的設(shè)計(jì)朝著這個(gè)方向發(fā)展,并且市場上已經(jīng)有這種類型的示例。但是,如何使兩個(gè)或更多芯片垂直互連?

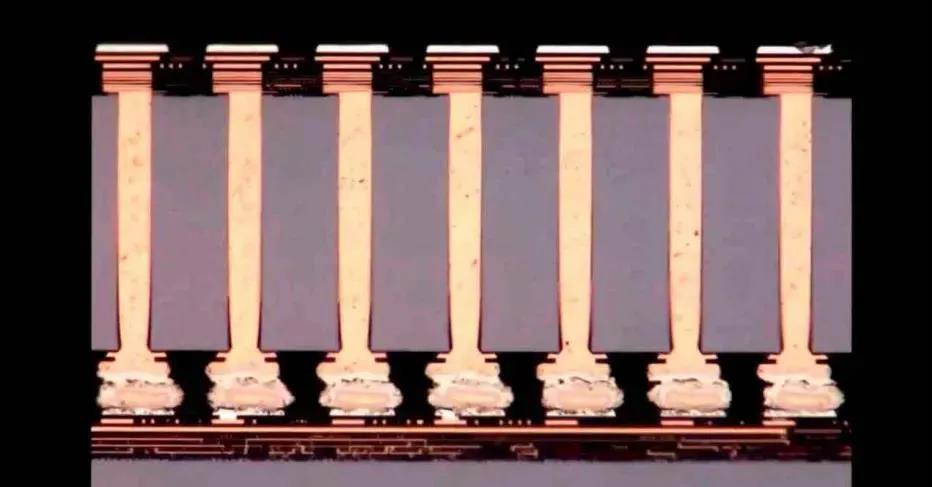

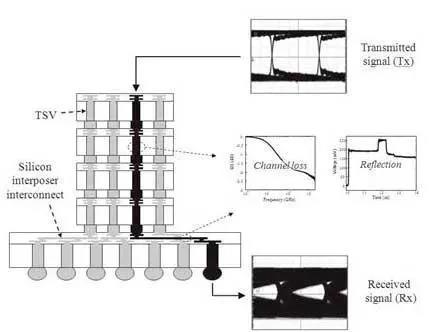

TSV

好吧,正是通過所謂的硅通道來完成的,硅通道垂直穿過組成堆棧的同一芯片的不同芯片或不同層,這就是為什么它們被稱為“通過”硅通道,因?yàn)樗鼈儗?shí)際上是通過的。

使用TSV的應(yīng)用和優(yōu)勢

TSV的應(yīng)用之一是,它允許將由不同部分組成的復(fù)雜處理器分離在幾個(gè)不同的芯片上,并具有以下附加優(yōu)點(diǎn):垂直連接允許更多數(shù)量的連接,這有助于實(shí)現(xiàn)更大的帶寬,而無需額外的帶寬。很高的時(shí)鐘頻率會增加數(shù)據(jù)傳輸期間的功耗。

例如,在將來,我們將看到CPU和GPU的最后一級緩存將不在芯片上,它們具有相同的帶寬,但存儲容量卻是原來的幾倍,這將大大提高性能。我們也有使用FSV來通信Lakefield SoC的兩個(gè)部分的Intel Foveros示例,即帶有系統(tǒng)I / O所在的基本芯片的計(jì)算芯片。

LakefieldFoveros

將處理器劃分為不同部分的原因是,隨著芯片的變大,電路中錯(cuò)誤的可能性越來越大,因此沒有故障的優(yōu)質(zhì)芯片的數(shù)量會增加。他們可以使用的更少,而那些做得好的人必須支付失敗者的費(fèi)用;這意味著從理論上減小芯片的尺寸會降低總體成本,盡管稍后我們將看到情況并非完全如此。

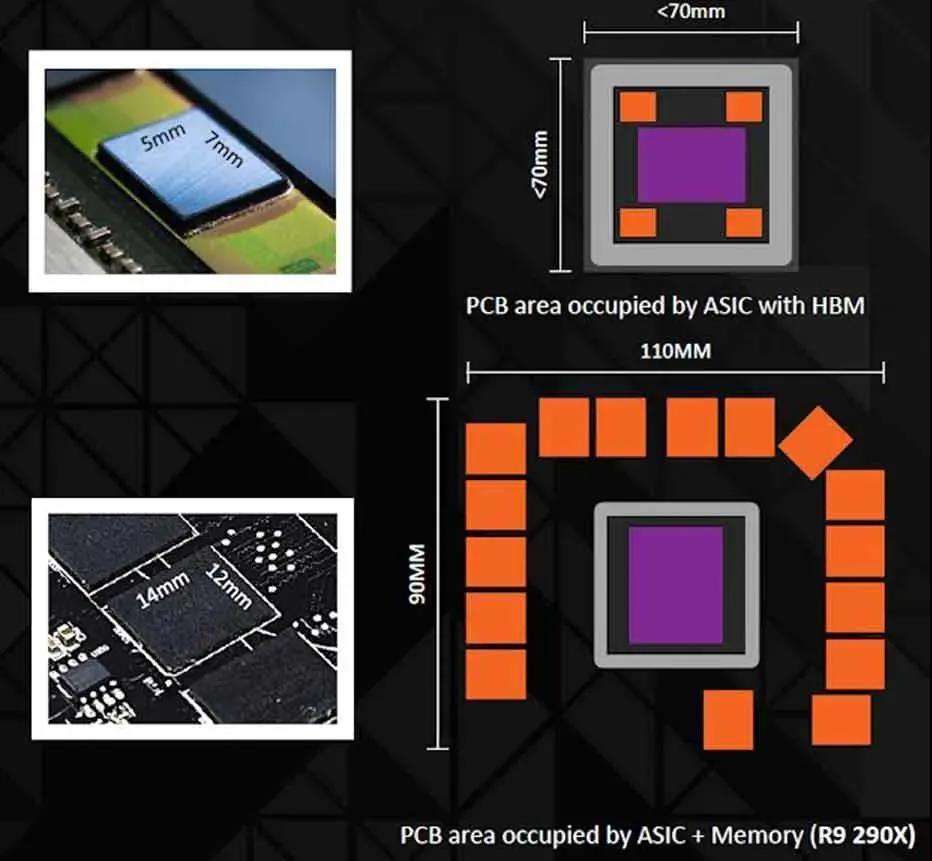

HBM-vs-GDDR

第二個(gè)應(yīng)用程序與占用的空間有關(guān);能夠垂直堆疊多個(gè)芯片的事實(shí)大大減少了它們占用的面積,因?yàn)樗鼈儾粫⒉荚诎迳希渲凶钪氖纠菍BM內(nèi)存用作某些圖形處理器的VRAM,但是我們還有其他示例,例如三星的V-NAND存儲器,將多個(gè)NAND閃存芯片彼此堆疊。

3DNAND

其他鮮為人知的選擇是邏輯和內(nèi)存的組合,其中內(nèi)存位于處理器的頂部,最著名的示例是寬I / O內(nèi)存,這是幾年前出現(xiàn)在智能手機(jī)中的一種內(nèi)存,包括SoC頂部的存儲器通過硅互連。

為什么采用硅途徑如此緩慢?

TSV存在一些固有的問題,這意味著盡管數(shù)十年來在紙上是一種非常有前途的技術(shù),但它并沒有完全普及,仍然是一種為很小的市場生產(chǎn)芯片但利潤率很高的方法。

他們的第一個(gè)問題是,要實(shí)施一項(xiàng)極其昂貴的技術(shù),需要對許多公司的生產(chǎn)線進(jìn)行深刻的變革,這些公司多年來一直在生產(chǎn)沒有TSV的芯片,并且對于許多應(yīng)用而言,傳統(tǒng)的制造工藝已被證明是足夠好的。

第二個(gè)問題是,如果組成垂直結(jié)構(gòu)的一部分完全失效,則必須丟棄整個(gè)結(jié)構(gòu),這會使通過TSV互連的系統(tǒng)制造起來更加昂貴。HBM內(nèi)存的示例在這方面意義重大,其成本如此之高,以致無法用作消費(fèi)市場的內(nèi)存。

第三個(gè)問題是熱阻塞,芯片在某些溫度條件下達(dá)到其時(shí)鐘速度,如果附近有另一個(gè)也會發(fā)熱的芯片會受到影響。例如,我們可能有兩個(gè)處理器,每個(gè)處理器分別達(dá)到1 GHz,但由于溫度問題,垂直放置在TSV結(jié)構(gòu)中的每個(gè)處理器只能達(dá)到0.8 GHz。

這是當(dāng)今工程師最關(guān)心的第三點(diǎn),并且正在開發(fā)冷卻機(jī)制,以使構(gòu)成堆棧的芯片保持盡可能低的溫度,以避免熱淹沒問題。