最近,美光已將其DRAM路線圖從三個單元縮減階段更新為四個階段,從而使每個芯片具有更大的DRAM容量并降低了每GB的成本。根據(jù)規(guī)劃,這家美國芯片制造商打算通過以下步驟逐步縮小單元或工藝節(jié)點的尺寸,從不再主流的20nm節(jié)點工藝尺寸到10nm(19nm-10nm范圍)節(jié)點工藝:

1Xnm –(c19-17nm)較早的DRAM技術處理節(jié)點大小

1Ynm –(c16-14nm)當今主流的DRAM位生產(chǎn)技術

1Znm –(c13-11mn)2020年第三季度,15%的美國DRAM位生產(chǎn)是在這個工藝完成

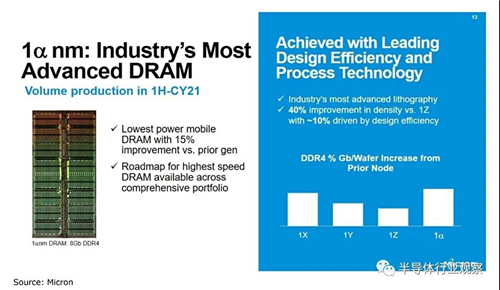

1αnm工藝節(jié)點– 1 alpha – 2021年上半年的量產(chǎn)

1βnm工藝節(jié)點– 1 beta –處于早期開發(fā)中

1納米工藝節(jié)點– 1gamma–早期工藝集成

1δnm工藝節(jié)點– 1delta–探索中,可能需要EUV技術

1 delta節(jié)點的大小是Micron DRAM路線圖中的一個新條目。我們沒有低于1Znm的指示性工藝節(jié)點尺寸。

美光表示,隨著從1Xnm到1Yn和1Znm的轉(zhuǎn)變,位密度的增長速度減慢了。但是,該公司加快了增長率,從1Znm到1αnm工藝節(jié)點尺寸增加了40%。

富國銀行分析師Aaron Rakers表示,美光在1Znm DRAM生產(chǎn)中擁有強大的地位。他引用研究公司DRAMeXchange的數(shù)據(jù),估計美光在2020年第三季度的1Znm產(chǎn)量占其DRAM位產(chǎn)量的15%,而三星和SK hynix分別為6%和0。

在其他條件相同的情況下,1Znm DRAM的制造成本低于之前的1Ynm節(jié)點。

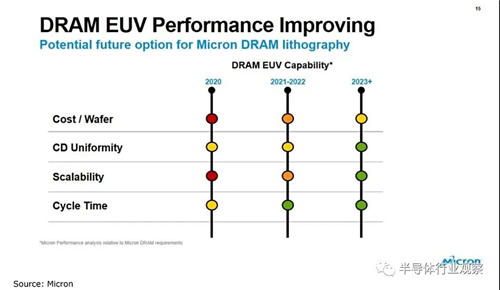

關于EUV的看法

美光采用深紫外線(DUV)多圖案光刻技術在晶圓上布置DRAM單元芯片細節(jié)。隨著工藝節(jié)點尺寸縮小到10nm單元尺寸水平以下,光束的波長成為一個約束。

ASML是芯片行業(yè)光刻機的主要供應商,已開發(fā)出發(fā)出較小波長光的EUV(極端紫外線)光刻機。這項技術可在晶圓上刻蝕較窄的線條,因此可實現(xiàn)更小的工藝尺寸,即晶圓上的DRAM裸片數(shù)量更多,因此每個晶圓的容量更高,每GB的成本更低。但是資本支出是巨大的。目前ASML每年僅生產(chǎn)30臺EUV光刻機,它們重180噸,每臺成本1.2億美元。

三星在1Znm工藝節(jié)點中就使用EUV,SK hynix計劃使用EUV技術批量生產(chǎn)1αnmDRAM和1βnmDRAM。美光認為EUV直到2023年或更晚才具有成本競爭力,這意味著他們將在1δnm工藝節(jié)點引入EUV。