先進(jìn)封裝在新型系統(tǒng)級(jí)芯片的開發(fā)中正在扮演著越來越重要的角色,并日益成為一種更加可行的解決方案。但是,對(duì)于芯片制造商來說,它提供的一系列選擇有時(shí)令人困惑,有時(shí)價(jià)格太高。

汽車、服務(wù)器、智能手機(jī)和一些其它高端系統(tǒng)已經(jīng)采用了某種形式的先進(jìn)封裝,而對(duì)于其它應(yīng)用來說,簡單的封裝技術(shù)就足夠了。盡管如此,先進(jìn)封裝正迅速成為吸引許多人的選擇。業(yè)界正在開發(fā)新形式的先進(jìn)級(jí)封裝技術(shù)或者對(duì)現(xiàn)有技術(shù)進(jìn)行升級(jí),以用于 5G 和 AI 等一系列新興應(yīng)用。

幾十年來,以一個(gè)基本形式的封裝把裸片組裝起來是可行的,但是,隨著芯片工藝尺寸的縮減走到了盡頭,封裝技術(shù)打開了另一個(gè)視角,它提供了一套全新的架構(gòu)選擇,既可以提高性能,又能降低功耗并為設(shè)計(jì)增加靈活性,從而既可以針對(duì)特定市場進(jìn)行定制,又可以縮短上市時(shí)間。

但是,沒有任何一種封裝類型可以滿足所有需求。每個(gè)應(yīng)用對(duì)封裝的要求都是不同的。在某些情況下,先進(jìn)包裝甚至可能不是正確的解決方案。

Semiconductor Engineering 研究了先進(jìn)封裝技術(shù)在四個(gè)主要市場中的優(yōu)勢和挑戰(zhàn):服務(wù)器、網(wǎng)絡(luò)設(shè)備、智能眼鏡和軍事 / 航空航天。盡管這里給出的只是先進(jìn)封裝技術(shù)可能應(yīng)用領(lǐng)域的若干示例,但是,這里的分析依然突顯了芯片制造商未來將在封裝方面面臨的一些主要問題和挑戰(zhàn)。

根據(jù) YoleDéveloppement 的數(shù)據(jù),2019 年整個(gè) IC 封裝市場的價(jià)值為 680 億美元。其中,先進(jìn)封裝的規(guī)模為 290 億美元,預(yù)計(jì)它將以增長 6.6%的速度增長,到 2025 年達(dá)到 420 億美元。

服務(wù)器領(lǐng)域

通常情況下,設(shè)備制造商依靠芯片工藝尺寸的縮減實(shí)現(xiàn)設(shè)計(jì)的升級(jí),其目標(biāo)是在每一代新工藝節(jié)點(diǎn)的單片芯片上封裝更多功能,新節(jié)點(diǎn)大約每 18 到 24 個(gè)月推出一次。但是現(xiàn)在,工藝尺寸的縮減變得越來越困難和昂貴,并且價(jià)格 / 性能優(yōu)勢正在減少。因此,盡管工藝尺寸依然將繼續(xù)縮減,但是,并非系統(tǒng)中的所有組件都按同樣的比例進(jìn)行縮減。

聯(lián)華電子業(yè)務(wù)發(fā)展副總裁 Walter Ng 說:“客戶需要更優(yōu)化的、提供更具成本效益的技術(shù)解決方案和業(yè)務(wù)解決方案。從上市時(shí)間的角度來看,在先進(jìn)節(jié)點(diǎn)上設(shè)計(jì)和驗(yàn)證大型片上系統(tǒng)(SoC)所花費(fèi)的時(shí)間也是一個(gè)不得不考慮的問題。”

圖源 | The Motley Fool

在服務(wù)器領(lǐng)域,它采取的方式是將不需要或者不能從中受益的功能從最先進(jìn)數(shù)字邏輯工藝上卸載下來,同時(shí)使用高速管芯對(duì)管芯互連的異構(gòu)集成,目前流行的方案是“小芯片”。

在小芯片中,芯片制造商可能有一個(gè)庫,庫中有一系列模塊化管芯或小芯片,這些模塊不需要都在同一工藝節(jié)點(diǎn)上開發(fā)。通常來說,包含小芯片的設(shè)計(jì)類似于單片 SoC,但是開發(fā)成本較低。

當(dāng)然,聽起來這種方法很好,但是它仍然存在一些挑戰(zhàn)。“這是一個(gè)新興的環(huán)境,是一種新模式。接口方面的標(biāo)準(zhǔn)不足。最早采用小芯片集成的公司往往是可以控制所有設(shè)計(jì)元素,特別是接口的垂直集成公司,” ASE 的業(yè)務(wù)開發(fā)高級(jí)總監(jiān) Eelco Bergman 在最近的 IMAPS2020 會(huì)議上的演講中說。“如今,小芯片設(shè)計(jì)將主要由芯片開發(fā)者推動(dòng),無論是 IDM 還是無晶圓廠供應(yīng)商。隨著行業(yè)的發(fā)展和生態(tài)系統(tǒng)的開放,您會(huì)看到這種變化。”

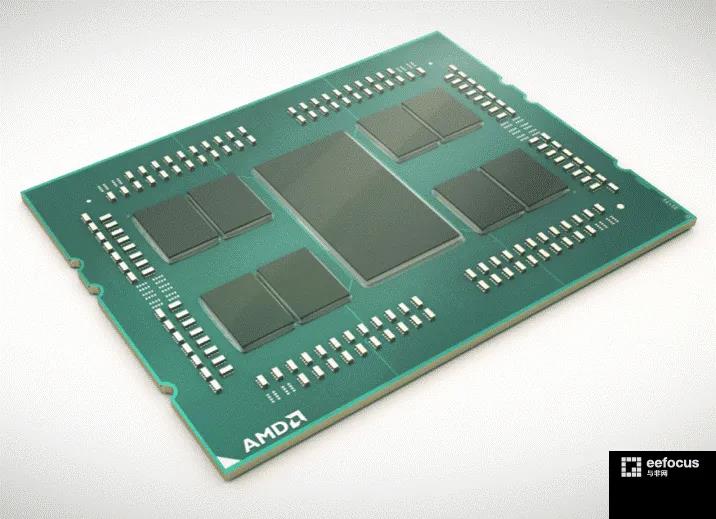

AMD、英特爾和其他一些公司已經(jīng)引入了類似小芯片的架構(gòu)。例如,AMD 最新的服務(wù)器處理器系列取代了大型的單芯片,它將較小的芯片集成到了一個(gè)模塊中,該模塊有時(shí)稱為多芯片模塊(MCM)。使用管芯到管芯互連來連接芯片。

AMD 的 MCM 被稱為 2D 小芯片設(shè)計(jì),它集成了基于 14nm 工藝的集成 I / O 和內(nèi)存控制器芯片,這個(gè) 14nm 的芯片在整個(gè)模塊的中間。MCM 中還集成了八個(gè) 7nm 處理器管芯。四個(gè)處理器管芯位于 I / O 管芯的每一側(cè)。

具有 8 個(gè)內(nèi)核芯片和 1 個(gè) I / O 芯片的 AMD EPYC 服務(wù)器

圖源 | AMD

AMD 的服務(wù)器處理器產(chǎn)品線轉(zhuǎn)向了類似小芯片的方案有幾個(gè)原因。“為了維持每兩年性能提升 2 倍的趨勢,我們需要使用小芯片技術(shù),不僅要以更高的良率集成更多的晶體管,還需要減少先進(jìn)工藝節(jié)點(diǎn)上的硅容量。”AMD 的高級(jí)研究員 Bryan Black 在一次演講表示。

展望未來,AMD 計(jì)劃在服務(wù)器處理器方面擴(kuò)大 MCM 的戰(zhàn)果。它還計(jì)劃使用 3D 堆疊技術(shù)開發(fā)小芯片。Black 說:“隨著我們進(jìn)入 3D 堆疊的世界,我們在 2D 世界面臨的所有挑戰(zhàn)都將加劇。”

最重要的是,封裝需要裸片具有適當(dāng)?shù)牧悸剩脖环Q為良品白片。封裝中有一個(gè)壞晶粒就可能導(dǎo)致產(chǎn)品或系統(tǒng)故障。“所有裸片都有參數(shù)變化。因此,我們會(huì)遇到多管芯解決方案的基本測試和特征化問題。有些管芯速度很慢,有些很快,有些消耗的電量更多,有些消耗的電量更少。”Black 說。

熱量、功率分配和可靠性也是基于小芯片設(shè)計(jì)的挑戰(zhàn)。然后,如果封裝失敗了,那么最大的問題就是誰來負(fù)責(zé)。是芯片供應(yīng)商、IP 供應(yīng)商還是封裝廠?

在這方面,封裝行業(yè)可以借鑒過去的經(jīng)驗(yàn),尤其是 2.5D 早期階段。使用 2.5D 時(shí),管芯堆疊或并排放置在中介層的頂部。中介層結(jié)合了硅通孔(TSV),充當(dāng)芯片和電路板之間的橋梁。

在 2.5D 的早期階段,設(shè)備制造商一直在努力應(yīng)對(duì)不同的管芯、集成問題和成品率挑戰(zhàn)。但是,隨著時(shí)間的流逝,供應(yīng)商解決了這些問題。

如果管芯不符合規(guī)格,供應(yīng)商將對(duì)器件進(jìn)行廣泛的根本原因分析。這需要一個(gè)完善的測試策略。

網(wǎng)絡(luò)設(shè)備領(lǐng)域

網(wǎng)絡(luò)設(shè)備供應(yīng)商也面臨許多相同的挑戰(zhàn)。網(wǎng)絡(luò)是一個(gè)復(fù)雜的系統(tǒng),覆蓋從家庭辦公室到云的廣泛范圍。為了應(yīng)對(duì)這些市場,通信設(shè)備供應(yīng)商針對(duì)網(wǎng)絡(luò)的各個(gè)子市場出售不同的系統(tǒng)。

例如,在網(wǎng)絡(luò)的一部分中,思科為大型服務(wù)提供商出售路由器。路由器使用 IP 數(shù)據(jù)包進(jìn)行網(wǎng)絡(luò)定向。思科最新的路由器基于其自研的 ASIC。思科的單片 ASIC 圍繞 7 納米工藝構(gòu)建,可在同一芯片上實(shí)現(xiàn) 12.8 Tbps 的帶寬。

圖源 | chainbulletin.com

思科還為其它網(wǎng)絡(luò)產(chǎn)品開發(fā) ASIC,其他通信設(shè)備供應(yīng)商也開發(fā)自家的 ASIC。

出于多種原因,供應(yīng)商也在探索或?qū)嵤┨娲椒āT诿總€(gè)節(jié)點(diǎn)上,ASIC 變得越來越大,越來越昂貴。它還集成了 SerDes(串行器 / 解串器),可提供高速的芯片到芯片通信。

Juniper 的資深工程師 Valery Kugel 在演講中說:“網(wǎng)絡(luò)帶寬擴(kuò)展的要求導(dǎo)致每一代技術(shù)的聯(lián)網(wǎng) ASIC 裸片尺寸都會(huì)增加。(SerDes)占據(jù)了 ASIC 的很大一部分。”

還有一些其它的問題。ASIC 由數(shù)字和模擬模塊組成。數(shù)字部分可以得益于工藝的升級(jí),可在更高帶寬下實(shí)現(xiàn)更多功能。但是,并非所有事情都能從工藝縮減中受益。

“SerDes 功能不能受益于工藝縮減,它是一個(gè)模擬結(jié)構(gòu),無法很好地?cái)U(kuò)展。” TE Connectivity 的技術(shù)專家兼行業(yè)標(biāo)準(zhǔn)經(jīng)理內(nèi)森·特雷西(Nathan Tracy)說。Tracy 還是行業(yè)標(biāo)準(zhǔn)組織光學(xué)互聯(lián)網(wǎng)絡(luò)論壇(OIF)的主席。

這里有包括小芯片在內(nèi)的幾種解決方案。為了將芯片連接到封裝中,OIF 正在開發(fā)一種稱為 CEI-112G-XSR 的芯片對(duì)芯片接口標(biāo)準(zhǔn)。XSR 連接 MCM 中的小芯片和光學(xué)引擎。它可通過短距離鏈路實(shí)現(xiàn)高達(dá) 112Gbps 的數(shù)據(jù)速率,目前該 XSR 標(biāo)準(zhǔn)仍處于草稿階段。

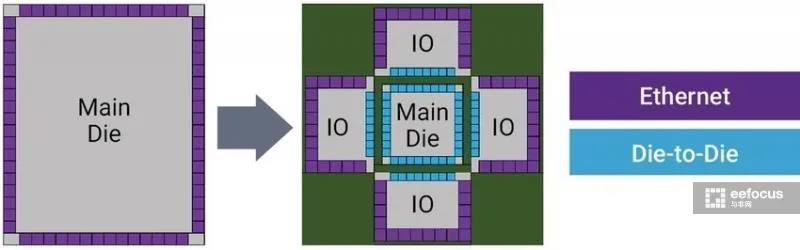

有幾種方法可以在網(wǎng)絡(luò)設(shè)備中實(shí)現(xiàn)小芯片和 XSR。例如,大型 ASIC 分為兩個(gè)較小的管芯,這些管芯使用 XSR 鏈接進(jìn)行連接。

在另一個(gè)示例中,大型 SerDes 模塊被分解為四個(gè)較小的 I / O 芯片。然后,在 MCM 中,ASIC 位于中間,中間被四個(gè)較小的 I / O 小芯片包圍。

需要管芯到管芯連接的以太網(wǎng)交換機(jī) SoC 的示例

圖源 | Synopsys

另外,設(shè)備制造商可以將光學(xué)引擎與 MCM 中的交換芯片 ASIC 集成在一起。

特雷西說:“業(yè)界對(duì)于和光學(xué)器件共同封裝的討論很多。我在這里說的是,從交換機(jī)面板上的可插拔光收發(fā)器轉(zhuǎn)移到直接將光學(xué)引擎安裝在交換機(jī) SoC 上的可能性。您需要一個(gè)低功耗的高速互連。討論的重點(diǎn)是 OIF 的 XSR 開發(fā)。”

小芯片的采用將取決于具體應(yīng)用。在某些情況下,ASIC 仍然是有意義的。這里有幾個(gè)因素,例如成本和產(chǎn)量。特雷西說:“這一切都是為了減少功耗。”

智能眼鏡領(lǐng)域

圖源 | www.ebay.com

這些解決方案可能適用于網(wǎng)絡(luò)設(shè)備,但是消費(fèi)市場有不同的要求,尤其是對(duì)于新興產(chǎn)品而言。

例如,在研發(fā)方面,多家公司正在開發(fā)下一代智能眼鏡或 AR / VR 眼鏡。虛擬現(xiàn)實(shí)(VR)使用戶可以體驗(yàn) 3D 虛擬環(huán)境。增強(qiáng)現(xiàn)實(shí)(AR)能夠獲取計(jì)算機(jī)生成的圖像,并將其覆蓋在系統(tǒng)上。

如果這項(xiàng)技術(shù)可行,AR / VR 眼鏡可以用于數(shù)據(jù)檢索、面部識(shí)別、游戲和語言翻譯。他們還可以將演示文稿或鍵盤投影在表面上。

Facebook Reality Labs 的主任兼研究科學(xué)家 Liu Chiao 在去年 IEDM 上的一篇論文中表示:“ [AR / VR]及其變體設(shè)備只是下一代計(jì)算平臺(tái)之旅的開始。”

開發(fā)一副有用且便宜的智能眼鏡并不是一件簡單的任務(wù)。這些產(chǎn)品需要新的低功耗芯片、顯示器和接口。在這些眼鏡中,使用語音、視線和頭部 / 身體移動(dòng)來激活程序。所有這些技術(shù)都必須是安全的。

“我們將需要全面的大幅度改進(jìn),” Facebook 的硅工程主管 Ron Ho 在 IMAPS2020 的演講中說。“相對(duì)于功率,我需要的性能要比當(dāng)今系統(tǒng)的性能高得多。通常,我需要以較低的延遲更快地運(yùn)行事情。”

為了以合適的尺寸實(shí)現(xiàn)智能眼鏡,IC 封裝是關(guān)鍵。Ho 說:“我必須管理能夠提高性能和降低延遲的封裝。您不能強(qiáng)迫芯片在 PCIe 上經(jīng)過多英寸的走線并消耗大量功率。但是,您可以將它們共同封裝在一起,然后放在彼此旁邊。通過 TSV,它們具有更高的帶寬和更高的性能連接。”

在 IEDM 上,F(xiàn)acebook 披露了有關(guān)其 AR / VR 眼鏡的一些線索,這些眼鏡正在研發(fā)中。Facebook 在一篇論文中概述了用于 AR / VR 眼鏡的計(jì)算機(jī)視覺接口技術(shù)的發(fā)展。其底層技術(shù)是一種先進(jìn)的 CMOS 圖像傳感器。

CMOS 圖像傳感器在智能手機(jī)和其他產(chǎn)品中提供相機(jī)功能。但是標(biāo)準(zhǔn)的圖像傳感器不足以用于 AR / VR 眼鏡。這里需要的是具有先進(jìn)封裝的機(jī)器感知優(yōu)化圖像傳感器。Facebook 在論文中描述了一種三層圖像傳感器。第一層是具有處理單元的圖像傳感器,其后是聚合處理器,然后是云計(jì)算平臺(tái)。

Facebook 還提到了銅混合鍵合技術(shù)。使用銅 - 銅擴(kuò)散鍵合技術(shù)將管芯堆疊并連接。目前尚不清楚 Facebook 是否會(huì)走這條路,但是混合鍵合是圖像傳感器領(lǐng)域的一項(xiàng)已知技術(shù)。

軍事 / 航空領(lǐng)域

同時(shí),幾十年來,美國國防部(DoD)認(rèn)識(shí)到芯片技術(shù)對(duì)于保持美國的軍事優(yōu)勢至關(guān)重要。國防界在各種系統(tǒng)中使用各種高級(jí)節(jié)點(diǎn)和成熟節(jié)點(diǎn)上的芯片。封裝也是很關(guān)鍵的一部分。

軍事 / 航空航天涉及眾多具有不同要求的客戶,當(dāng)然這里有一些共同的主題。Quik-Pak 的 Molitor 說:“我們?yōu)樵S多不同領(lǐng)域提供服務(wù)。我們也為軍用 / 航空業(yè)服務(wù)。軍事 / 航空計(jì)劃往往是長期存在的。它們習(xí)慣于處理必須工作 20 到 30 年的組件。”

軍用 / 航空客戶面臨其他挑戰(zhàn)。與商業(yè)領(lǐng)域一樣,開發(fā)先進(jìn)芯片的成本昂貴,但每次節(jié)點(diǎn)升級(jí)帶來的收益卻在減小。另外,對(duì)于國防界而言,對(duì)芯片產(chǎn)量的需求相對(duì)較少。

有時(shí),國防界使用非美國本土的代工廠獲得先進(jìn)工藝的芯片,但出于安全目的,它更傾向于使用本土供應(yīng)商。軍用 / 航空業(yè)客戶希望獲得可信賴且有保證的芯片和封裝供應(yīng)鏈。

盡管如此,國防部仍在尋找芯片工藝升級(jí)以外的替代方法,即異構(gòu)集成和小芯片。

圖源 | theburnin.com

例如,英特爾最近獲得了國防部小芯片的新合同,稱為先進(jìn)異構(gòu)集成原型(SHIP)項(xiàng)目。根據(jù)該計(jì)劃,英特爾圍繞小芯片建立了一個(gè)新的美國商業(yè)實(shí)體。該計(jì)劃使國防部和國防行業(yè)的客戶可以使用英特爾的封裝技術(shù)。

SHIP 計(jì)劃包含多個(gè)部分。英特爾贏得了該計(jì)劃的數(shù)字組件合同,Qorvo 則拿下了 SHIP 計(jì)劃的 RF 組件合同。在該項(xiàng)目下,Qorvo 將在德克薩斯州建立一個(gè)射頻異構(gòu)封裝設(shè)計(jì)、生產(chǎn)和原型制作中心。該中心將主要為國防行業(yè)服務(wù)。

Qorvo 對(duì)軍事 / 航空行業(yè)并不陌生。多年來,這家 RF 器件和其他產(chǎn)品的供應(yīng)商一直為軍事 / 航空和商業(yè)領(lǐng)域提供芯片制造和封裝服務(wù)。該公司開發(fā)了基于氮化鎵(GaN)、砷化鎵(GaAs)和其他工藝的器件。

根據(jù) SHIP 計(jì)劃,Qorvo 將使用基于氮化鎵、砷化鎵和硅器件提供異構(gòu)封裝服務(wù)。目的是滿足國防部所稱的 SWAP-C(這是一個(gè)首字母縮寫,表示相控陣?yán)走_(dá)系統(tǒng)、無人駕駛車輛、電子戰(zhàn)平臺(tái)和衛(wèi)星等各種應(yīng)用)中的尺寸、重量、功率和成本要求。

盡管 Qorvo 將提供一站式服務(wù),但 SHIP 計(jì)劃主要是針對(duì)封裝的。它將繼續(xù)為軍事 / 航空客戶提供芯片制造和封裝服務(wù)。“我們使用自己的代工模型為之建模。我們使用的是同一種開放獲取型的模型。這將是一項(xiàng)服務(wù),您可以在我們的代工廠中進(jìn)行設(shè)計(jì),然后再考慮使用我們的封裝技術(shù)來封裝這些零部件,因此,SHIP 計(jì)劃是對(duì)我們現(xiàn)有能力的補(bǔ)充或擴(kuò)展。”White 說。

同時(shí),軍事 / 航空行業(yè)涉及到定制化的工作。每個(gè)客戶可能有不同的封裝要求,并面臨各種挑戰(zhàn)。

以 RF 為例。White 說:“ RF 行業(yè)面臨的挑戰(zhàn)之一是,一旦將器件放入封裝中,就會(huì)改變 RF 性能。您必須設(shè)計(jì)芯片和 MMIC 使其適合這些封裝,并使其性能盡可能接近其最初的預(yù)期性能。”

寫在最后

預(yù)計(jì)還有許多其它市場將推動(dòng)更加異構(gòu)的集成。蘋果公司的低端 Mac 計(jì)算機(jī)正在轉(zhuǎn)向內(nèi)部開發(fā)的 M1 處理器,該處理器將 CPU 核心、圖形和機(jī)器學(xué)習(xí)引擎集成在“定制封裝”中。

現(xiàn)在,一切才剛剛開始。在其它市場(例如 5G、人工智能、移動(dòng)設(shè)備)中,存在許多新的封裝機(jī)會(huì),并且伴隨著許多挑戰(zhàn)。但是,在市場發(fā)生新的重大變化的情況下,似乎從來都不缺少使行業(yè)從業(yè)者忙碌起來的機(jī)會(huì)。