本文概要

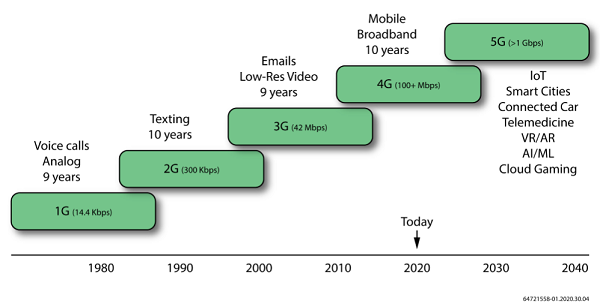

了解網(wǎng)絡(luò)基礎(chǔ)設(shè)施功能迅速增長的一種便捷方法是回顧一下過去四十年的發(fā)展歷程(如下圖所示)。蜂窩網(wǎng)絡(luò)技術(shù)的創(chuàng)新,加上新型的數(shù)據(jù)存儲和搜索技術(shù),正在轉(zhuǎn)變行業(yè)的發(fā)展模式。創(chuàng)新的技術(shù)不僅為公司和個(gè)人提供了全新的應(yīng)用場景,也使他們?nèi)フJ(rèn)真思考如何利用那些原本不屬于其產(chǎn)品組合的技術(shù)。也許最能說明問題的變化的是新的商業(yè)模式導(dǎo)致了價(jià)值從基礎(chǔ)設(shè)施轉(zhuǎn)向了服務(wù)。

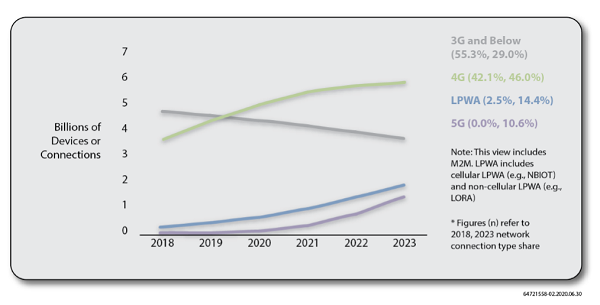

聯(lián)網(wǎng)設(shè)備正在從2G向5G演進(jìn),以支持移動應(yīng)用的爆發(fā),并為不斷增長的用戶群擴(kuò)展連接。一個(gè)日趨成熟的行業(yè)需要一種具有競爭力的商業(yè)模式,而這種模式可以被詮釋為優(yōu)化帶寬管理。據(jù)估計(jì),到2023年,聯(lián)網(wǎng)設(shè)備的數(shù)量將超過全球人口的三倍(如圖1所示)。

圖1:網(wǎng)絡(luò)基礎(chǔ)設(shè)施的演進(jìn)

Voice calls: 語音通話

Analog: 模擬

9 years: 9年

Texting: 發(fā)送短信

10 years: 10年

Emails: 電子郵件

Low-Res Video: 低分辨率視頻

Mobile Broadband:移動寬帶

IoT: 物聯(lián)網(wǎng)

Smart Cities: 智慧城市

Connected Car: 聯(lián)網(wǎng)汽車

Telemedicine: 遠(yuǎn)程醫(yī)療

VR/AR: 虛擬現(xiàn)實(shí)/增強(qiáng)現(xiàn)實(shí)

AI/ML: 人工智能/機(jī)器學(xué)習(xí)

Cloud Gaming: 云游戲

圖2:全球移動設(shè)備和連接增長(來源:思科)

Billions of Devices or Connections: 數(shù)十億的設(shè)備或連接

3G and Below (55.3%, 29.0%): 3G及以下(55.3%,29.0%)

LPWA (2.5%, 14.4%): 低功耗廣域技術(shù)(2.5%,14.4%)

注:此圖表包括M2M。LPWA包括蜂窩LPWA(例如NB-IoT)和非蜂窩LPWA(例如LoRa)

*數(shù)據(jù)(n)為2018 - 2023年網(wǎng)絡(luò)連接類型份額

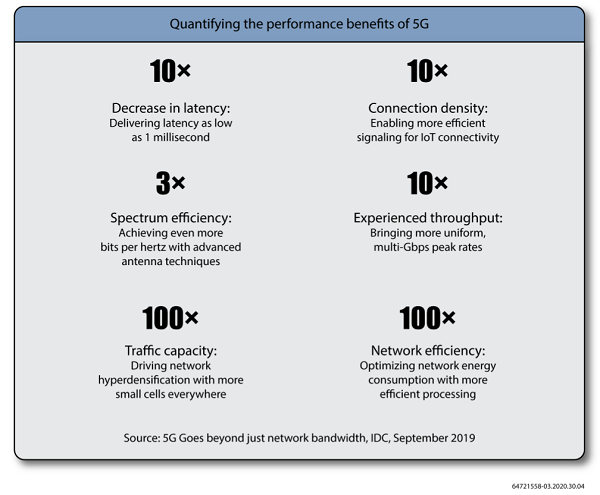

5G的興起和數(shù)據(jù)中心的重構(gòu)將更好和更多地集成和應(yīng)用加速技術(shù),這給通信和網(wǎng)絡(luò)設(shè)計(jì)人員帶來了巨大的壓力,要求他們?nèi)ゴ蛟烀棵肟商幚砗娃D(zhuǎn)發(fā)萬億字節(jié)數(shù)據(jù)的系統(tǒng)。這些新的系統(tǒng)不僅必須要具備高度可靠性,而且還需要滿足人類思維級別的響應(yīng)時(shí)間,以確保嚴(yán)格的性能保證(如圖3所示),這就需要全新的架構(gòu)。

盡管可編程邏輯提供了最佳的功能組合,以支持新一代通信和網(wǎng)絡(luò)系統(tǒng)的復(fù)雜需求,但是傳統(tǒng)的可編程芯片產(chǎn)品無法滿足這些需求。為了平衡片上的處理、互連和外部I / O,必須對整個(gè)FPGA架構(gòu)進(jìn)行重新考慮。需要最先進(jìn)的片上網(wǎng)絡(luò)(NoC)和總線布線能力,來實(shí)現(xiàn)所需的帶寬和性能。集成的NoC是唯一可行的方法來構(gòu)建可支持高效計(jì)算、巨大數(shù)據(jù)吞吐量和深度內(nèi)存層次結(jié)構(gòu)的系統(tǒng)。大規(guī)模的并行性與FPGA獨(dú)特的卸載和加速功能相結(jié)合,以實(shí)現(xiàn)單位功耗可實(shí)現(xiàn)的最高的性能和最高的性價(jià)比。

圖3:5G性能指標(biāo)

Quantifying the performance benefits of 5G

量化5G的性能優(yōu)勢

10XDecrease in latency: Delivering latency as low as 1 millisecond

延遲降低10倍:提供低至1毫秒的延遲

10XConnection density: Enabling more efficient signaling for IoT connectivity

10倍的連接密度:為物聯(lián)網(wǎng)連接提供更高效的信令服務(wù)

3XSpectrum efficiency:Achieving even more bits per hertz with advanced antenna techniques

3倍的頻譜效率:借助先進(jìn)的天線技術(shù)來實(shí)現(xiàn)更高的比特/赫茲比率

10XExperienced throughput: Bringing more uniform, multi-Gbps peak rates

10倍的可體驗(yàn)吞吐量:帶來更均勻的、多Gbps的峰值速率

100XTraffic capacity: Driving network hyperdensification with more small cells everywhere

100倍的數(shù)據(jù)流容量:通過遍布各地的更多小基站來推動網(wǎng)絡(luò)超高密集化

100XNetwork efficiency: Optimizing network energy consumption with more efficient processing

100倍的網(wǎng)絡(luò)效率:通過更高效的處理方式來優(yōu)化網(wǎng)絡(luò)能耗

不斷變化的網(wǎng)絡(luò)技術(shù)格局

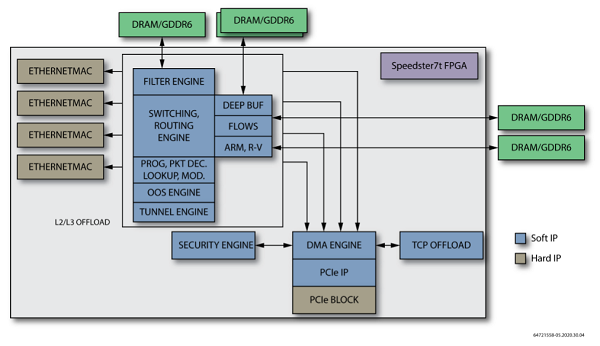

對由高帶寬連接提供的先進(jìn)服務(wù)的需求正在重塑通信和網(wǎng)絡(luò)領(lǐng)域。數(shù)據(jù)中心、邊緣系統(tǒng)和接入設(shè)備中的新型應(yīng)用正在推動對傳輸海量數(shù)據(jù)的需求,但同時(shí)又要滿足嚴(yán)格的延遲要求。FPGA正在成為所有實(shí)際網(wǎng)絡(luò)的核心,如下面的圖4所示。

圖4:各種實(shí)際網(wǎng)絡(luò)中的FPGA

例如,為了支持諸如增強(qiáng)現(xiàn)實(shí)和機(jī)器人控制等應(yīng)用,與之前的蜂窩無線通信技術(shù)相比,5G基站及其背后的網(wǎng)絡(luò)設(shè)備必須保證極低的延遲。這項(xiàng)要求同時(shí)還與對更高的每用戶吞吐量需求相伴而來,因而它們利用了多種不同的技術(shù),包括多天線、波束成形以及作為網(wǎng)絡(luò)密集化進(jìn)程的一部分而增加使用的小基站。所有這些因素都導(dǎo)致了在集中式基帶單元中進(jìn)行更密集的處理,這些基帶單元通過光纖鏈路與多個(gè)遠(yuǎn)程射頻單元進(jìn)行協(xié)同。

智能網(wǎng)卡(SmartNIC)的興起

運(yùn)營商已經(jīng)采用了諸如軟件驅(qū)動網(wǎng)絡(luò)(SDN)和網(wǎng)絡(luò)功能虛擬化(NFV)等技術(shù)來提高其系統(tǒng)的響應(yīng)能力。為了運(yùn)行這些服務(wù),數(shù)據(jù)中心所有者正在為其服務(wù)器添加智能網(wǎng)卡(SmartNIC),以便將許多網(wǎng)絡(luò)功能有效地卸載到加速器上。

智能網(wǎng)卡能夠處理傳入和傳出服務(wù)器的大部分?jǐn)?shù)據(jù)流,只有在需要處理異常情況時(shí),才會請求核心服務(wù)器上的處理器來提供幫助。借助足夠的加速功能,此類智能網(wǎng)卡能夠以線速度執(zhí)行一系列服務(wù)。這些服務(wù)范圍從對傳輸中的數(shù)據(jù)進(jìn)行壓縮到詳細(xì)的數(shù)據(jù)流控制,再到能夠檢測異常和可能的安全漏洞的深度數(shù)據(jù)包檢查應(yīng)用。隨著智能網(wǎng)卡技術(shù)的成熟,正在考慮引入諸如機(jī)器學(xué)習(xí)等越來越先進(jìn)的功能,以最大程度地發(fā)揮數(shù)據(jù)流和數(shù)據(jù)包分析的潛力。下面的圖5顯示了智能網(wǎng)卡的一些功能。

圖5:智能網(wǎng)卡功能原理圖

對傳輸高速數(shù)據(jù)和快速響應(yīng)不斷變化的條件的需求,要求系統(tǒng)能夠同時(shí)處理高吞吐量和低延遲。在傳統(tǒng)的架構(gòu)中,很難同時(shí)滿足這兩個(gè)要求。現(xiàn)在,基于微處理器的架構(gòu)集成了高度并行化的流水線,能夠處理高帶寬數(shù)據(jù)。但由于需要不斷地將數(shù)據(jù)從復(fù)雜的內(nèi)存體系結(jié)構(gòu)中傳入和傳出,結(jié)果使得確保低延遲變得極其困難。即使借助于專用的卸載處理器,智能網(wǎng)卡也面臨著由不斷增加的數(shù)據(jù)速率和延遲要求所帶來的挑戰(zhàn)。

應(yīng)對智能網(wǎng)卡設(shè)計(jì)的挑戰(zhàn)

在傳統(tǒng)的FPGA架構(gòu)中,用戶需要設(shè)計(jì)電路來連接加速器,從而導(dǎo)致不理想的布局和布線。更新的FPGA架構(gòu)使用了一種網(wǎng)絡(luò),在邏輯陣列內(nèi)的處理單元與各種片上高速接口和內(nèi)存端口之間傳輸數(shù)據(jù)(如下面的圖6所示)。

圖6:在傳統(tǒng)的FPGA架構(gòu)中連接加速器

Status Control: 狀態(tài)控制

Parameters: 參數(shù)

Accelerator: 加速器

Address decode and routing: 地址解碼和布線

Back pressure: 背壓

Request arbitration: 請求仲裁

Response arbitration: 響應(yīng)仲裁

Response back pressure: 響應(yīng)背壓

Response routing: 響應(yīng)布線

圖7:先進(jìn)的FPGA減少了所需電路的數(shù)量

硬連線架構(gòu)極大地改善了處理的延遲和能效,但是缺乏應(yīng)對需求變化的靈活性。對于數(shù)據(jù)壓縮和加密等應(yīng)用,數(shù)據(jù)中心運(yùn)營商希望能夠接納算法的改進(jìn),并更加容易地應(yīng)對不斷變化的威脅態(tài)勢。對加速器進(jìn)行(重新)編程以適應(yīng)這些變化的能力是一個(gè)關(guān)鍵的需求。一種能夠?qū)崿F(xiàn)這種重新編程的方法是通過部分重新配置,利用內(nèi)置的地址轉(zhuǎn)換表來簡化實(shí)現(xiàn)(如下面的圖8所示)。

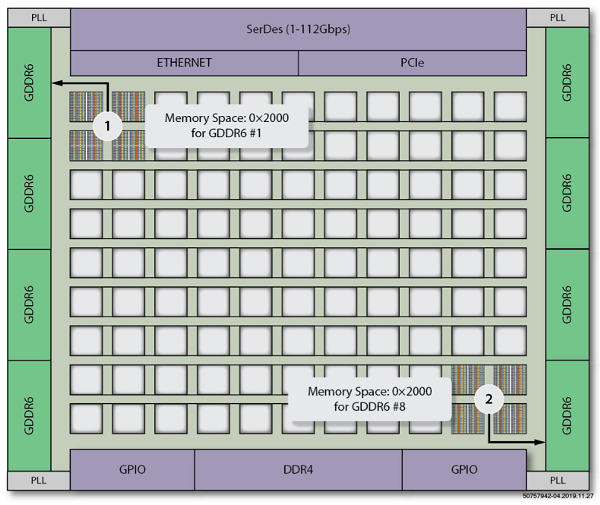

圖8:Speedster7t器件中的地址轉(zhuǎn)換表

Memory Space: 存儲空間

一種可編程邏輯架構(gòu)為實(shí)現(xiàn)靈活的控制和數(shù)據(jù)流結(jié)構(gòu)提供了堅(jiān)實(shí)的基礎(chǔ),從而可以為諸如數(shù)據(jù)包處理等多種通信操作提供高吞吐量。但是其他FPGA架構(gòu)中的傳統(tǒng)方法仍然受到了許多限制,難以達(dá)到下一代5G和數(shù)據(jù)中心網(wǎng)絡(luò)設(shè)備所需的性能等級。

Achronix Speedster7t系列FPGA通過一種平衡的架構(gòu)克服了這些限制,其結(jié)果是在計(jì)算密度和數(shù)據(jù)傳輸能力上都有重大改進(jìn)。

Speedster7t系列中的第一款FPGA器件AC7t1500提供了一系列高速接口,包括可分段(fracturable)以太網(wǎng)控制器(支持高達(dá)400G的速率)、PCI Gen 5端口和多達(dá)32個(gè)SerDes通道,其速率高達(dá)112 Gbps。AC7t1500器件是首款部署多通道GDDR6存儲器接口的FPGA,它滿足了需要高速緩存海量數(shù)據(jù)和存儲大型查找表的通信系統(tǒng)的需求。除了可編程邏輯架構(gòu)采用的面向位(bit-oriented)的布線結(jié)構(gòu)外,這些外圍設(shè)備還通過一個(gè)智能二維片上網(wǎng)絡(luò)(NoC)進(jìn)行互連。因此,Speedster7t FPGA是第一款能夠?qū)崿F(xiàn)太比特以太網(wǎng)(TbE)交換功能的器件,對于數(shù)據(jù)中心、網(wǎng)絡(luò)和電信基礎(chǔ)設(shè)施提供商來說,這是一項(xiàng)關(guān)鍵的賦能技術(shù)。

這種架構(gòu)使得網(wǎng)絡(luò)設(shè)計(jì)再向前更進(jìn)一步成為了可能。例如,它集成的面向矩陣的算術(shù)單元可實(shí)現(xiàn)網(wǎng)絡(luò)內(nèi)機(jī)器學(xué)習(xí)。使用諸如深度學(xué)習(xí)或更簡單的統(tǒng)計(jì)技術(shù)等技術(shù),網(wǎng)絡(luò)設(shè)備可以分析數(shù)據(jù)流量模式,以觀察和增強(qiáng)通過網(wǎng)絡(luò)的數(shù)據(jù)包流量,并對不斷變化的情況作出快速反應(yīng)。

針對性能而優(yōu)化的Speedster7t架構(gòu)

在通信和網(wǎng)絡(luò)中,對任何FPGA的關(guān)鍵要求是支持最新協(xié)議的密集I / O需求。Speedster7t系列FPGA通過在器件的I / O環(huán)中實(shí)現(xiàn)的全套硬件I / O控制器來滿足了這一需求,包括400G以太網(wǎng)、PCI Gen 5和GDDR6接口。

為了避免由于需要將一些核心功能置入可編程邏輯而造成的瓶頸,Speedster7t FPGA提供了完整的400 Gbps以太網(wǎng)MAC。這些MAC處理前向糾錯(FEC),支持400G配置的4×100G和8×50G選項(xiàng)。但是要充分利用這些功能,F(xiàn)PGA架構(gòu)還需要更多的東西 —— 一個(gè)能釋放其全部性能的互連框架。

通常來講,F(xiàn)PGA已經(jīng)使用了通過可編程互連來實(shí)現(xiàn)的超寬總線,以使高速串行通道與內(nèi)核中可編程邏輯的處理能力相匹配。互連矩陣的可任意編程性質(zhì)限制了數(shù)據(jù)在邏輯模塊之間的傳輸速度。為了彌補(bǔ)這種速度上的代價(jià),從事網(wǎng)絡(luò)類設(shè)計(jì)的FPGA用戶經(jīng)常采用極寬的總線——通常寬達(dá)1024位——這些總線是由面向位的互連矩陣匯聚合成。例如,在傳統(tǒng)的FPGA架構(gòu)中,為實(shí)現(xiàn)400Gbps所需的總線寬度將需要2048位(運(yùn)行速率為642MHz),或1024位(運(yùn)行速率為724MHz)。如此寬的總線難以布線,因?yàn)樗鼈儠腇PGA架構(gòu)內(nèi)大量的布線資源。其結(jié)果是,即使在最先進(jìn)的FPGA中,也不太可能用所需的時(shí)鐘速率來處理輸入數(shù)據(jù)并實(shí)現(xiàn)時(shí)序收斂。

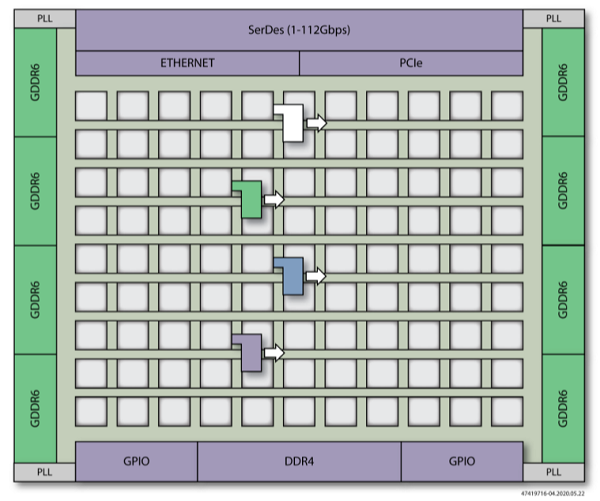

Speedster7t架構(gòu)通過提供一個(gè)聚合帶寬可高達(dá)20 Tbps的多級NoC層級化結(jié)構(gòu),消除了由于需要將高速I/O通道直接連接到以較低時(shí)鐘速率運(yùn)行的可編程邏輯所造成的瓶頸。與采用FPGA邏輯陣列實(shí)現(xiàn)互連方式相比,NoC不僅在速度上有了巨大的提升,而且NoC還能夠在不消耗任何FPGA可編程資源的情況下傳輸大量的數(shù)據(jù)。內(nèi)部NoC不僅提供了更高的帶寬,Speedster7t系列FPGA中的智能連接機(jī)制還簡化了將數(shù)據(jù)從NoC端口傳輸?shù)竭壿嬯嚵兄械娜蝿?wù)。

NoC有兩個(gè)主要部分。NoC的外部設(shè)備部分負(fù)責(zé)PCIe Gen 5接口、內(nèi)存控制器和核心FPGA邏輯陣列之間的數(shù)據(jù)傳輸。NoC的另一部分由在FPGA結(jié)構(gòu)頂部運(yùn)行的行和列組成。NoC提供雙向的、256位寬的水平和垂直通道,這些通道在可編程集群之間運(yùn)行。每個(gè)NoC行或列可以同時(shí)在相反方向上以512 Gbps的速率處理數(shù)據(jù)流。為了最大限度地利用基礎(chǔ)架構(gòu)及其在Speedster7t器件上快速分發(fā)數(shù)據(jù)的能力,NoC還直接連接到片上400G以太網(wǎng)控制器,并采用智能數(shù)據(jù)流分配策略,通過易于實(shí)現(xiàn)的256位寬接口,沿NoC通道將數(shù)據(jù)流劃分為并行的可編程邏輯集群組。

NoC數(shù)據(jù)模式

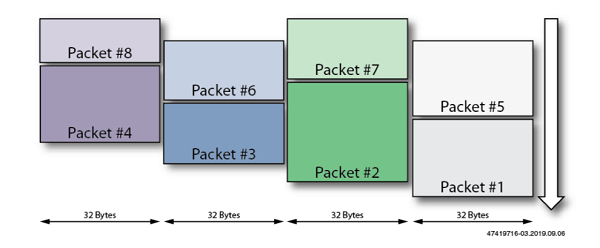

為了實(shí)現(xiàn)400 Gbps的性能,設(shè)計(jì)人員可以使用一種稱為數(shù)據(jù)包模式的全新處理模式,在這種模式下,傳入以太網(wǎng)的數(shù)據(jù)流被重新排列(如圖9所示)成四個(gè)較小的32字節(jié)的數(shù)據(jù)包。這些數(shù)據(jù)包在四條獨(dú)立的256位總線上以506MHz的頻率運(yùn)行。這種模式的優(yōu)點(diǎn)包括:當(dāng)數(shù)據(jù)包結(jié)束時(shí),浪費(fèi)的字節(jié)更少;并且數(shù)據(jù)可以并行傳輸(前后相接),而不是必須等到在第一個(gè)數(shù)據(jù)包完成傳輸后才開始第二個(gè)數(shù)據(jù)包的傳輸。

對于運(yùn)行在分組化數(shù)據(jù)上的典型網(wǎng)絡(luò)應(yīng)用,每個(gè)模塊可以對其接收到的數(shù)據(jù)包報(bào)頭進(jìn)行分類和標(biāo)記,并通過調(diào)用NoC接口的服務(wù)來連接片外GDDR6或DDR4存儲器,將不需要進(jìn)一步處理的工作負(fù)載卸載到外部存儲器的緩沖區(qū)存儲。對每個(gè)數(shù)據(jù)包的處理完成后,通過NoC引導(dǎo)來自外部和內(nèi)部緩沖區(qū)的數(shù)據(jù)流,將必要的數(shù)據(jù)傳送到相關(guān)的以太網(wǎng)出口端口。因此,許多操作并不需要調(diào)用FPGA邏輯陣列中的資源,并且可以充分利用NoC和以太網(wǎng)端口之間的直接連接。

圖9:數(shù)據(jù)包模式(Packet Mode)下的數(shù)據(jù)總線重新排列

圖10:使用數(shù)據(jù)包模式(Packet Mode)的400 Gbps以太網(wǎng)

通過NoC通道的數(shù)據(jù)分發(fā)也可以采用非數(shù)據(jù)包化的模式來完成,以支持目前在以太網(wǎng)上使用的、盡可能多樣化的協(xié)議,例如5G系統(tǒng)中的eCPRI,并幫助設(shè)計(jì)人員避免在邏輯架構(gòu)中不得已去創(chuàng)建超寬總線。

高速存儲接口

Speedster7t的架構(gòu)師對存儲接口的選擇反映了以太網(wǎng)和NoC連接可提供的巨大容量。一種可能的方法是在一系列設(shè)計(jì)中采用即將推出的HBM2接口。盡管這樣的接口可以提供所需的性能水平,但HBM2價(jià)格昂貴,這將迫使客戶去等待必要的組件和集成技術(shù)的出現(xiàn)。

與此不同,Speedster7t系列則采用了GDDR6標(biāo)準(zhǔn),該標(biāo)準(zhǔn)為當(dāng)今片外存儲器提供了最高的性能。Speedster7t FPGA是市場上首款支持該接口的器件,每個(gè)片上GDDR6內(nèi)存控制器可維持512 Gbps的帶寬。在單個(gè)AC7t1500器件中最多可帶有8個(gè)GDDR6控制器,使總的內(nèi)存帶寬可達(dá)到4 Tbps。

對PCIe Gen 5的支持

除了以太網(wǎng)和存儲控制器,Speedster7t FPGA上提供的對PCIe Gen 5的支持還能夠與主機(jī)處理器緊密集成,以支持諸如sidecar智能網(wǎng)卡(SmartNIC)設(shè)計(jì)等高性能加速器應(yīng)用。PCI Gen 5控制器使其能夠讀取和寫入存儲在FPGA內(nèi)存層級結(jié)構(gòu)中的數(shù)據(jù),包括許多位于邏輯架構(gòu)內(nèi)的塊RAM,以及連接到FPGA存儲控制器的外部GDDR6和DDR4 SRAM設(shè)備。在FPGA邏輯陣列中實(shí)例化的數(shù)據(jù)傳輸控制器(例如DMA引擎),可以類似地通過PCIe Gen 5總線訪問與主機(jī)處理器共享的內(nèi)存,而無需消耗FPGA邏輯陣列內(nèi)的任何資源即可實(shí)現(xiàn)這種高帶寬連接,并且設(shè)計(jì)時(shí)間幾乎為零。用戶只需要啟用PCIe和GDDR6接口,就可以通過NoC發(fā)送事務(wù)數(shù)據(jù)。

下面的圖11展示了PCIe子系統(tǒng)與任何GDDR6或DDR4存儲接口之間的直接連接。

圖11:無需消耗FPGA邏輯陣列即可實(shí)現(xiàn)PCIe和GDDR6之間的數(shù)據(jù)傳輸

112-Gbps SerDes

AC7t1500器件搭載了400G以太網(wǎng)通道用于物理層訪問,該器件可提供多達(dá)32個(gè)高速SerDes通道,它們可用于需要數(shù)據(jù)速率高達(dá)112 Gbps的其他標(biāo)準(zhǔn),并完全支持PAM4信令。這些SerDes通道支持器件間實(shí)現(xiàn)極短距離(XSR)和超短距離(USR)通道,事實(shí)證明這些通道對一系列通信系統(tǒng)都非常重要。SerDes實(shí)現(xiàn)方式的靈活性加上對各種以太網(wǎng)速度的支持(因?yàn)橐鸭闪艘粋€(gè)可分解型控制器)為設(shè)計(jì)提供了現(xiàn)成可用的支持,這些設(shè)計(jì)將能夠與任何規(guī)劃的CPRI和eCPRI格式(用于5G前端傳輸設(shè)計(jì))一起使用。

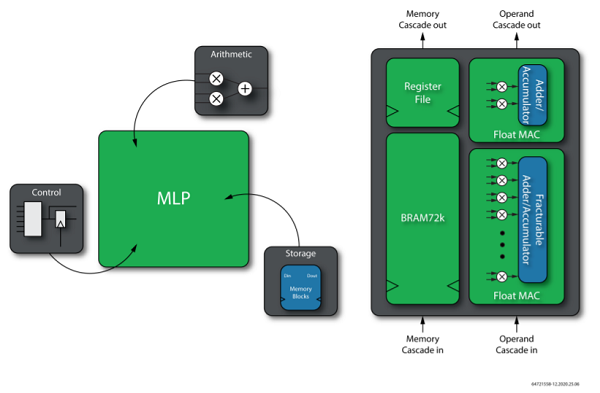

機(jī)器學(xué)習(xí)處理器

對于計(jì)算密集型任務(wù),在Speedster7t FPGA上部署的Speedster7t機(jī)器學(xué)習(xí)處理器(MLP)是靈活的且可分解的算術(shù)單元。MLP是高密度乘法器陣列,帶有支持多種數(shù)字格式的浮點(diǎn)和整數(shù)MAC模塊。MLP帶有集成的內(nèi)存塊,可以在不使用FPGA資源的情況下執(zhí)行操作數(shù)和內(nèi)存級聯(lián)功能。MLP適用于一系列矩陣數(shù)學(xué)運(yùn)算,從5G無線電控制器的波束成形計(jì)算到加速深度學(xué)習(xí)應(yīng)用,諸如數(shù)據(jù)流模式和數(shù)據(jù)包內(nèi)容分析。

圖12:機(jī)器學(xué)習(xí)處理器原理框圖

結(jié)論

從5G網(wǎng)絡(luò)的邊緣到數(shù)據(jù)中心內(nèi)部的交換機(jī),通信和網(wǎng)絡(luò)系統(tǒng)對芯片的功能帶來了極大的壓力,以支持其所需的計(jì)算能力和數(shù)據(jù)傳輸速率。傳統(tǒng)的可編程邏輯為這些系統(tǒng)提供了靈活性和速率的最佳組合,但是近年來卻因以太網(wǎng)等協(xié)議的速度提高到100G和400G而面臨新挑戰(zhàn)。Speedster7t架構(gòu)通過采用創(chuàng)新的、多層級片上網(wǎng)絡(luò),使數(shù)據(jù)能夠在器件周圍輕松傳輸,而不影響FPGA的邏輯陣列,從而充分保障所有已集成在內(nèi)的全球最先進(jìn)的I / O接口,諸如400G以太網(wǎng)、GDDR6和PCI Gen 5,以支持充分發(fā)揮核心的可編程邏輯結(jié)構(gòu)的潛在能力。

Achronix Speedster7t系列采用了一種借助于NoC技術(shù)的創(chuàng)新架構(gòu),并充分利用了7nm技術(shù)來部署各種現(xiàn)有可用的、性能最高的控制器,提供了其他FPGA器件迄今為止所缺少的要素。基于Speedster7t FPGA的設(shè)計(jì)可以接收來自多個(gè)高速數(shù)據(jù)源的巨量數(shù)據(jù),并將這些數(shù)據(jù)分發(fā)到可編程的片上算法和處理單元,然后以盡可能低的延遲來獲得這些結(jié)果。由此帶來的是一種創(chuàng)新的FPGA架構(gòu),可以支持目前正在設(shè)計(jì)的下一代5G、軟件定義網(wǎng)絡(luò)和數(shù)據(jù)中心系統(tǒng)。Speedster7t FPGA現(xiàn)在可以推動通信和網(wǎng)絡(luò)應(yīng)用向新一代發(fā)展。

版權(quán)所有?2020 Achronix半導(dǎo)體公司保留所有權(quán)利。Achronix、Speedcore、Speedster和ACE是Achronix半導(dǎo)體公司在美國和/或其他國家/地區(qū)的商標(biāo)。所有其他商標(biāo)均為其各自所有者的財(cái)產(chǎn)。所有規(guī)格如有更改,恕不另行通知。

免責(zé)聲明

本文件中所提供的信息被認(rèn)為是準(zhǔn)確和可靠的。但是,Achronix半導(dǎo)體公司不對此類信息的完整性或準(zhǔn)確性作出任何聲明或擔(dān)保,并且對于使用本文包含的信息不承擔(dān)任何責(zé)任。Achronix半導(dǎo)體公司保留隨時(shí)更改本文件及其所含信息的權(quán)利,恕不另行通知。所有Achronix商標(biāo)、注冊商標(biāo)、免責(zé)聲明和專利均在網(wǎng)站上列出。