進入最近幾年,每當我們引入一個新的先進工藝節(jié)點,大家都把絕大多數(shù)注意力集中在光刻更新上。引用的常用指標是每平方毫米的晶體管或(高密度)SRAM位單元的面積。或者,可以使用透射電子顯微鏡(TEM)對薄片樣品進行詳細的分解分析,以測量鰭片節(jié)距(fin pitch),柵極節(jié)距(gate pitch)和(第一級)金屬節(jié)距(metal pitch)。

隨著關鍵尺寸層從193i到近紫外線(EUV)的轉(zhuǎn)變,對光刻的關注是可以理解的。然而,制程開發(fā)和認證涵蓋了材料工程的許多方面,才得以實現(xiàn)可靠的可制造性,進而實現(xiàn)產(chǎn)品目標的充分補充。具體而言,制程開發(fā)工程師面臨越來越嚴格的可靠性目標,同時要實現(xiàn)性能和功耗的改善。

在最近的IEDM會議上,TSMC進行了技術演講,重點介紹了使N5工藝節(jié)點能夠達到(風險生產(chǎn))資格的開發(fā)重點。本文總結了該演示文稿的重點。

在SemiWiki較早的文章中,我們介紹了N5的光刻和功耗/性能功能。N5的重大材料差異之一是引入了“高遷移率”設備溝道或HMC。如文所述,通過在器件溝道區(qū)域引入額外的應變,可以提高N5中的載流子遷移率。(盡管TSMC沒有提供技術細節(jié),但通過向硅溝道區(qū)或Si(1-x)Ge(x)中引入適量的鍺,pFET空穴遷移率也可能得到改善。)

此外,優(yōu)化的N5工藝節(jié)點在柵極和溝道之間結合了優(yōu)化的高K金屬柵極(HKMG)電介質(zhì)堆棧,從而產(chǎn)生了更強的電場。

該“帶隙工程”對于載流子遷移率和柵極氧化物堆疊材料選擇的一個非常重要的方面是確保滿足可靠性目標。N5可靠性鑒定的一些結果如下所示。

臺積電強調(diào)了N5資格測試的以下可靠性措施:

偏置溫度穩(wěn)定性(bias temperature stability :BTI)

對于pFET的NBTI和對于nFET的PBTI都表現(xiàn)為由于捕獲的氧化物電荷而導致的器件Vt漂移(正絕對值)隨時間的性能下降

也可能導致SRAM操作的VDDmin下降

熱載流子注入(hot carrier injection :HCI)

電荷不對稱注入到器件漏極附近的柵極氧化物中(飽和工作),導致載流子遷移率下降

時間相關的柵極氧化物介電擊穿(TDDB)

請注意,N5節(jié)點旨在滿足高性能和移動(低功耗)產(chǎn)品要求。結果,性能下降和保持主動SRAM VDDmin都是重要的長期可靠性標準。

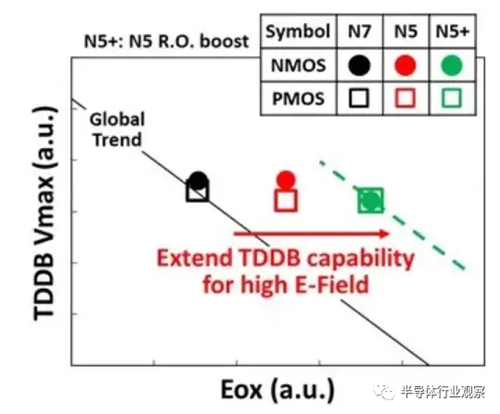

TDDB

上圖顯示,即使柵極電場增加,TDDB的壽命也與節(jié)點N7相當

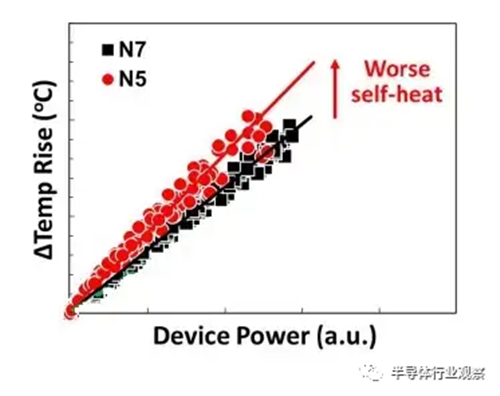

自發(fā)熱(Self-heating)

FinFET器件幾何結構的引入大大改變了從溝道功耗到環(huán)境(ambient)的熱阻路徑(thermal resistance paths)。采用新的“自熱”分析流程來更準確地計算局部結點溫度,通常以“熱圖”形式顯示。正如從N7到N5的尺寸激進縮放所預期的那樣,N5的自熱溫度升高更大,如下所示。

HPC產(chǎn)品的設計人員需要與他們的EDA合作伙伴(用die熱分析工具)及其產(chǎn)品工程團隊合作,以進行準確的(die和系統(tǒng))熱阻建模。對于die模型,有源和非有源結構都會強烈影響散熱。

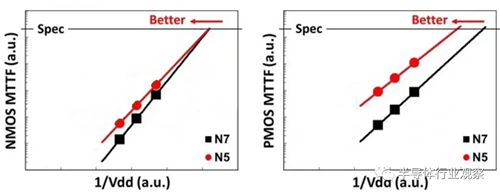

HCI

N7和N5的nFET和pFET的熱載流子注入性能下降如下所示。

請注意,HCl與溫度密切相關,因此必須進行準確的自熱分析。

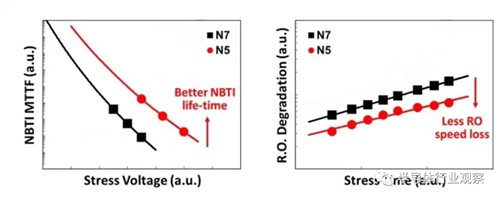

BTI

下面說明了pMOS NBTI可靠性分析結果以及相關的環(huán)形振蕩器性能影響。

在這兩種情況下,可靠性分析均表明N5相對于N7具有改善的BTI特性。

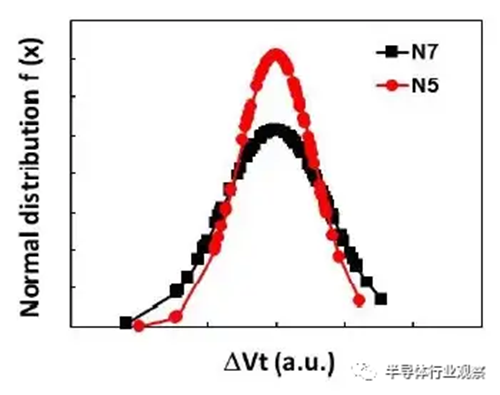

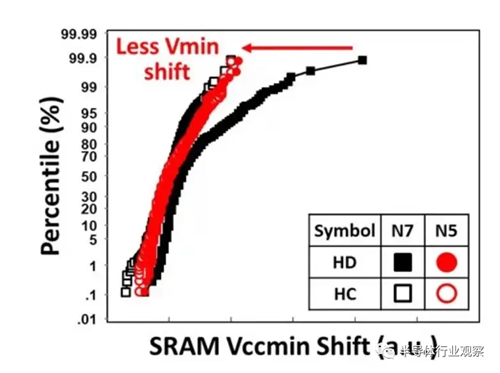

SRAM VDDmin

SRAM的最低工作電壓(VDDmin)是低功耗設計的關鍵參數(shù),尤其是對本地存儲器存儲的需求不斷增長時。影響最低SRAM工作電壓(具有足夠的讀寫裕度)的兩個因素是:

BTI設備轉(zhuǎn)移,如上所示

設備Vt的統(tǒng)計過程變化,如下所示(在N7和N5中標準化為Vt_mean)

根據(jù)這兩個單獨的結果,HTOL應力后的SRAM可靠性數(shù)據(jù)顯示N5相對于N7改善了VDDmin影響。

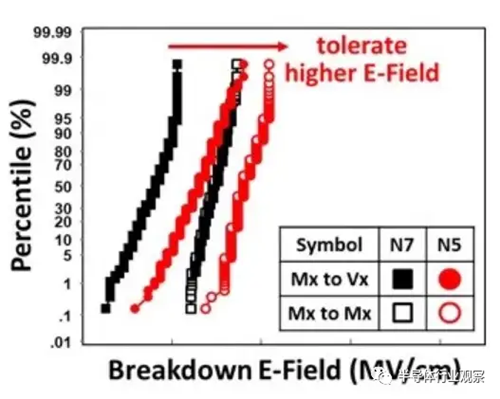

互連線

臺積電還簡要介紹了N5工藝工程對(Mx,低級金屬)互連可靠性優(yōu)化的重視。通過改進的鑲嵌溝槽襯里(damascene trench liner)和“ Cu reflow”步驟,Mx間距的縮放比例(使用EUV在N5中增加了約30%)不會對電遷移失敗產(chǎn)生不利影響,也不會對線間電介質(zhì)造成破壞。下圖顯示了N5的線到線(和過孔)累積擊穿可靠性故障數(shù)據(jù),而N7 – N5可以按比例縮放Mx間距來承受較高的電場。