對(duì)于后硅時(shí)代的選擇,工程師一直致力于把原子厚的二維材料制成晶體管的研究。最著名的是石墨烯,但專家認(rèn)為,二維半導(dǎo)體(例如二硫化鉬和二硫化鎢)可能更適合此工作。因?yàn)槭┤狈叮@種禁帶使材料成為半導(dǎo)體。

現(xiàn)在,通過將石墨烯和MoS 2結(jié)合在一起,研究人員已經(jīng)制造出一種晶體管,該晶體管的工作電壓為常規(guī)電壓的一半,并且電流密度高于以前開發(fā)中的任何最新2D晶體管。這將大大降低基于這些2D器件的集成電路的功耗。

“我們能夠充分挖掘2D材料的潛力,從而制造出一種在能耗和開關(guān)速度方面表現(xiàn)出更好性能的晶體管,”布法羅大學(xué)電氣工程學(xué)教授李華敏在IEDM 2020上說。

有趣的是,該設(shè)備利用了石墨烯缺乏帶隙的優(yōu)勢(shì)。在晶體管中,柵電極上的電壓將電荷載流子注入到溝道區(qū)中,從而在源電極和漏電極之間形成導(dǎo)電路徑。常規(guī)的硅晶體管和2D MoS 2晶體管利用了從源發(fā)出高能“熱”電子的優(yōu)勢(shì)。對(duì)于漏極電流每增加十倍(60 mV /十倍:60 mV/decade),這就設(shè)置了60毫伏的基本極限。

李說,沒有帶隙的石墨烯是“冷”電子源。這意味著需要更少的能量將電子跨過溝道區(qū)域發(fā)送到漏電極。結(jié)果:可以更快地接通和斷開設(shè)備電流。

李說:“使用這種獨(dú)特的機(jī)制,我們能夠突破切換的基本極限。” 該小組的1納米厚晶體管僅需29 mV即可實(shí)現(xiàn)器件電流10倍的變化。“我們使用較少的電壓來切換器件并控制更多的電流,因此我們的晶體管具有更高的能源效率。”

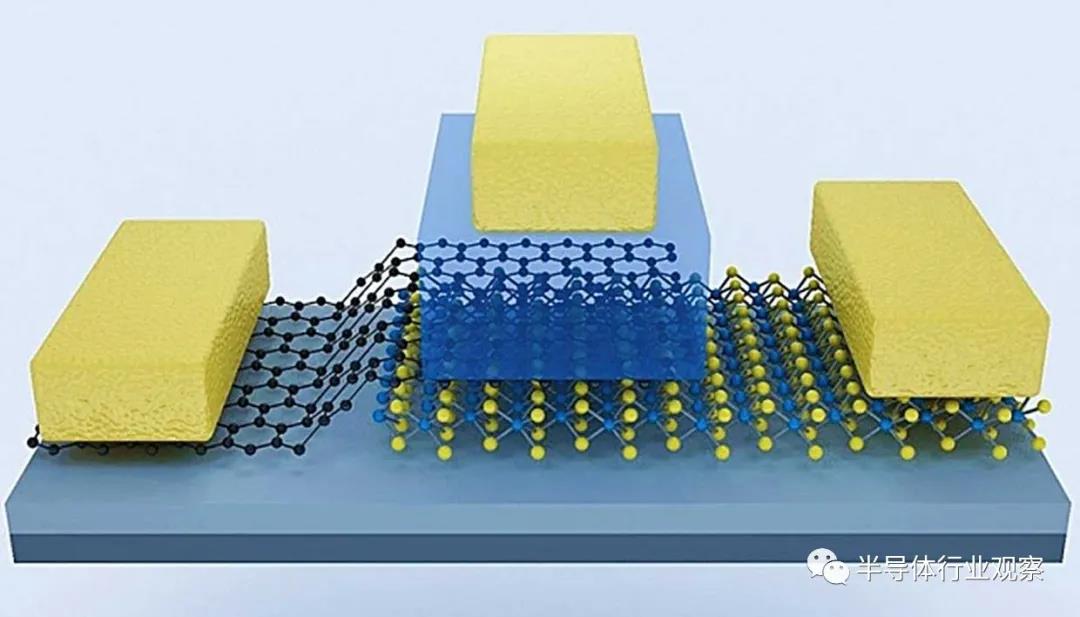

研究人員通過在單層MoS 2上堆疊單層石墨烯來制造這種設(shè)備。此堆疊區(qū)域用作晶體管通道,研究人員將柵電極沉積在頂部。石墨烯單層充當(dāng)源極,而二硫化鉬層充當(dāng)漏極。

而據(jù)山東大學(xué)的研究人員說,其他冷源材料,例如2D金屬和electron-rich,n摻雜的半導(dǎo)體,也可以用于突破60 mV /十年(60 mV/decade)的極限。通過仿真和建模,他們表明,n摻雜石墨烯可以將電壓降至24 mV。即使簡(jiǎn)單地使用n摻雜的硅, 也可以將其降至33 mV。

李說,他和他的同事選擇MoS 2作為他們的概念驗(yàn)證設(shè)備,因?yàn)檫@是研究人員了解并研究了很長(zhǎng)時(shí)間的2D半導(dǎo)體。臺(tái)積電的研究人員也在IEDM上發(fā)表了有關(guān)MoS 2晶體管的最新發(fā)現(xiàn) 。

這些小組和其他小組不限于此2D材料。他們還使用二硫化鎢(WS 2)和黑磷等材料。Buffalo的Li說:“如果其他材料在我們的設(shè)備技術(shù)中能更好地工作,我們將進(jìn)行探索。”

位于比利時(shí)魯汶的Imec將賭注押在WS 2上,該公司的研究人員認(rèn)為WS 2應(yīng)該能生產(chǎn)出性能最高的設(shè)備。兩年前,imec計(jì)劃總監(jiān)Iuliana Radu和她的團(tuán)隊(duì)開發(fā)了一種在300毫米硅晶圓上放置高質(zhì)量WS 2 單層的技術(shù)。他們現(xiàn)在報(bào)告說,他們可以在晶圓級(jí)制造WS 2晶體管。他們說:“這項(xiàng)工作為工業(yè)上采用2D材料鋪平了道路。”

硅的繼任者:碳納米管有了新進(jìn)展

得益于研究人員的持續(xù)推進(jìn),碳納米管器件現(xiàn)在正在越來越接近硅的能力,最新的進(jìn)展也在最近舉辦的IEEE電子器件會(huì)議IEDM上揭曉。會(huì)上,來自TSMC,加州大學(xué)圣地亞哥分校和斯坦福大學(xué)的工程師介紹了一種新的制造工藝,該工藝可以更好地控制碳納米管晶體管。這種控制對(duì)于確保在邏輯電路中充當(dāng)晶體管的晶體管完全關(guān)閉時(shí)至關(guān)重要。

近年來,人們對(duì)碳納米管晶體管的興趣有所增加,因?yàn)樗鼈冇锌赡鼙裙杈w管更進(jìn)一步縮小尺寸,并提供一種生產(chǎn)電路堆疊層的方法比在硅中做起來容易得多。

該團(tuán)隊(duì)發(fā)明了一種生產(chǎn)更好的柵極電介質(zhì)(gate dielectric)的工藝。那是柵電極和晶體管溝道區(qū)之間的絕緣層。在操作中,柵極處的電壓會(huì)在溝道區(qū)中建立電場(chǎng),從而切斷電流。然而,隨著幾十年來硅晶體管的規(guī)模縮小,由二氧化硅制成的絕緣層必須越來越薄,以便使用較少的電壓來控制電流,從而降低了能耗。最終,絕緣屏障非常薄,以至于電荷實(shí)際上可以通過它隧穿,從而帶來電流泄漏并浪費(fèi)能量。

大約十多年前,硅半導(dǎo)體工業(yè)通過切換到新的介電材料二氧化鉿(hafnium dioxide)解決了這個(gè)問題。與先前使用的二氧化硅相比,該材料具有較高的介電常數(shù)(high-k),這意味著相對(duì)較厚的高k介電層在電氣上等效于非常薄的氧化硅層。

碳納米管晶體管還使用HfO 2柵極電介質(zhì)。碳納米管的問題在于,它們不允許在控制按比例縮小的設(shè)備所需的薄層中形成電介質(zhì)。

沉積high-k電介質(zhì)的方法稱為原子層沉積。顧名思義,它一次可建造一個(gè)原子層的材料。但是,它需要一個(gè)開始的地方。在硅中,這是在表面自然形成的原子的原子薄層。

碳納米管不提供這種立足點(diǎn)來開始沉積。它們不會(huì)自然形成氧化物層,畢竟二氧化碳和一氧化碳都是氣體。納米管中任何會(huì)導(dǎo)致所需“懸掛鍵”(dangling bonds)的缺陷都會(huì)限制其傳導(dǎo)電流的能力。

到目前為止,在碳納米管上生長(zhǎng)一層薄薄的high-k電介質(zhì)二氧化鉿是不可能的。斯坦福大學(xué)和臺(tái)積電的研究人員通過在它們之間添加中間k介電層解決了這一問題。

“形成high-k電介質(zhì)一直是一個(gè)大問題。” 領(lǐng)導(dǎo)這項(xiàng)工作的臺(tái)積電(TSMC)首席科學(xué)家,斯坦福大學(xué)教授Philip Wong(黃漢森)說。“因此您必須將比納米管更厚的氧化物傾倒在納米管的頂部,而不是在縮小的晶體管中”,黃漢森建議。“要了解為什么這是一個(gè)問題,可以想象一下柵極電壓的作用,就是試圖用腳踩踏來阻止水流過花園軟管。如果在腳和軟管之間放一堆枕頭(類似于厚的門氧化物),則枕頭會(huì)變得更難”,黃漢森進(jìn)一步指出。

臺(tái)積電的Matthias Passlack和UCSD的Andrew Kummel教授提出了一種解決方案,將HfO2的原子層沉積與沉積中間介電常數(shù)材料氧化鋁的新方法結(jié)合在一起。Al2O3是使用UCSD發(fā)明的納米霧工藝沉積的。像水蒸氣凝結(jié)形成霧一樣,Al2O3凝結(jié)成簇,覆蓋納米管表面。然后可以使用該界面電介質(zhì)作為立足點(diǎn)開始HfO2的原子層沉積。

這兩種電介質(zhì)的綜合電學(xué)特性使該團(tuán)隊(duì)能夠構(gòu)建一種器件,該器件的柵極電介質(zhì)在寬度僅為15納米的柵極下的厚度小于4納米。最終的器件具有與硅CMOS器件相似的開/關(guān)電流比特性,并且仿真表明,即使具有較小柵極電介質(zhì)的較小器件也能正常工作。

但是,在碳納米管器件能夠匹配硅晶體管之前,還有很多工作要做。其中一些問題已單獨(dú)解決,但尚未合并到單個(gè)設(shè)備中。例如,黃漢神團(tuán)隊(duì)設(shè)備中的單個(gè)納米管限制了晶體管可以驅(qū)動(dòng)的電流量。他表示,要使多個(gè)相同的納米管完美對(duì)齊一直是一個(gè)挑戰(zhàn)。北京大學(xué)彭練矛實(shí)驗(yàn)室的研究人員最近成功地使每微米排列250個(gè)碳納米管,這表明解決方案可能很快就會(huì)出現(xiàn)。

另一個(gè)問題是設(shè)備的金屬電極和碳納米管之間的電阻,特別是當(dāng)這些觸點(diǎn)的尺寸縮小到接近當(dāng)今先進(jìn)硅芯片所使用的尺寸時(shí)。去年,黃漢森的一名學(xué)生Greg Pitner(現(xiàn)為臺(tái)積電研究人員和IEDM研究的主要作者)報(bào)告了一種方法,可以將一種接觸類型(p型)的電阻提高到兩倍以下接觸的理論極限僅為10納米。但是,與碳納米管的n型接觸尚未達(dá)到相似的性能水平,而CMOS邏輯則需要兩種類型。

最后,需要摻雜碳納米管以增加?xùn)艠O兩側(cè)的載流子數(shù)量。通過用其他元素替換晶格中的一些原子,可以在硅中完成這種摻雜。這在碳納米管中是行不通的,因?yàn)樗鼘⑵茐慕Y(jié)構(gòu)的電子能力。相反,碳納米管晶體管使用的是靜電摻雜。在此,有意操縱介電層的成分以將電子捐贈(zèng)給納米管或?qū)⑵涑槌觥|S漢森表示,他的學(xué)生Rebecca Park在該層中使用氧化鉬取得了良好的效果。

他說:“我們感到非常興奮,因?yàn)槲覀冋谝徊揭徊降貙⑺羞@些難題都擊倒。” “下一步就是將它們放在一起……如果我們可以將所有這些結(jié)合起來,我們將擊敗硅。”