2020年7月,JEDEC固態(tài)技術(shù)協(xié)會正式發(fā)布了新的主流內(nèi)存標(biāo)準(zhǔn)DDR5 SDRAM的最終規(guī)范,這意味著新一輪的內(nèi)存升級換代又要開始了!

自上一代DDR4內(nèi)存標(biāo)準(zhǔn)的問世到現(xiàn)在,已經(jīng)歷了9年,有數(shù)據(jù)顯示目前DDR4標(biāo)準(zhǔn)產(chǎn)品在服務(wù)器和PC領(lǐng)域的滲透率都已經(jīng)超過了95%,按照摩爾定律或者其他技術(shù)預(yù)測,新一代的DDR內(nèi)存標(biāo)準(zhǔn)早該駕到了,由此足見在內(nèi)存領(lǐng)域技術(shù)進(jìn)步的邊際成本是越來越高。

好在DDR5這把“磨”了近十年的“劍”并沒有讓大家失望,從JEDEC協(xié)會公布的信息來看,與上一代標(biāo)準(zhǔn)相比,DDR5將主電壓從1.2 V降低至1.1 V,最大芯片密度提高了4倍,最大數(shù)據(jù)速率提高一倍,突發(fā)長度增加一倍,存儲單元組數(shù)增加一倍。可以說在速度、容量、能耗和穩(wěn)定性等方面,DDR5都來了一次全面的提升。

圖1:不同DDR內(nèi)存標(biāo)準(zhǔn)之間的比較 (資料來源:JEDEC)

DDR5標(biāo)準(zhǔn)推出之后,Micron等內(nèi)存及模塊制造商都已經(jīng)積極行動起來,陸續(xù)推出了相關(guān)的樣品,為即將到來的新一波內(nèi)存升級潮積極備戰(zhàn)。按照以往的經(jīng)驗(yàn),2021年DDR5將最先進(jìn)入服務(wù)器市場,之后伴隨著工藝穩(wěn)定和產(chǎn)能爬坡,再逐漸向PC和消費(fèi)電子等領(lǐng)域滲透。但不管怎么說,這個進(jìn)程已經(jīng)啟動。

當(dāng)然,在一輪技術(shù)熱潮到來之際,在做出“追不追,以及怎么追”等決定之前,既要做到知其然,還要知其所以然,因此今天我們就來看看,DDR5這性能提升背后,究竟暗藏著哪些技術(shù)玄機(jī)。

DDR5升級背后的技術(shù)玄機(jī)

數(shù)據(jù)存儲容量和速率是衡量DDR標(biāo)準(zhǔn)代際之間差異的核心指標(biāo),在提升此核心性能方面,DDR5放出了以下這些大招兒:

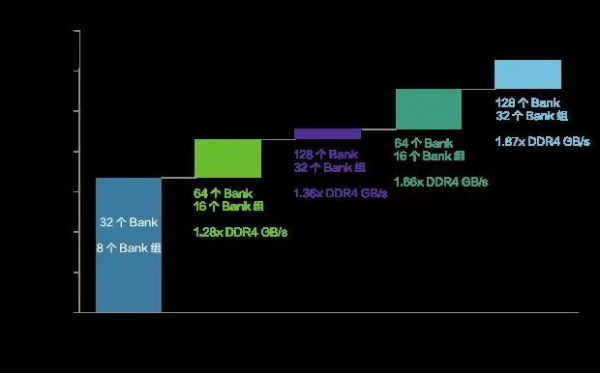

增加整體Bank數(shù)量

當(dāng)存儲器密度增加時,需要擴(kuò)展Bank的數(shù)量來應(yīng)對。DDR5標(biāo)準(zhǔn)中每個Bank組中的Bank數(shù)量(4個)保持不變,而將Bank組的數(shù)量增加一倍,達(dá)到了4或8個。通過允許在任意指定時間開啟更多分頁,并增加高頁面點(diǎn)擊率的統(tǒng)計概率,來提高整體的系統(tǒng)效率。增加的Bank組通過提高使用短時序的可能性來減輕內(nèi)部時序限制。

增加數(shù)據(jù)突發(fā)長度

DDR5將缺省的數(shù)據(jù)突發(fā)長度(Burst Length)從DDR4標(biāo)準(zhǔn)的BL8增加到了BL16,這樣就提高了命令/地址和數(shù)據(jù)總線的效率。也就是說,相同的CA總線讀寫事務(wù)可以在數(shù)據(jù)總線上實(shí)現(xiàn)兩倍的數(shù)據(jù)量,同時限制在同一Bank內(nèi)受到IO/陣列時序限制的風(fēng)險。突發(fā)長度的增加也可減少相同的64B緩存線數(shù)據(jù)負(fù)載存取所需的IO數(shù)量,減少存取特定數(shù)據(jù)量所需的命令,這對于功耗的控制十分有利。

特別值得一提的是,數(shù)據(jù)突發(fā)長度的增加可以讓DDR5 DIMM模塊實(shí)現(xiàn)雙子通道的架構(gòu),提高整體的通道并行能力、靈活性和數(shù)量,進(jìn)而優(yōu)化內(nèi)存整體的能效。

增加新的命令

在以往DDR SDRAM標(biāo)準(zhǔn)的ALL-BANK REFRESH 命令(REFab)基礎(chǔ)上,DDR5增加了SAME-BANK REFRESH (REFsb) 命令。SDRAM在刷新 (REFRESH)之前,需要準(zhǔn)備刷新的Bank處于idle(閑置)狀態(tài),且這些Bank在刷新命令期間無法繼續(xù)后續(xù)的寫入和讀取活動。因此在執(zhí)行REFab刷新命令前,必須確保所有Bank均處于閑置狀態(tài),以3.9μs一次計算,一個16Gb DDR5 SDRAM 器件,其持續(xù)時間為295ns。

而新增加的REFsb在發(fā)出命令之前,每個Bank組中只需一個Bank閑置即可,其余的在發(fā)出REFsb命令時不需閑置,對非更新Bank的唯一時序限制為 same-bank- refresh-to-activate 延遲。REFsb命令以細(xì)粒度刷新 (FGR) 模式發(fā)出,每個Bank平均每1.95μs接收一次REFRESH命令,這樣一個16Gb DDR5 SDRAM器件的REFsb 持續(xù)時間僅130ns。

有模擬分析數(shù)據(jù)顯示,使用REFsb系統(tǒng)效能處理量比使用REFab時提高6%至9%;REFsb將刷新對平均閑置延遲時間的影響從11.2ns縮短到了5.0ns。

基于上述這幾個方面的優(yōu)化,DDR5在性能上實(shí)現(xiàn)了明顯的提升。圖2展示了,在規(guī)定的測試條件下,DDR5與DDR4相比在數(shù)據(jù)速率上的優(yōu)勢。

圖2:DDR5與DDR4相比的性能優(yōu)勢(資料來源:Micron)

除了在核心性能上的突破,DDR5還在可靠性、可用性與服務(wù)性 (RAS)上,以及可操作性上做了諸多優(yōu)化。

芯片內(nèi)建錯誤校正碼 (ECC):通過DDR5器件輸出數(shù)據(jù)之前在READ命令期間執(zhí)行校正,減輕系統(tǒng)錯誤校正的負(fù)擔(dān)。在DDR4內(nèi)存上實(shí)現(xiàn)ECC功能,需要額外增加一顆芯片,而DDR5原生支持片上ECC,對于提升系統(tǒng)可靠性大有幫助。

PPR強(qiáng)化功能:包括hPPR (硬) 和sPPR (軟)兩個獨(dú)立的修復(fù)功能。主要的優(yōu)化在于減少了執(zhí)行sPPR修復(fù)之前需要Bank中備份的列,這樣可以將備份和儲存大量信息所需的系統(tǒng)時間縮至最短,通常每列數(shù)據(jù)約2μs。

多用途命令 (MPC):DDR5時鐘頻率的提高,也給初始化和訓(xùn)練之前的操作執(zhí)行帶來挑戰(zhàn)。為此,DDR5使用多用途命令 (MPC) 來執(zhí)行介面初始化、訓(xùn)練和定期校正等功能,提升操作的效率。

從上文可以看出,一方面DDR5通過增加Bank組、增加突發(fā)長度、引入新的REFsb刷新命令等舉措,提升核心性能,降低用戶總體擁有成本;另一方面通過優(yōu)化RAS和可操作性為開發(fā)和應(yīng)用帶來更大便利,這樣雙管齊下,為DDR5標(biāo)準(zhǔn)打造了穩(wěn)固的根基。

表1:DDR5產(chǎn)品特色與功能優(yōu)化(資料來源:安富利)

DDR5內(nèi)存條的變化

當(dāng)然,想要最大程度上釋放出一個全新內(nèi)存標(biāo)準(zhǔn)的威力,DIMM內(nèi)存模塊的設(shè)計也十分重要。DDR5標(biāo)準(zhǔn)的順利升級,也必然需要內(nèi)存模塊方案的變化,為其提供助力。從Micron提供的技術(shù)文檔中我們可以看到,這樣的變化主要體現(xiàn)在以下幾個方面:

首先,DDR5模塊與DDR4模塊最大的差別就在于,標(biāo)準(zhǔn)的DDR5模塊中有兩個獨(dú)立的子通道,每個子通道最多有兩個實(shí)體封裝的存儲器區(qū)塊 (rank)。每個DRAM封裝都可設(shè)為主要/輔助拓?fù)洌M(jìn)而增加邏輯存儲器區(qū)塊以提高密度。獨(dú)立子通道能提高并行性,并支持存儲器控制器更有效率地安排時序,進(jìn)而打破數(shù)據(jù)傳輸量的限制,滿足服務(wù)器等應(yīng)用中日益增加的運(yùn)算需求。

其次,DDR5中增加了本地的PMIC進(jìn)行電壓調(diào)節(jié),由于將電源管理的功能從主板轉(zhuǎn)到更靠近內(nèi)存芯片的模塊上,因此這種電源架構(gòu)可降低主板的復(fù)雜性、提升電源轉(zhuǎn)換的效率、增加更多電源管理的功能。

再有,DDR5模塊上引入了基于MIPI I3C通訊協(xié)定的邊帶存取功能,能夠更好地支持模塊上越來越多的主動器件,提高可用性,并監(jiān)控關(guān)鍵參數(shù)以掌握模塊工作時與功率、散熱等相關(guān)的詳細(xì)信息。

此外,在L/RDIMM模塊上,還放置了一對溫度傳感器IC,對模塊表面溫度梯度變化進(jìn)行持續(xù)監(jiān)測,并以此為依據(jù)調(diào)整流量變化,或者改變風(fēng)扇速度,通過調(diào)優(yōu)來最大化系統(tǒng)的處理能力。

最后,DDR5模塊設(shè)計的改變,也催生了CAI、MIR和擴(kuò)展接地等其他新功能,以利于改善設(shè)計配置、電源噪聲和模塊信號隔離等特性。命令和地址上的ODT及增強(qiáng)的 DQ/DQS/CA/CS 訓(xùn)練等新功能,也可提供更好的信號處理能效、更快的時鐘速率,最終實(shí)現(xiàn)更高的帶寬。

表2:DDR5與DDR4性能比較與優(yōu)化(資料來源:安富利)

用DDR5開始一個新設(shè)計

可以想見,在即將到來的2021年,如何將計算存儲方案升級到DDR5,將成為很多開發(fā)者——特別是數(shù)據(jù)中心等計算密集型應(yīng)用的開發(fā)者——案頭上的一個重要課題。為了加速這個進(jìn)程,DDR5的核心技術(shù)供應(yīng)商在快馬加鞭推出新產(chǎn)品之外,也紛紛推出了開發(fā)者支持計劃,比如Micron的DDR5 技術(shù)支持計劃 (TEP)中,就為經(jīng)過核準(zhǔn)通過的合伙伙伴提供了豐富的技術(shù)資源,如:

1.產(chǎn)品數(shù)據(jù)手冊、電氣模型、熱模型和仿真模型等技術(shù)資源,以幫助其產(chǎn)品開發(fā)和平臺搭建

2.選擇可用的DDR5元件與模塊樣品

3.與其他生態(tài)系統(tǒng)合作伙伴建立聯(lián)系,以助其進(jìn)行DDR5可用平臺的設(shè)計與搭建

4.技術(shù)支持和培訓(xùn)資料

簡言之,在需求發(fā)展的大趨勢下,面對DDR5,除了“升級”跟上技術(shù)進(jìn)步的節(jié)奏,實(shí)際上我們沒有其他的選擇。現(xiàn)在的關(guān)鍵就在于,如何在升級的這條路上走得更快、更順暢。為此,安富利作為全球領(lǐng)先的技術(shù)分銷商,也會為你提供全面和專業(yè)的支持。