前言:現(xiàn)在的CPU或SoC基本都是在單芯片中集成多個(gè)CPU核心,形成通常所說(shuō)的4核、8核或更多核的CPU或SoC芯片。為什么要采用這種方式?多個(gè)CPU 核心在一起是如何工作的?CPU核心越多就一定越好嗎?帶著這些問(wèn)題,筆者查閱了一些資料,學(xué)習(xí)了相關(guān)概念和要點(diǎn)并編輯成此文,試以通俗的語(yǔ)言來(lái)回答這些專業(yè)問(wèn)題。文章一方面可作為自己的一個(gè)學(xué)習(xí)記錄,另一方面也希望對(duì)讀者有參考作用,不準(zhǔn)確的地方歡迎討論和指正。

要說(shuō)明什么是多核心CPU或SoC芯片,首先要從CPU核心(Core)說(shuō)起。我們知道,CPU是中央處理器(Central Processing Unit)的英文簡(jiǎn)稱,它具有控制和信息處理的能力,是電腦和智能設(shè)備的控制中樞。如果把傳統(tǒng)CPU芯片中的封裝和輔助電路(例如引腳的接口電路、電源電路和時(shí)鐘電路等)排除在外,只保留完成控制和信息處理功能的核心電路,這部分電路就是CPU核心,也簡(jiǎn)稱CPU核。一個(gè)CPU核心基本上是一個(gè)完全獨(dú)立的處理器,它可以從內(nèi)部存儲(chǔ)器中讀取指令,并執(zhí)行指令指定的控制和計(jì)算任務(wù)。

如果把一個(gè)CPU核心和相關(guān)輔助電路封裝在一個(gè)芯片中,這個(gè)芯片就是傳統(tǒng)的單核心CPU芯片,簡(jiǎn)稱單核CPU。如果把多個(gè)CPU核心和相關(guān)輔助電路封裝在一個(gè)芯片中,這個(gè)芯片就是多核心CPU芯片,簡(jiǎn)稱多核CPU。當(dāng)然,多核心CPU芯片會(huì)包含更多的輔助電路,以解決多個(gè)CPU核心之間的通信和協(xié)調(diào)問(wèn)題。

如果在多核心CPU芯片中再集成一些其它功能部件和接口電路,就形成了完整的系統(tǒng),那么這個(gè)芯片就變成了多核心SoC芯片了,簡(jiǎn)稱多核SoC。在不嚴(yán)格區(qū)分的情況下,SoC也可以稱為CPU。

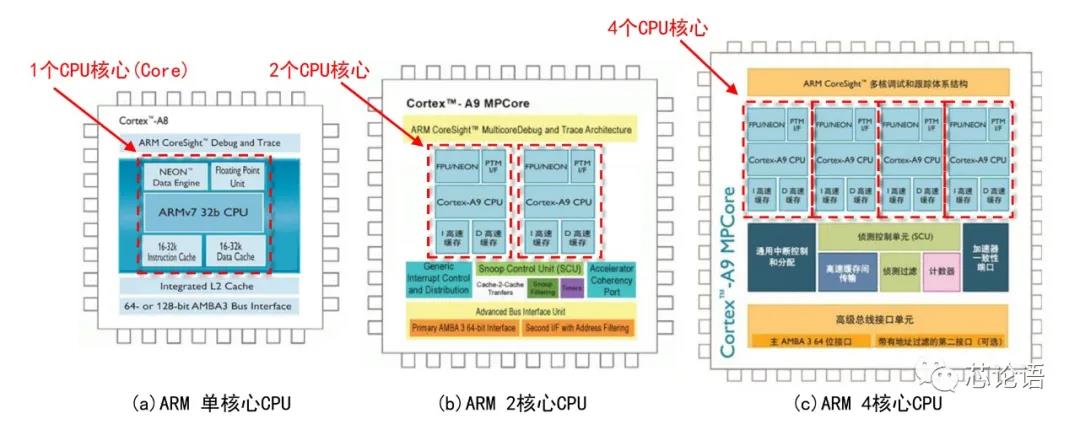

圖1用ARM的單核心CPU和多核心CPU進(jìn)行舉例。圖中紅色虛線框標(biāo)出的部分就是一個(gè)個(gè)的CPU核心,圖1a是ARM Cortex-A8基于ARMv7微架構(gòu)的單核心CPU芯片的示意圖。圖1b和圖1c分別是ARM Cortex-A9 MPCore用2個(gè)和4個(gè)Cortex-A9構(gòu)成的2核心和4核心CPU芯片的示意圖。

圖1. ARM單核心與多核心CPU芯片示意圖

ARM Cortex-A8 CPU是第一款基于新一代ARM v7架構(gòu)的應(yīng)用處理器,它使用了性能、功耗效率和代碼密度更高的Thumb-2技術(shù),它只有單核心架構(gòu)。第一家獲得Cortex-A8 CPU授權(quán)的公司是德州儀器,隨后還有飛思卡爾、Matsushita和三星等公司[3]。Cortex-A8的應(yīng)用案例有MYS-S5PV210開發(fā)板、TI OMAP3系列、蘋果A4處理器(iPhone4)、三星S5PC110(三星I9000)、瑞芯微RK2918、聯(lián)發(fā)科MT6575等。另外,高通的MSM8255、MSM7230等也可看作是其衍生產(chǎn)品。

ARM Cortex-A9 MPCore CPU屬于Cortex-A系列,也是基于ARM v7-A微架構(gòu),它提供了1~4個(gè)CPU核心的可選架構(gòu)。目前我們能見到的4核心CPU大多都是屬于Cortex-A9系列。ARM Cortex-A9的應(yīng)用案例有德州儀器OMAP 4430/4460、Tegra 2、Tegra 3、新岸線NS115、瑞芯微RK3066、聯(lián)發(fā)科MT6577、三星Exynos 4210、4412、華為K3V2等。另外高通APQ8064、MSM8960、蘋果A6、A6X等都可以看作是在A9架構(gòu)基礎(chǔ)上的改良版本。

一、多核心CPU的發(fā)展歷程

發(fā)展多核心CPU的初心源于“人多力量大”的簡(jiǎn)單道理。從這個(gè)意義上來(lái)看,當(dāng)初芯片集成度不高的時(shí)候,Inteli8086 CPU和i8087協(xié)處理器應(yīng)該算是多核心CPU的雛形,是多芯片協(xié)作形成了一個(gè)處理核心,需要采取許多技術(shù)來(lái)解決CPU和協(xié)處理器之間的合作、協(xié)作問(wèn)題。

今天芯片的集成度很高,單芯片中集成幾個(gè)甚至幾十個(gè)CPU核心已不在話下,但還是不能滿足超級(jí)計(jì)算的需要,需要在超級(jí)計(jì)算機(jī)中使用成千上萬(wàn)塊高性能CPU芯片一起合作、協(xié)作,這可以看作芯片內(nèi)多核心、芯片外多芯片的多核心CPU集群。

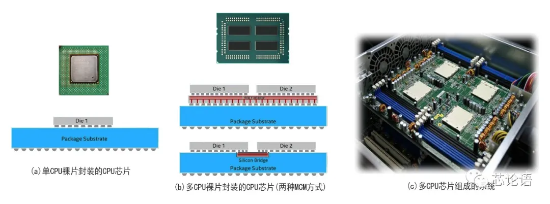

CPU芯片從外觀上看是一塊芯片,但打開封裝來(lái)看,內(nèi)部可能只有一塊裸片(die),也可能是多塊裸片封裝在一起,稱為多芯片模組(Multichip Module,簡(jiǎn)稱MCM),如圖2b所示。但從軟件角度來(lái)看,封裝形式無(wú)關(guān)緊要,無(wú)論是芯片內(nèi)還是芯片外,CPU核心多少才是最重要的,它們決定著系統(tǒng)的并行運(yùn)算和處理能力,它們的主頻頻率和核心之間通信方式?jīng)Q定了系統(tǒng)的處理速度。

圖2. 單裸片封裝、多裸片MCM封裝及多芯片系統(tǒng)的示意圖

另外,今天的桌面計(jì)算機(jī)CPU、手機(jī)SoC中還集成了許多圖形處理器(GPU)核心、人工智能處理器(APU)核心等,這些是否也應(yīng)該算作多核心CPU和SoC中的“核心”呢?我覺(jué)得從廣義角度上應(yīng)該算吧。

因此,要回顧多核心CPU的發(fā)展,大致可以分為1.雛形期;2. 單芯片單核心;3.單芯片多核心;4.單核心多芯片;5.多核心多芯片幾種情形。這些發(fā)展階段不一定按照這個(gè)前后順序,可能有交叉時(shí)期,也可能有前后顛倒的情形。第2和第3種情形一般是應(yīng)用在桌面計(jì)算機(jī)、智能手機(jī)等移動(dòng)終端上的CPU芯片,第4和第5種是應(yīng)用在服務(wù)器和超級(jí)計(jì)算機(jī)上的CPU芯片。本文限于篇幅和主題集中的需要,主要探討第3種單芯片多核心的情況,這種情況下的CPU是單芯片多處理器(Chip Multi Processors,簡(jiǎn)稱CMP)模式。

1971~2004年,單核心CPU一路獨(dú)行。Intel公司1971年推出全球首款CPU芯片i4004,直到2004年推出超線程的Pentium 4 CPU系列,期間共33年時(shí)間。在這期間,CPU芯片很好地沿著摩爾定律預(yù)示的規(guī)律發(fā)展,沿著集成度不斷翻倍、主頻不斷提升、晶體管數(shù)量快速增加的道路前進(jìn),這是一條單核心CPU不斷迭代升級(jí)的發(fā)展之路。

但是,當(dāng)晶體管數(shù)量大幅增加導(dǎo)致功耗急劇增長(zhǎng),CPU芯片發(fā)熱讓人難以接受,CPU芯片可靠性也受到很大影響的時(shí)候,單核心CPU發(fā)展似乎到了窮途末路。摩爾定律的提出者戈登。摩爾也依稀覺(jué)得“尺寸不斷縮小”、“主頻為王”這條路子即將走到盡頭。2005年4月他曾公開表示,引領(lǐng)芯片行業(yè)接近40年的摩爾定律將在10~20年內(nèi)失效。

其實(shí),早在上世紀(jì)90年代末,就有許多業(yè)界人士呼吁用CMP技術(shù)實(shí)現(xiàn)的多核心CPU替代單線程單核心CPU。IBM、惠普、Sun等高端服務(wù)器廠商,更是相繼推出了多核心服務(wù)器CPU。但是,由于服務(wù)器CPU芯片價(jià)格太高、應(yīng)用面較窄,并未引起大眾廣泛關(guān)注。

2005年初AMD搶先推出了64位CPU芯片,并率先Intel發(fā)表聲明保證其64位CPU的穩(wěn)定性和兼容性,Intel才想起了利用“多核心”這一武器進(jìn)行“帝國(guó)反擊戰(zhàn)”。2005年4月,Intel倉(cāng)促推出簡(jiǎn)單封裝的2核心Pentium D和Pentium4至尊版840。之后不久,AMD也發(fā)布了雙核心皓龍(Opteron)和速龍(Athlon)CPU芯片[9]。

2006年被認(rèn)為是多核心CPU的元年。這年7月23日,Intel基于酷睿(Core)架構(gòu)的CPU發(fā)布。11月,Intel又推出了面向服務(wù)器、工作站和高端PC機(jī)的至強(qiáng)(Xeon)5300和酷睿2雙核心和4核心至尊版系列CPU。與上一代臺(tái)式機(jī)CPU相比,酷睿2雙核心CPU在性能方面提高40%,功耗反而降低40%。

作為對(duì)Intel的回應(yīng),7月24日,AMD宣布對(duì)雙核Athlon64 X2處理器進(jìn)行大降價(jià)。兩大CPU巨頭在宣傳多核心CPU時(shí),都會(huì)強(qiáng)調(diào)其節(jié)能效果。Intel發(fā)布的低電壓版4核心至強(qiáng)CPU功耗僅為50瓦。而AMD的“Barcelona”4核心CPU的功耗也沒(méi)超過(guò)95瓦。在Intel高級(jí)副總裁Pat Gelsinger看來(lái),摩爾定律還是有生命力的,因?yàn)椤癈PU從單核心到雙核心,再到多核心的發(fā)展,可能是摩爾定律問(wèn)世以來(lái),CPU芯片性能提升最快的時(shí)期” [9]。

CPU技術(shù)發(fā)展要比軟件技術(shù)發(fā)展更快,軟件對(duì)多核心CPU的支持相對(duì)滯后。如果沒(méi)有操作系統(tǒng)的支持,多核心CPU的性能提升優(yōu)勢(shì)不能發(fā)揮出來(lái)。同樣運(yùn)行Win7的情況下,4核心CPU和8核心CPU所帶來(lái)的差異化體驗(yàn)并不明顯,導(dǎo)致這種情況的原因是Win7根本沒(méi)有對(duì)8核心CPU進(jìn)行相應(yīng)的優(yōu)化。而在Win10出來(lái)后,8核心CPU所帶來(lái)的體驗(yàn)速度就明顯要比4核心處理器快很多,這源于微軟在Win10上對(duì)多核心CPU的支持做了優(yōu)化。而且微軟還將在Win10上針對(duì)多核心CPU做進(jìn)一步適配優(yōu)化。

目前核心最多的服務(wù)器CPU有Intel至強(qiáng)鉑金9282,56核心112線程,引線焊球多達(dá)5903個(gè),估計(jì)售價(jià)約4萬(wàn)美元;AMD霄龍 7H12,64核心128線程,散熱設(shè)計(jì)功耗280W。這兩款CPU都需要采用液冷散熱。核心最多的臺(tái)式機(jī)CPU有Intel酷睿i97980XE至尊版,18核心36線程,散熱設(shè)計(jì)功耗165W,售價(jià)1999美元;AMD的Ryzen9 5950X,16核心32線程,散熱設(shè)計(jì)功耗105W,售價(jià)6049元。核心最多的手機(jī)SoC有Apple M1、麒麟9000、高通驍龍 888等。多核心CPU或者多核心SoC似乎成為一種潮流,但是不是核心越多CPU就越好呢?在不考慮其它因素影響,單從技術(shù)和集成度考慮的話,有人甚至預(yù)測(cè)到2050年,人們可能會(huì)用上1024個(gè)核心的CPU芯片。

二、多核心CPU和SoC芯片舉例

舉例的芯片包括:1.服務(wù)器用的多核心CPU芯片:Intel Xeon W-3175X;2.桌面PC應(yīng)用的多核心CPU芯片:Intel Corei7-980X;3.智能手機(jī)應(yīng)用的多核心SoC芯片:海思麒麟9000/E;4.ARM架構(gòu)PC應(yīng)用的多核心CPU芯片:AppleM1;5.兼容x86架構(gòu)的多核心AI CPU芯片:威盛CHA;6.多核心國(guó)產(chǎn)服務(wù)器CPU芯片:騰云S2500。

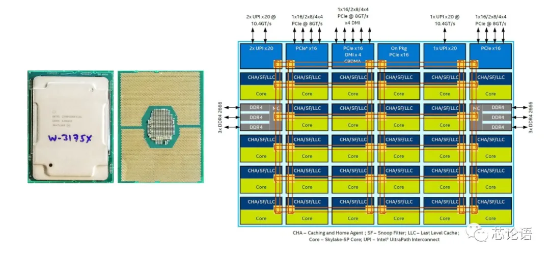

1.Intel至強(qiáng)W-317X: Intel 2018年推出的服務(wù)器CPU芯片Xeon W-3175X,采用14nm工藝制造,28核心56線程,主頻3.1~4.3GHz,三級(jí)緩存38.5MB,內(nèi)存支持六通道DDR4-2666 ECC/512GB,封裝接口LGA3647,搭配芯片組C621。它的售價(jià)高達(dá)2999美元,約合人民幣2萬(wàn)多元。

該芯片采用了全新的6x6網(wǎng)格(Mesh)架構(gòu),I/O位于頂部,內(nèi)存通道在兩側(cè)居中的位置,最多28個(gè)CPU核心,四倍L2Cache(每個(gè)核心的緩存由256KB升級(jí)到1MB),減小了共享L3Cache但提高了利用率。

圖3. Intel Xeon W-3175X的28核心架構(gòu)圖

Xeon W-3175X是該架構(gòu)的最頂級(jí)28個(gè)CPU核心配置。但代價(jià)是超高功耗和發(fā)熱,標(biāo)稱熱設(shè)計(jì)功耗就有255W,默認(rèn)主頻實(shí)測(cè)跑分就能輕松達(dá)到380W,超頻的話甚至?xí)黄?00W。它在日常使用中,高端水冷是必須配備的。Intel在發(fā)布Xeon W-3175X的時(shí)候就特別推薦了Asetek 690LX-PN一體化水冷散熱器,這也是目前唯一針對(duì)W-3175X設(shè)計(jì)的散熱方案。Asetek宣稱該水冷的最大散熱能力達(dá)500W,因此只要不進(jìn)行極限超頻,該方案為W-3175X散熱問(wèn)題不大[13]。價(jià)格399.99美元,約合人民幣2680元。

圖4. Asetek 690LX-PN水冷散熱器(來(lái)源:參考資料13)

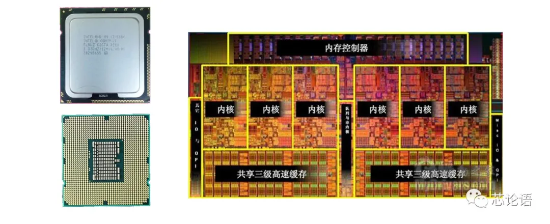

2.Intel酷睿i7-980X:Intel Core i7-980X采用32nm工藝制程和Gulftown核心,是Intel面向桌面PC市場(chǎng)推出的第一顆6核心CPU,相對(duì)之前的Bloomfield核心CPU,工藝更先進(jìn)、核心更多、緩存更大,還保持了很好地向下兼容性,嚴(yán)格來(lái)說(shuō)同屬Nehalem微架構(gòu)衍生產(chǎn)品。尤其是CPU依然采用LGA 1366接口,用戶之前購(gòu)買的X58主板只要升級(jí)Bios便可繼續(xù)支持新版32nm 6核心CPU,體驗(yàn)6核心12線程帶來(lái)的至尊體驗(yàn)。它擁有目前Intel桌面PC高端CPU的所有特性,具備超線程技術(shù)、睿頻加速技術(shù)、三通道DDR3內(nèi)存控制器和三級(jí)緩存配備等,尤其是酷睿i7-980X還沒(méi)有鎖定倍頻,讓超頻用戶能夠以更簡(jiǎn)便的方式挑戰(zhàn)極限[5]。

圖5. Intel Core i7-980X的6核心架構(gòu)圖(來(lái)源:參考資料5)

3.華為麒麟9000:華為Mate40手機(jī)搭載了華為海思自研的麒麟9000芯片,它是目前功能和性能最強(qiáng)5G多核心SoC芯片。參見下圖,該芯片上集成了8個(gè)CPU核心、3個(gè)NPU核心和24個(gè)核心的GPU,采用了5nm的制造工藝,其上集成了153億個(gè)晶體管。它與聯(lián)發(fā)科最強(qiáng)的5G手機(jī)芯片天璣2000相比,性能測(cè)試的跑分明顯占優(yōu)。可惜美國(guó)無(wú)理封堵了華為高端智能手機(jī)芯片的生產(chǎn)渠道,使華為旗艦手機(jī)Mate40系列可能成為絕版。

圖6.華為最強(qiáng)5G手機(jī)芯片麒麟9000的多核心架構(gòu)示意圖

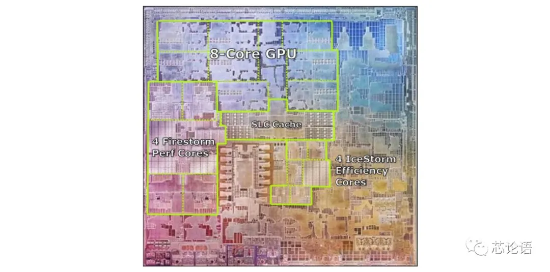

4.AppleM1:下圖是蘋果首款自研的Mac電腦8核心SoC芯片布圖。它具有4個(gè)高效能的冰風(fēng)暴小核心(Icestorm)、4個(gè)高性能火風(fēng)暴大核心(Firestorm)和8核心的GPU。可謂冰火四重天,處理能力十分強(qiáng)勁。該芯片以5nm工藝制造,其上集成了160億個(gè)晶體管。蘋果公司為新處理器系列啟動(dòng)新的SoC命名方案,稱為Apple M1。

圖7.蘋果自研的Mac電腦SoC芯片Apple M1的布圖(來(lái)源:參考資料19)

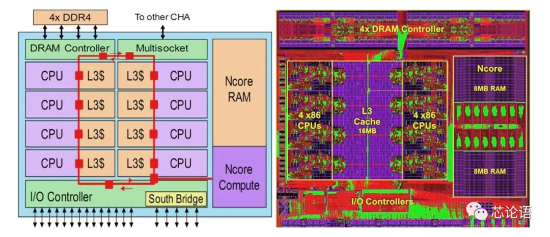

5.VIACHA:威盛(VIA)最新基于x86的AI處理器是一個(gè)8核心SoC,它采用臺(tái)積電16nm工藝制造,芯片面積不超過(guò)195平方毫米,內(nèi)部采用環(huán)形總線設(shè)計(jì),串聯(lián)集成了八個(gè)x86 CPU核心、16MB共享三級(jí)緩存、四通道DDR4-3200內(nèi)存控制器、PCIe 3.0控制器(44條)、南橋和IO功能,是一顆完整的SoC。據(jù)報(bào)道該芯片暫時(shí)命名為CHA。

圖8.威盛的8核心AI處理器的芯片布局(左)和布圖(右)(來(lái)源:參考資料15)

6.騰云S2500:據(jù)報(bào)道[21],國(guó)產(chǎn)CPU廠商飛騰公司7月發(fā)布了一款面向服務(wù)器應(yīng)用的多核心CPU芯片——騰云S2500,該芯片采用16nm工藝制造,芯片面積達(dá)400mm2,最多可配置64個(gè)FTC663架構(gòu)的CPU核心,主頻2.0~2.2GHz,三級(jí)緩存64MB,支持八通道DDR4內(nèi)存,可提供800Gbps帶寬的四個(gè)直連接口,支持2~8路并行,單系統(tǒng)可提供128~512個(gè)CPU核心的配置,熱設(shè)計(jì)功耗為150W。在飛騰2020生態(tài)合作伙伴大會(huì)上,長(zhǎng)城、浪潮、同方、曙光、中興通訊等15家國(guó)內(nèi)廠商也同時(shí)發(fā)布了各自基于騰云S2500的多路服務(wù)器產(chǎn)品,軟件生態(tài)建設(shè)取得了可喜突破。

圖9.飛騰公司64核心CPU芯片騰云S2500 (來(lái)源:網(wǎng)絡(luò)圖片)

三、為什么要采用多個(gè)核心?

我們先從任務(wù)處理的角度來(lái)看這個(gè)問(wèn)題。如果把CPU處理的事情叫做任務(wù)的話,以前的CPU只有一個(gè)核心,CPU只會(huì)“一心一用”地處理一個(gè)任務(wù),干完一件事再接著干下一件事。專業(yè)上稱之為串行單任務(wù)處理。這在DOS操作系統(tǒng)的時(shí)代是合適的,這個(gè)時(shí)期對(duì)CPU的追求只有一條,那就是處理速度要盡可能地快。在Windows操作系統(tǒng)出現(xiàn)后,出現(xiàn)了多任務(wù)的處理需求,要求CPU可以“一心多用”,同時(shí)干多件事情。專業(yè)上稱之為分時(shí)多任務(wù)處理。這個(gè)時(shí)期對(duì)CPU的追求一是處理速度要盡可能地快,二是同時(shí)可處理的任務(wù)盡可能地多。其實(shí)這種“一心多用”的處理方法是把時(shí)間分配給了多個(gè)任務(wù),從宏觀上看CPU處理的任務(wù)多了,但從某項(xiàng)任務(wù)來(lái)看CPU對(duì)該項(xiàng)任務(wù)的處理速度變慢了。

要實(shí)現(xiàn)CPU處理的任務(wù)更多、處理速度更快,人們自然想到了在芯片中集成多個(gè)CPU核心,采用“多心多用”的方式處理事務(wù),因而就出現(xiàn)了多核心CPU的需求,而這種需求在服務(wù)器CPU應(yīng)用方面顯得尤為迫切。

我們?cè)購(gòu)奶岣逤PU時(shí)鐘頻率,加快處理速度的角度來(lái)看這個(gè)問(wèn)題。無(wú)論是“一心一用”、“一心多用”、還是“多心多用”,只要提高了CPU的時(shí)鐘頻率,CPU的處理速度都會(huì)加快。如論是單任務(wù)還是多任務(wù),就會(huì)在更短時(shí)間完成任務(wù)。因此,CPU發(fā)展的歷史就是隨著芯片技術(shù)的進(jìn)步,CPU的時(shí)鐘頻率不斷提升的歷史,從早期的MHz級(jí)別不斷提升到目前的GHz級(jí)別,大約提升了1000倍左右。無(wú)論是單核心還是多核心,CPU時(shí)鐘頻率是人們選用CPU芯片的重要指標(biāo)。

過(guò)去很長(zhǎng)一段時(shí)間里,隨著Intel和AMD CPU速度越來(lái)越快,x86操作系統(tǒng)上的軟件的性能和速度自然會(huì)不斷提高,系統(tǒng)整機(jī)廠家只要對(duì)現(xiàn)有軟件作輕微設(shè)置就能坐享電腦系統(tǒng)整體性能提升的好處。

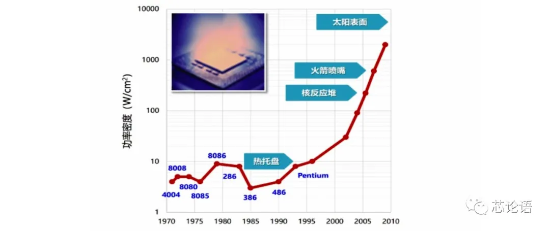

但是隨著芯片工藝沿著摩爾定律發(fā)展,CPU集成度提高、晶體管密度加大,時(shí)鐘頻率提升,直接導(dǎo)致CPU芯片的功率不斷增大,散熱問(wèn)題成為一個(gè)無(wú)法逾越的障礙。據(jù)測(cè)算,CPU主頻每增加1GHz,功耗將上升25瓦,而在芯片功耗超過(guò)150瓦后,現(xiàn)有的風(fēng)冷散熱將無(wú)法滿足要求。2003年前后Intel推出的主頻為3.4GHz的Pentium4至尊版CPU芯片,最高功耗已達(dá)135瓦,有人給它送了一個(gè)“電爐”的綽號(hào),更有好事者用它來(lái)玩煎蛋的游戲。現(xiàn)在的服務(wù)器CPU芯片Xeon W-3175標(biāo)稱功耗為255W,默認(rèn)頻率實(shí)測(cè)能達(dá)到380W,超頻的話甚至?xí)黄?00W,必須采用高端水冷系統(tǒng)來(lái)降溫。

所以,功耗極限制約著CPU頻率的提升。下圖是CPU功率密度隨時(shí)間的變化趨勢(shì)圖,IntelPentium之后的CPU芯片,由于晶體管密度和時(shí)鐘頻率提升,CPU芯片的功率密度陡然上升,CPU產(chǎn)生的熱量將會(huì)超過(guò)太陽(yáng)表面。

圖10. CPU功率密度隨時(shí)間的變化趨勢(shì)圖(來(lái)源:魏少軍教授演講)

綜上所述,追求多任務(wù)處理功能,追求處理速度提升是CPU芯片設(shè)計(jì)的兩大目標(biāo)。以提升CPU時(shí)鐘頻率而加快處理速度又受到CPU功耗極限的制約,多核心CPU芯片成為解決上述矛盾的必由之路。目前,多核心CPU和SoC已成為處理器芯片發(fā)展的主流。

四、多核心CPU用到哪些技術(shù)?

與單核心CPU相比,多核心CPU在體系結(jié)構(gòu)、軟件、功耗和安全性設(shè)計(jì)等方面面臨著巨大的挑戰(zhàn),但也蘊(yùn)含著巨大的潛能。本文參考了后附的參考資料1,對(duì)多核心CPU用到的技術(shù)作如下簡(jiǎn)單介紹。

1.超線程技術(shù)

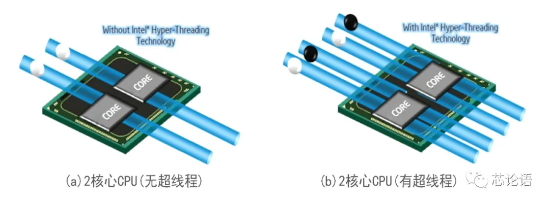

一個(gè)傳統(tǒng)CPU核心只有一個(gè)運(yùn)算處理單元(Processing Unit,簡(jiǎn)稱PU)和一個(gè)架構(gòu)狀態(tài)單元(Architectual State,簡(jiǎn)稱AS),在同一時(shí)間只能處理一個(gè)軟件線程(Thread)。采用了超線程(Hyper-Threading,簡(jiǎn)稱HT)技術(shù)的CPU核心中包含一個(gè)PU和兩個(gè)AS,兩個(gè)AS共用這個(gè)PU。軟件在CPU核心上運(yùn)行時(shí),AS與軟件線程對(duì)接,并把線程的任務(wù)分配到PU中的相關(guān)單元中。所以,兩個(gè)AS就可以處理兩個(gè)軟件線程。

用生產(chǎn)車間打個(gè)比方,PU是生產(chǎn)部門,有幾臺(tái)機(jī)床用于生產(chǎn);AS是跟單員,他同時(shí)只能跟一個(gè)任務(wù)訂單;軟件線程好比是任務(wù)訂單。如果生產(chǎn)車間只有一個(gè)AS時(shí),這個(gè)車間同時(shí)只能處理一個(gè)任務(wù)訂單,PU的有些機(jī)床有事干,有些機(jī)床可能無(wú)事干而閑置。如果有兩個(gè)AS時(shí),就能處理兩個(gè)任務(wù)訂單,并把任務(wù)分配到不同的機(jī)床上去完成。

所以,具有超線程的CPU核心的集成度增加量不大,但有兩個(gè)AS后使它看起來(lái)像兩個(gè)邏輯的CPU核心,就可以同時(shí)處理兩個(gè)軟件線程,大約可以提高40%的處理能力。所以,我們經(jīng)常可以看到CPU芯片廣告,說(shuō)某多核心CPU芯片是N個(gè)核心,2×N個(gè)線程,就是采用了超線程帶來(lái)的好處。否則,如果沒(méi)有采用超線程技術(shù)的話,多核心CPU芯片參數(shù)就只能寫成N個(gè)核心,N個(gè)線程。下圖給出了2核心CPU無(wú)超線程和有超線程的示意圖。

圖11.多核心CPU的超線程的示意圖(來(lái)源:參考資料20)

2.核心結(jié)構(gòu)研究

多核心CPU的結(jié)構(gòu)分成同構(gòu)(homogeneous)多核和異構(gòu)(heterogeneous)多核兩類,同構(gòu)多核是指芯片內(nèi)多個(gè)CPU核心的結(jié)構(gòu)是相同的,而異構(gòu)多核是指芯片內(nèi)多個(gè)CPU核心的結(jié)構(gòu)各不相同。面對(duì)不同的應(yīng)用場(chǎng)景,研究核心結(jié)構(gòu)的實(shí)現(xiàn)方式對(duì)CPU整體性能至關(guān)重要。核心本身的結(jié)構(gòu),關(guān)系到整個(gè)芯片的面積、功耗和性能。怎樣繼承和發(fā)展傳統(tǒng)CPU的成果,也直接影響多核的性能和實(shí)現(xiàn)周期。同時(shí),核心所用的指令系統(tǒng)對(duì)系統(tǒng)的實(shí)現(xiàn)也是很重要的,多核心采用相同的指令系統(tǒng)還是不同的指令系統(tǒng),能否運(yùn)行操作系統(tǒng)等,也是設(shè)計(jì)者要研究的重要問(wèn)題。

3.Cache設(shè)計(jì)技術(shù)

CPU和主存儲(chǔ)器之間的速度差距對(duì)多核心CPU來(lái)說(shuō)是個(gè)突出的矛盾,因此必須使用多級(jí)Cache來(lái)緩解。可分為共享一級(jí)Cache、共享二級(jí)Cache和共享主存三種方式。多核心CPU一般采用共享二級(jí)Cache的結(jié)構(gòu),即每個(gè)CPU核心擁有私有的一級(jí)Cache,并且所有CPU核心共享二級(jí)Cache。

Cache本身的體系結(jié)構(gòu)設(shè)計(jì)直接關(guān)系到系統(tǒng)整體性能。但是在多核心CPU中,共享Cache或獨(dú)有Cache孰優(yōu)孰劣、是否在片上建立多級(jí)Cache、以及建立幾級(jí)Cache等,對(duì)整個(gè)芯片尺寸、功耗、布局、性能以及運(yùn)行效率等都有很大的影響,需要認(rèn)真研究和慎重對(duì)待。同時(shí)還要考慮多級(jí)Cache引發(fā)的一致性問(wèn)題。

4.核心間通信技術(shù)

多核心CPU的各核心同時(shí)執(zhí)行程序,有時(shí)需要在核心之間進(jìn)行數(shù)據(jù)共享與同步,因此硬件結(jié)構(gòu)必須支持CPU核心間的通信。高效通信機(jī)制是多核心CPU高性能的重要保障,比較主流的片上高效通信機(jī)制有兩種,一種是基于總線共享的Cache結(jié)構(gòu),另一種是基于片上的互連結(jié)構(gòu)。

總線共享Cache結(jié)構(gòu)是指每個(gè)CPU核心擁有共享的二級(jí)或三級(jí)Cache,用于保存比較常用的數(shù)據(jù),并通過(guò)核心間的連接總線進(jìn)行通信。它的優(yōu)點(diǎn)是結(jié)構(gòu)簡(jiǎn)單,通信速度高,缺點(diǎn)是基于總線的結(jié)構(gòu)可擴(kuò)展性較差。

片上互連的結(jié)構(gòu)是指每個(gè)CPU核心具有獨(dú)立的處理單元和Cache,各個(gè)CPU核心通過(guò)交叉開關(guān)電路或片上網(wǎng)絡(luò)等方式連接在一起。各個(gè)CPU核心間通過(guò)消息進(jìn)行通信。這種結(jié)構(gòu)的優(yōu)點(diǎn)是可擴(kuò)展性好,數(shù)據(jù)帶寬有保證,缺點(diǎn)是硬件結(jié)構(gòu)復(fù)雜,且軟件改動(dòng)較大。

5.總線設(shè)計(jì)技術(shù)

傳統(tǒng)CPU中,Cache不命中或訪問(wèn)存儲(chǔ)器事件都會(huì)對(duì)CPU的執(zhí)行效率產(chǎn)生負(fù)面影響,而總線接口單元(BIU)的工作效率會(huì)決定此影響的程度。在多核心CPU中,當(dāng)多個(gè)CPU核心同時(shí)要求訪問(wèn)內(nèi)存,或多個(gè)CPU核心內(nèi)私有Cache同時(shí)出現(xiàn)Cache不命中事件時(shí),BIU對(duì)這些訪問(wèn)請(qǐng)求的仲裁機(jī)制效率,以及對(duì)外存儲(chǔ)訪問(wèn)的轉(zhuǎn)換機(jī)制的效率決定了多核心CPU系統(tǒng)的整體性能。

6.針對(duì)多核心的操作系統(tǒng)

對(duì)于多核心CPU,優(yōu)化操作系統(tǒng)的任務(wù)調(diào)度是提升執(zhí)行效率的關(guān)鍵。任務(wù)調(diào)度算法有全局隊(duì)列調(diào)度和局部隊(duì)列調(diào)度之分。前者是指操作系統(tǒng)維護(hù)一個(gè)全局的任務(wù)等待隊(duì)列,當(dāng)系統(tǒng)中有一個(gè)CPU核心空閑時(shí),操作系統(tǒng)就從全局任務(wù)等待隊(duì)列中選取就緒任務(wù)開始在此核心上執(zhí)行。其優(yōu)點(diǎn)是CPU核心利用率較高。后者是指操作系統(tǒng)為每個(gè)CPU核心維持一個(gè)局部的任務(wù)等待隊(duì)列,當(dāng)系統(tǒng)中有一個(gè)CPU核心空閑時(shí),便從該核心的任務(wù)等待隊(duì)列中選取就緒任務(wù)來(lái)執(zhí)行。其優(yōu)點(diǎn)是有利于提高CPU核心局部Cache命中率。大多數(shù)的多核心CPU操作系統(tǒng)采用的是基于全局隊(duì)列的任務(wù)調(diào)度算法。

多核心CPU的中斷處理和單核CPU有很大不同。CPU核心之間需要通過(guò)中斷方式進(jìn)行通信和協(xié)調(diào),所以,CPU核心的本地中斷控制器和仲裁各CPU核心之間中斷的全局中斷控制器需要封裝在芯片內(nèi)部。

另外,多核心CPU操作系統(tǒng)是一個(gè)多任務(wù)系統(tǒng)。由于不同任務(wù)會(huì)競(jìng)爭(zhēng)共享資源,因此需要系統(tǒng)提供同步與互斥機(jī)制。而傳統(tǒng)的用于單核心CPU的解決機(jī)制并不能滿足多核心的情況,需要利用硬件提供的“讀-修改-寫”的原始操作或其他同步互斥機(jī)制來(lái)進(jìn)行保證。

7.低功耗設(shè)計(jì)技術(shù)

每?jī)扇闏PU晶體管密度和功耗密度都會(huì)翻倍。低功耗和熱優(yōu)化設(shè)計(jì)已經(jīng)成為多核心CPU設(shè)計(jì)的重點(diǎn)。需要同時(shí)在操作系統(tǒng)級(jí)、算法級(jí)、結(jié)構(gòu)級(jí)、電路級(jí)等多個(gè)層次上考慮。每個(gè)層次上實(shí)現(xiàn)的效果不同,抽象層次越高,功耗和溫度降低的效果越明顯。

8.可靠性及安全性設(shè)計(jì)技術(shù)

在今天的信息社會(huì),CPU的應(yīng)用無(wú)處不在,對(duì)CPU的可靠性和安全性提出了更高要求。一方面多核心CPU復(fù)雜性提高,低電壓、高主頻、高溫度對(duì)維持芯片安全運(yùn)行帶來(lái)挑戰(zhàn)。另一方面,來(lái)自外界惡意攻擊越來(lái)越多,手段越來(lái)越先進(jìn),高可靠、安全性設(shè)計(jì)技術(shù)越來(lái)越受到重視。

五、多核心CPU是如何工作?

要弄明白多核心CPU是如何工作,要從應(yīng)用程序、操作系統(tǒng)和CPU核心一起來(lái)分析。Windows操作系統(tǒng)作為任務(wù)調(diào)度者,按照進(jìn)程(Process)和線程(Thread)為應(yīng)用程序(Program)分配程序執(zhí)行的硬件資源——CPU核心。一個(gè)進(jìn)程對(duì)應(yīng)一個(gè)應(yīng)用程序,但是一個(gè)應(yīng)用程序可以同時(shí)對(duì)應(yīng)多個(gè)進(jìn)程,通過(guò)多個(gè)進(jìn)程來(lái)完成這個(gè)程序的執(zhí)行。

應(yīng)用程序未執(zhí)行的時(shí)候是“靜態(tài)”的,程序一旦被用戶啟動(dòng)執(zhí)行,就被操作系統(tǒng)接管變成“動(dòng)態(tài)”的了。操作系統(tǒng)按照一個(gè)一個(gè)的進(jìn)程管理著一批被用戶啟動(dòng)了的程序。所以一個(gè)進(jìn)程可以看作是一個(gè)“執(zhí)行中的程序”,進(jìn)程中包括了由操作系統(tǒng)分配給這個(gè)程序的基本資源。

一個(gè)進(jìn)程又被細(xì)分為多個(gè)線程,只有線程才能通過(guò)操作系統(tǒng)獲得CPU核心的使用權(quán)限來(lái)讓自己運(yùn)行。只包含一個(gè)線程的進(jìn)程可以叫做單線程程序,如果包含多個(gè)線程的進(jìn)程,就可以叫做多線程程序了。

程序的線程要想獲得CPU時(shí)間,必須進(jìn)入操作系統(tǒng)的線程隊(duì)列排隊(duì),經(jīng)過(guò)操作系統(tǒng)調(diào)度之后,獲得某個(gè)CPU核心的執(zhí)行時(shí)間。操作系統(tǒng)對(duì)CPU核心的分派是非常復(fù)雜的過(guò)程,誰(shuí)也無(wú)法用簡(jiǎn)短的文字說(shuō)清楚具體詳細(xì)的過(guò)程。以下按單核心CPU和4核心CPU兩種情況來(lái)示意說(shuō)明,程序進(jìn)程的一個(gè)個(gè)線程,是如何分派到CPU核心上進(jìn)行執(zhí)行的[7]。

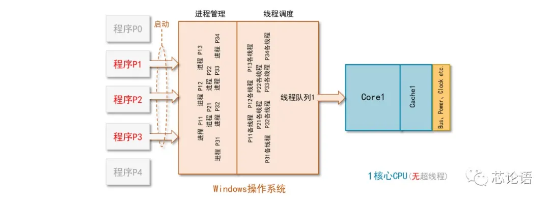

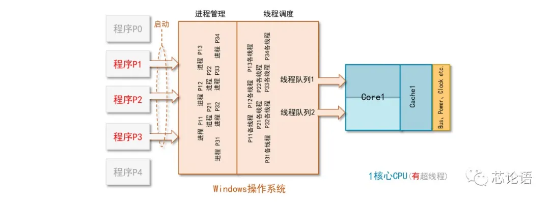

如果CPU是單核心的話,而且沒(méi)有采取超線程技術(shù),線程隊(duì)列就只有1個(gè),線程的選擇也只有1個(gè)。如果采取了超線程技術(shù),單核心就擴(kuò)展成2個(gè)邏輯核心,線程隊(duì)列就有2個(gè),線程的選擇就有2個(gè)。如下圖所示。

圖12.應(yīng)用程序在單核心CPU上按線程調(diào)度執(zhí)行的示意圖(無(wú)超線程)

圖13.應(yīng)用程序在單核心CPU上按線程調(diào)度執(zhí)行的示意圖(有超線程)

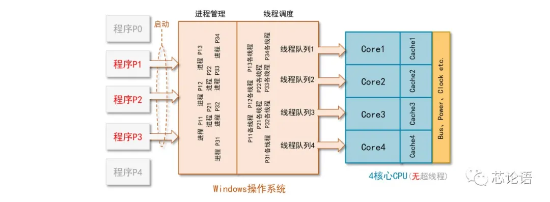

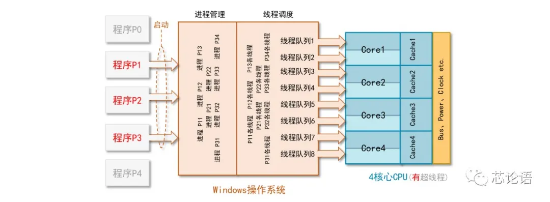

如果CPU是4核心的話,而且沒(méi)有采取超線程技術(shù),線程隊(duì)列就只有4個(gè),線程的選擇也只有4個(gè)。如果采取了超線程技術(shù),4核心就擴(kuò)展成8個(gè)邏輯核心,線程隊(duì)列就有8個(gè),線程的選擇就有8個(gè)。如下圖所示。

圖14.應(yīng)用程序在4核心CPU上按線程調(diào)度執(zhí)行的示意圖(無(wú)超線程)

圖15.應(yīng)用程序在4核心CPU上按線程調(diào)度執(zhí)行的示意圖(有超線程)

如果站在多核心CPU角度看,每個(gè)CPU核心不斷從操作系統(tǒng)收到要執(zhí)行的軟件線程,按照程序指令去完成規(guī)定任務(wù),它可能要使用存儲(chǔ)器、運(yùn)算器、輸入輸出等部件,還要與其它CPU核心進(jìn)行通信和傳遞數(shù)據(jù),完成任務(wù)后還要報(bào)告。這些過(guò)程可看成一個(gè)一個(gè)的事件,都要通過(guò)事件中斷處理部件來(lái)協(xié)調(diào)。多核心CPU的硬件調(diào)度處理模式大致有三種[8][18]。

1.對(duì)稱多處理(Symmetric Multi-Processing,簡(jiǎn)稱SMP)是目前使用最多的模式。在SMP模式下,一個(gè)操作系統(tǒng)同等地管理著各個(gè)CPU核心,并為各個(gè)核心分配工作負(fù)載。目前,大多數(shù)的操作系統(tǒng)都支持SMP模式,例如Linux,Windows,Vxworks等。另外,這種模式通常用在同構(gòu)多核CPU上,因?yàn)楫悩?gòu)多核CPU的結(jié)構(gòu)不同,實(shí)現(xiàn)SMP比較復(fù)雜。

2.非對(duì)稱多處理(Asymmetric Multi-Processing,簡(jiǎn)稱AMP)是指多個(gè)核心相對(duì)獨(dú)立地運(yùn)行著不同的任務(wù),每個(gè)核心可能運(yùn)行不同的操作系統(tǒng)或裸機(jī)程序,或者不同版本的操作系統(tǒng),但是有一個(gè)主導(dǎo)的CPU核心,用來(lái)控制其它從屬的CPU核心以及整個(gè)系統(tǒng)。這種模式大多情況是異構(gòu)多核心CPU。例如MCU + DSP,MCU +FPGA等。當(dāng)然,同構(gòu)多核心CPU也可以用。

3.邊界多處理(Bound Multi-processing,簡(jiǎn)稱BMP)與SMP基本相同,唯一區(qū)別是開發(fā)者可以定義某個(gè)任務(wù)僅在某個(gè)CPU核心上執(zhí)行。

以上只是原理性的簡(jiǎn)單介紹,如果要了解多核心CPU的硬件調(diào)度原理和實(shí)現(xiàn)細(xì)節(jié),恐怕只能打進(jìn)Intel或AMD公司內(nèi)部,才能了解更多技術(shù)詳情。

六、多核心CPU的仁智各見

多核心CPU中的核心是否越多越好,多CPU系統(tǒng)中的CPU芯片是否也越多越好?同樣條件下是否具有超線程就比不具有超線程的好?回答是仁者見仁,智者見智。主要是要分清用在哪些場(chǎng)合,不能一概而論。

首先,多核心CPU或者多CPU之間需要同步和調(diào)度,這是以時(shí)間開銷和算力損耗為代價(jià)的。如果CPU核心數(shù)或者CPU芯片數(shù)增加對(duì)系統(tǒng)處理能力提升是加分項(xiàng)的話,同步和調(diào)度帶來(lái)的時(shí)間開銷和算力損耗就是減分項(xiàng)。如果加分大于減分,而且成本增加可接受的話,則方案是可行的,否則就是不值當(dāng)?shù)姆桨浮O到y(tǒng)方案的評(píng)判除了要考慮CPU核心數(shù)量以外,還要考慮操作系統(tǒng)的差異、調(diào)度算法的不同,應(yīng)用和驅(qū)動(dòng)程序特點(diǎn)等因素,它們共同影響著系統(tǒng)的處理速度。以下是一些文章的討論觀點(diǎn)。

1. CPU核心越多,執(zhí)行速度不一定越快。這里說(shuō)的是“不一定”,因?yàn)橐粋€(gè)線程可能要等待其它線程或進(jìn)程完成后,才能輪到它繼續(xù)執(zhí)行。在它等待別的線程或進(jìn)程的時(shí)候,即便排隊(duì)隊(duì)列輪到了它,它也只能放棄運(yùn)行權(quán)利而繼續(xù)等待,讓隊(duì)列后續(xù)線程超過(guò)它在CPU上執(zhí)行。對(duì)它這個(gè)線程的程序來(lái)說(shuō)是變慢了,但對(duì)系統(tǒng)來(lái)說(shuō),它起碼它讓開了位置讓其它線程繼續(xù)運(yùn)行。多核心CPU肯定可以加速批量進(jìn)程的執(zhí)行,但對(duì)某個(gè)進(jìn)程或者某類型的程序來(lái)說(shuō),未必是最快的。

2.智能手機(jī)要向用戶提供優(yōu)秀的使用體驗(yàn),不僅僅是靠CPU性能一個(gè)方面。除了CPU核心數(shù)這個(gè)因素以外,還應(yīng)包括決定通信質(zhì)量的基帶芯片的性能,再加上GPU的性能、游戲和VR應(yīng)用性能等。系統(tǒng)綜合性能好才是真的好。

3.聯(lián)發(fā)科2015年推出10核心、3重架構(gòu)等手機(jī)SoC芯片技術(shù),后來(lái)又開發(fā)了10核心、4重架構(gòu)helio X30,通過(guò)多重架構(gòu)的方式來(lái)降低功耗。雖然聯(lián)發(fā)科在多核心SoC方面的技術(shù)優(yōu)勢(shì)是毋庸置疑,但是高通在2015年底推出了僅有四個(gè)核心的驍龍820芯片,蘋果手機(jī)較早使用的SoC芯片也不過(guò)是雙核心而已。這些都表明,對(duì)于智能手機(jī)而言,多核心CPU或SoC的意義到底大不大,不可絕對(duì)斷言,需要從系統(tǒng)角度分析才能得出正確結(jié)論。

結(jié)語(yǔ):多核心CPU和SoC是為了滿足整機(jī)系統(tǒng)對(duì)處理能力和處理速度不斷提升的需求,在單核心CPU沿著摩爾定律向前發(fā)展,受到了芯片功率極限阻礙時(shí),人們不得不選擇的一種突破路線。多核心CPU推動(dòng)著操作系統(tǒng)的更新和升級(jí),操作系統(tǒng)又決定了多核心CPU效能的發(fā)揮。多核心CPU技術(shù)的難點(diǎn)是多核心之間的信息傳遞、數(shù)據(jù)同步和任務(wù)調(diào)度等。系統(tǒng)性能優(yōu)劣不能只考慮CPU核心數(shù)量,還要考慮操作系統(tǒng)、調(diào)度算法、應(yīng)用和驅(qū)動(dòng)程序等。多核心CPU技術(shù)和FinFET等3D芯片技術(shù)可以看作是延續(xù)摩爾定律生命的兩大關(guān)鍵技術(shù)。