一款理想的神經(jīng)網(wǎng)絡(luò)芯片是什么樣的?按照工程師的說法,最重要的是在芯片本身上擁有大量的存儲(chǔ)空間。這是因?yàn)閿?shù)據(jù)傳輸(從主內(nèi)存到處理器芯片)通常消耗最多的能量,并且會(huì)產(chǎn)生大部分的系統(tǒng)滯后,即使與AI計(jì)算本身相比也是如此。

有鑒于此,Cerebras Systems通過制造一臺(tái)幾乎完全由一個(gè)包含18 GB內(nèi)存的大型芯片組成的計(jì)算機(jī),解決了這些問題(統(tǒng)稱為內(nèi)存墻)。

但是法國,硅谷和新加坡的研究人員提出了另一種方法。

一家稱為Illusion的公司使用在硅邏輯之上構(gòu)建的3D堆棧中使用由電阻性RAM存儲(chǔ)器構(gòu)建的處理器來執(zhí)行相關(guān)操作,因此花費(fèi)很少的精力或時(shí)間來獲取數(shù)據(jù)。

僅憑其本身,還不夠,因?yàn)樯窠?jīng)網(wǎng)絡(luò)的規(guī)模越來越大,無法容納在一個(gè)芯片中。因此,該方案還需要多個(gè)此類混合處理器以及一種算法,該算法既可以智能地對處理器之間的網(wǎng)絡(luò)進(jìn)行分割,還可以知道何時(shí)在閑置時(shí)迅速關(guān)閉處理器。

在測試中,八芯片版本的Illusion的能耗和延遲約為“理想”處理器的3-4%,該處理器在一塊芯片上具有所有需要的內(nèi)存和處理能力。

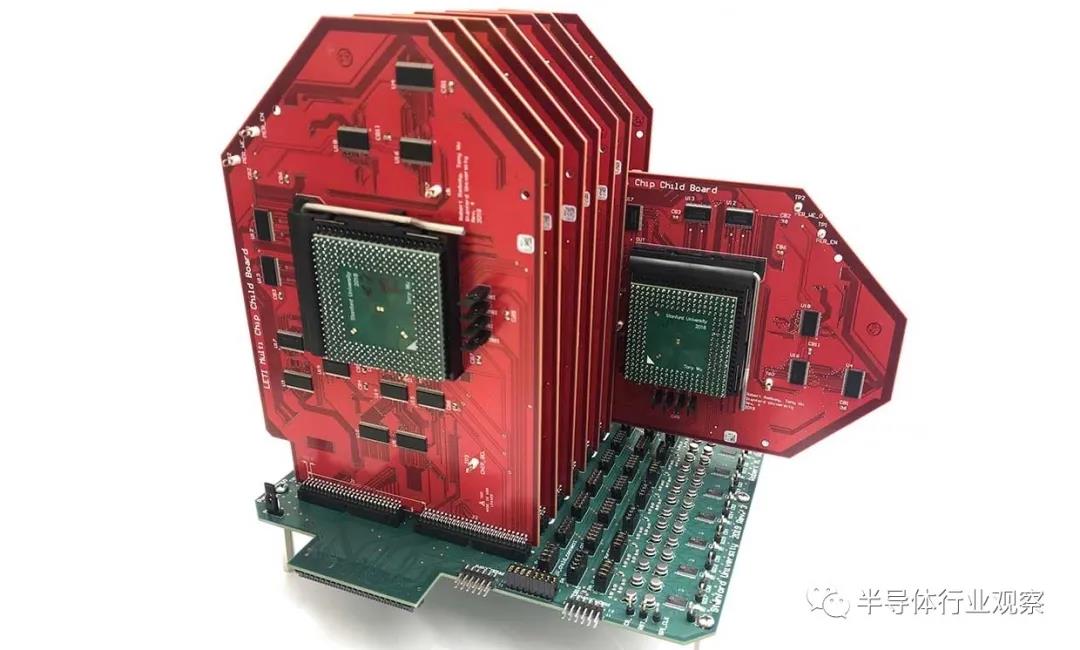

該研究團(tuán)隊(duì)(其中包括來自法國CEA-Leti研究實(shí)驗(yàn)室,F(xiàn)acebook,新加坡南洋理工大學(xué),圣何塞州立大學(xué)和斯坦福大學(xué)的貢獻(xiàn))受到了神經(jīng)網(wǎng)絡(luò)規(guī)模不斷擴(kuò)大這一事實(shí)的推動(dòng)。

負(fù)責(zé)這項(xiàng)研究的斯坦福大學(xué)電氣工程和計(jì)算機(jī)科學(xué)教授Subhasish Mitra說:“從某種意義上講,這種理想的芯片永遠(yuǎn)無法使用,因?yàn)樗且粋€(gè)不斷發(fā)展的目標(biāo)。” 他說:“神經(jīng)網(wǎng)絡(luò)變得越來越快,其速度超過了摩爾定律。”

因此,他們設(shè)法設(shè)計(jì)一種系統(tǒng),使它實(shí)際上是由多個(gè)混合處理器組成,它也會(huì)產(chǎn)生一個(gè)帶有大量片上存儲(chǔ)器的單個(gè)處理器的錯(cuò)覺(illusion),因此他們將其命名為為項(xiàng)目名)。這樣,Illusin就可以輕松擴(kuò)展以適應(yīng)不斷增長的神經(jīng)網(wǎng)絡(luò)。

Mishra解釋說,這樣的系統(tǒng)需要做到三件事:

首先是芯片上的大量內(nèi)存,可以快速訪問而幾乎不消耗能量。這就是集成3D的RRAM發(fā)揮功效的地方。他們選擇了RRAM,“因?yàn)樗敲芗模?D集成的,并且可以在掉電狀態(tài)下快速訪問,并且因?yàn)樗跀嚯姇r(shí)不會(huì)丟失數(shù)據(jù), ” 斯坦福大學(xué)電氣工程學(xué)教授,該項(xiàng)目的合作者Philip Wong說。

但是RRAM確實(shí)有一個(gè)缺點(diǎn)。像Flash存儲(chǔ)器一樣,它被覆蓋過多次后就會(huì)損耗。在Flash中,軟件會(huì)跟蹤每個(gè)存儲(chǔ)單元塊發(fā)生了多少次覆蓋,并試圖保持該數(shù)量,即使在芯片中的所有單元中也是如此。斯坦福大學(xué)理論計(jì)算機(jī)科學(xué)家 Mary Wootters 領(lǐng)導(dǎo)團(tuán)隊(duì)為RRAM發(fā)明了類似的東西。結(jié)果稱為Distributed Endurer,這增加了確保寫入時(shí)的磨損甚至跨越多個(gè)芯片的負(fù)擔(dān)。

即使使用Endurer混合RRAM和處理器芯片,但強(qiáng)大的神經(jīng)網(wǎng)絡(luò)(例如當(dāng)今使用的自然語言處理器)仍然太大,讓我們無法將其容納在一個(gè)芯片中。然而使用多個(gè)混合芯片意味著在它們之間傳遞消息,消耗能量并浪費(fèi)時(shí)間。

Illusion團(tuán)隊(duì)的解決方案是其技術(shù)的第二部分,其解決方案是以使消息傳遞最小化的方式來切割神經(jīng)網(wǎng)絡(luò)。神經(jīng)網(wǎng)絡(luò)本質(zhì)上是一組計(jì)算發(fā)生的節(jié)點(diǎn)以及連接它們的邊。每個(gè)網(wǎng)絡(luò)將具有某些節(jié)點(diǎn)或節(jié)點(diǎn)的整個(gè)層,它們具有大量的連接。

但是網(wǎng)絡(luò)中也將存在阻塞點(diǎn),即在節(jié)點(diǎn)之間必須傳遞少量消息的地方。在這些阻塞點(diǎn)上劃分大型神經(jīng)網(wǎng)絡(luò),并將每個(gè)部分映射到單獨(dú)的芯片上,可確保從一個(gè)芯片到另一個(gè)芯片的數(shù)據(jù)傳輸量最少。Mitra說,Illusion映射算法“自動(dòng)識(shí)別切割神經(jīng)網(wǎng)絡(luò)的理想位置,以最小化這些消息。”

但是像這樣切割的東西有其自身的后果。

不可避免地,一種芯片會(huì)先于另一種芯片來完成其業(yè)務(wù),這會(huì)拖延系統(tǒng)并浪費(fèi)功耗。其他嘗試運(yùn)行超大型神經(jīng)網(wǎng)絡(luò)的多芯片系統(tǒng),則以使所有芯片持續(xù)忙碌的方式來劃分網(wǎng)絡(luò),但這是以在它們之間傳輸更多數(shù)據(jù)為代價(jià)的。

在第三項(xiàng)創(chuàng)新中,Illusion團(tuán)隊(duì)決定設(shè)計(jì)混合處理器及其控制算法,以便可以快速關(guān)閉和打開芯片。因此,當(dāng)芯片等待工作時(shí),它不會(huì)消耗任何功耗。

Mishra說,CEA-Leti的3D RRAM技術(shù)是制造3D SoC的關(guān)鍵,該SoC可以在幾個(gè)時(shí)鐘周期內(nèi)完全關(guān)閉并重新啟動(dòng)而不會(huì)丟失數(shù)據(jù)。

該團(tuán)隊(duì)構(gòu)建了八芯片版本的Illusion,并在三個(gè)深度神經(jīng)網(wǎng)絡(luò)上進(jìn)行了測試。這些網(wǎng)絡(luò)遠(yuǎn)不及當(dāng)前正在計(jì)算機(jī)系統(tǒng)運(yùn)行的網(wǎng)絡(luò)的規(guī)模,因?yàn)槊總€(gè)Illusion原型僅為神經(jīng)網(wǎng)絡(luò)數(shù)據(jù)保留了4 KB的RRAM。他們測試過的“理想芯片”實(shí)際上是一個(gè)模仿了完整神經(jīng)網(wǎng)絡(luò)執(zhí)行的illusion 芯片。

8片幻覺系統(tǒng)能夠在理想芯片能耗的3.5%和2.5%的執(zhí)行時(shí)間內(nèi)運(yùn)行神經(jīng)網(wǎng)絡(luò)。Mitra指出,該系統(tǒng)可以很好地?cái)U(kuò)展。有4 GB RRAM的64芯片illusion 方案的仿真也接近理想。

“我們已經(jīng)展開了新的更強(qiáng)大的原型設(shè)計(jì)”,斯坦福大學(xué)的研究生Robert Radway說。他們也將其發(fā)表在本周的自然電子上。與原型相比,下一代芯片將具有更大數(shù)量級(jí)的內(nèi)存和計(jì)算能力。雖然第一代經(jīng)過了推理的測試,但下一代將用于訓(xùn)練它們,這是一項(xiàng)艱巨的任務(wù)。

“總的來說,我們認(rèn)為illusion 對未來技術(shù)具有深遠(yuǎn)的影響,” Radway說。“它為技術(shù)創(chuàng)新開辟了廣闊的設(shè)計(jì)空間,并為未來的系統(tǒng)創(chuàng)造了新的擴(kuò)展途徑。”