雷達數(shù)據(jù)處理平臺是雷達系統(tǒng)的重要組成部分,隨著現(xiàn)代相控陣雷達任務對運算處理速度、系統(tǒng)響應時間、總線傳輸帶寬、數(shù)據(jù)處理能力等需求不斷提高,傳統(tǒng)雷達數(shù)據(jù)處理系統(tǒng)已經(jīng)很難滿足技術發(fā)展的要求。提出了一種基于VPX總線的雷達數(shù)據(jù)處理平臺設計方案,重點介紹了數(shù)據(jù)處理平臺的組成和各功能模塊的設計原理。該數(shù)據(jù)處理平臺具有通用化、模塊化、易擴充、可靠性高等特點,經(jīng)過實際雷達的工程驗證,性能優(yōu)越,穩(wěn)定可靠。

數(shù)據(jù)處理系統(tǒng)是雷達整機的重要組成部分,其任務是完成雷達點跡和航跡跟蹤處理、雷達時間和能量資源的調度管理和目標情報顯示,并將目標參數(shù)進行通信上報。數(shù)據(jù)處理平臺是數(shù)據(jù)處理系統(tǒng)軟件工作運行的硬件載體,其設計的先進性、穩(wěn)定性和可靠性對雷達整體性能的提升具有至關重要的作用。

VPX圖片來自互聯(lián)網(wǎng)

隨著現(xiàn)代相控陣雷達任務對目標運算處理速度、系統(tǒng)響應時間、總線傳輸帶寬、數(shù)據(jù)處理能力和高可靠性等需求不斷提高,傳統(tǒng)雷達數(shù)據(jù)處理系統(tǒng)已經(jīng)很難滿足技術發(fā)展的要求。基于VPX架構的數(shù)據(jù)處理平臺具備強大的數(shù)據(jù)處理能力、高性能網(wǎng)絡交換能力以及豐富的I/O 接口能力。因此,VPX架構代表了新一代雷達數(shù)據(jù)處理平臺系統(tǒng)的發(fā)展趨勢和方向。鑒于此,本文結合某項目實際應用,主要介紹一種基于VPX架構的雷達數(shù)據(jù)處理平臺的設計。

1 數(shù)據(jù)處理平臺的設計

1。1 系統(tǒng)功能需求和平臺設計思路

現(xiàn)代雷達數(shù)據(jù)處理系統(tǒng)的主要功能是:完成雷達目標點跡、航跡的實時處理;完成雷達時間和能量資源的調度管理;完成雷達回波顯示和目標點跡、航跡信息顯示;雷達目標情報信息的通信上報。

為了實現(xiàn)雷達數(shù)據(jù)處理系統(tǒng)的優(yōu)越性能,結合VPX總線的特點,基于VPX總線架構的雷達數(shù)據(jù)處理平臺設計思路是:

1)運用高性能VPX計算刀片,利用其高速數(shù)據(jù)運算能力,實時完成雷達大容量目標的點跡處理和航跡跟蹤等運算處理和信息顯示;

2)充分運用VPX 總線的高速傳輸性能,實現(xiàn)雷達內外部數(shù)據(jù)的高速實時傳輸和交換;

3)利用VPX總線的低時延特性,實現(xiàn)相控陣雷達波束實時編排和掃描;

4)利用VPX 可帶電熱插拔、結構緊湊抗震性好等優(yōu)點,可在復雜惡劣環(huán)境下可靠工作,從而實現(xiàn)系統(tǒng)高可靠性。

1。2 平臺的總體設計

根據(jù)雷達數(shù)據(jù)處理系統(tǒng)的功能需求和平臺的設計思路,基于VPX總線架構的高性能雷達數(shù)據(jù)處理平臺的總體設計如圖1所示,由多塊VPX功能板卡組成,主要包括VPX計算刀片、VPX架構的時序接口板、VPX通信處理計算機、VPX顯示計算機、交換刀片以及平臺底板。該平臺設計按功能劃分為3個功能處理單元:

1)數(shù)據(jù)處理單元由兩塊高性能VPX計算機板組成,完成雷達大容量目標的點跡處理和航跡跟蹤等數(shù)據(jù)處理功能。

2)任務管理單元 主要由1塊VPX計算機板、1塊VPX架構的時序接口板和1塊VPX通信處理計算機,完成雷達回波信號的接收和轉發(fā)、雷達情報信息的通信上報。VPX計算機板和時序接口板通過高速SRIO(Serial RapidIO)總線連接,實現(xiàn)數(shù)據(jù)的高速傳輸和實時控制。

3)顯控處理單元 主要由3塊VPX顯示計算機組成。顯示計算機通過SRIO總線和千兆網(wǎng)與航跡計算機和波束調度計算機互聯(lián),實現(xiàn)雷達回波數(shù)據(jù)和點跡、航跡數(shù)據(jù)的傳輸,完成雷達的回波顯示、點航跡顯示以及人機交互等功能。

上述3個功能處理單元通過交換刀片,實現(xiàn)數(shù)據(jù)交互,使VPX數(shù)據(jù)處理平臺具有易于擴充、便于維護等優(yōu)點。

圖1 數(shù)據(jù)處理平臺的總體設計

1。3 平臺組成單元的詳細設計

1。3。1 時序接口板

時序接口板為符合VPX 總線標準的6U 插件,該板卡硬件原理框圖如圖2所示。FPGA芯片采用高性能FPGA,容量大,處理速度快,支持高速傳輸。本設計中選用的芯片型號為EP2SGX90FF1508,器件中等價邏輯單元(LE)高達90 960個,片內存儲器達到4。3Mbit,可滿足對存儲器要求較多的應用。時序接口板主要功能電路模塊包括匹配驅動電路、VPX高速總線接口電路、系統(tǒng)對時、方位信息處理、光電轉換電路、FPGA外圍電路等。除匹配驅動電路、光電轉換電路、FPGA外圍電路外,相關功能處理模塊均在FPGA內部實現(xiàn)。時序接口板主要完成以下功能:

圖2 時序接口板設計原理

1)通過SRIO 總線,接收來自波束調度計算機的控制參數(shù),產(chǎn)生雷達整機時序,并可通過TTL或RS422電平送出,波束編排信息可通過光纖輸出至其他分系統(tǒng)。

2)接收來自時統(tǒng)系統(tǒng)的秒脈沖信號和時間信息,完成整機時統(tǒng)設計,為雷達各分系統(tǒng)提供統(tǒng)一的時間基準。

3)根據(jù)雷達各種工作模式,完成雷達頻率源的變頻控制功能。

時序接口板對外信號接口如下:1路SRIO×4接口;12路光纖入/出,每路光纖最高傳輸速率可達6。375Gbit/s;128 路TTL 電平接口;64 路RS422電平接口。

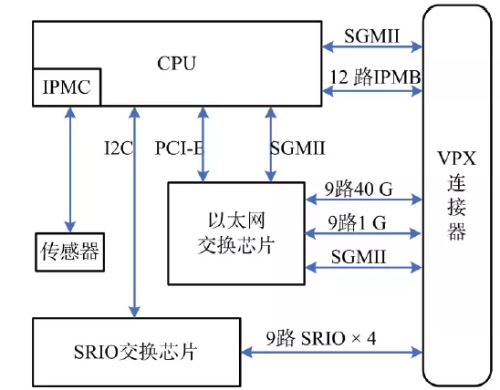

1。3。2 VPX計算機板

計算機板在本數(shù)據(jù)處理平臺中擔任兩個角色:

1)作為數(shù)據(jù)處理計算機,完成雷達點跡處理和航跡跟蹤任務;

2)作為波束調度計算機和通信處理計算機,完成雷達資源管理、波束調度處理和通信控制功能。

VPX計算機板主要性能指標如下:

1)處理器性能:Intel Xeon E5處理器或以上,單個CPU為12核或以上,單精度浮點理論峰值計算能力≥490GFLOPS;

2)內存:容量≥32GB;

3)SRIO傳輸接口:2路SRIO 5G×4接口;

4)網(wǎng)絡接口:不少于3路千兆以太網(wǎng);

5)40G以太網(wǎng)接口:2路40G以太網(wǎng)接口;

6) 管理與監(jiān)控:2路IPMB(IntelligentPlatform Management Bus)接口。

1。3。3 VPX顯示計算機

顯示計算機是一款基于通用處理器和高性能GPU的VPX計算機,通用處理器負責業(yè)務數(shù)據(jù)流的管控和調度,GPU負責2D/3D圖形計算。顯示計算機主要性能指標如下:

1)處理器 性能優(yōu)于Intel CoreTM I7處理器及以上,主頻2。2GHz及以上;

2)內存 板載32GB DDR3雙通道內存,數(shù)據(jù)速率1333MHz以上;

3)GPU 控制器 AMDRadeon E6760嵌入式顯示控制器,4GB獨立顯存,驅動接口符合OpenGL2。2 及以上和OpenGL4。2標準,支持2D/3D硬件加速;

4)顯示分辨率 最高分辨率1 920×1 200@60Hz,支持1920×1 080,1 600×1 200等常用分辨率。

顯示計算機通過40G以太網(wǎng)與航跡計算機、波束調度計算機和通信處理計算機進行雷達點/航跡信息、波束調度指令和雷達通信控制信息的交換;完成雷達參數(shù)顯示、二維顯示、三維顯示和監(jiān)控信息顯示,接收顯控臺輸入指令,完成人機交互功能。顯示計算機通過SRIO 總線接收來自信號處理送來的回波數(shù)據(jù),通過回波顯示軟件模塊實現(xiàn)雷達的原始回波的顯示。顯示計算機的功能框圖如圖3所示。

圖3 顯示計算機功能框圖

1。3。4 交換刀片

本數(shù)據(jù)處理平臺交換刀片的主要功能包括兩個部分:數(shù)據(jù)分發(fā)和機箱管理。

1)數(shù)據(jù)分發(fā):交換刀片支持SRIO 和以太網(wǎng)雙交換,負責建立平臺內各計算機之間以及各計算機與外部其他設備之間的通信鏈路。以太網(wǎng)交換支持千兆以太網(wǎng)和40G以太網(wǎng)交換。

2)機箱管理:交換刀片負責整個數(shù)據(jù)處理平臺的監(jiān)控和管理,收集各功能模塊的電壓、溫度和工作狀態(tài)等參數(shù)信息,據(jù)此進行風扇調速和設備切換等管理。交換刀片的原理框圖如圖4所示。

圖4 交換刀片原理框圖

1。3。5 平臺背板設計

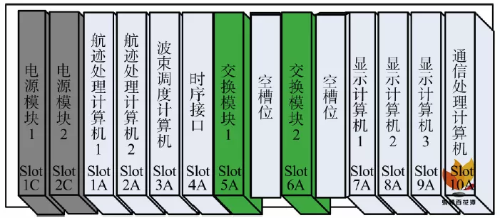

根據(jù)數(shù)據(jù)處理平臺各處理單元的任務劃分和各處理板卡的性能特點,進行平臺印制背板的設計。分機高度為6U,19英寸寬度,共有16個槽位。槽位布局如圖5所示,具體分布如下:最左側4個槽位為兩個電源模塊;背板中間為兩個交換模塊,同時工作,互為備份;交換模塊左側為航跡處理計算機、波束調度計算機和時序接口槽位;交換模塊右側為3個顯示計算機槽位和通信處理計算機槽位。這種采用將交換板放置在中間的布局設計,可方便背板信號的互連互通。

圖5 數(shù)據(jù)處理平臺底板板卡的槽位布局

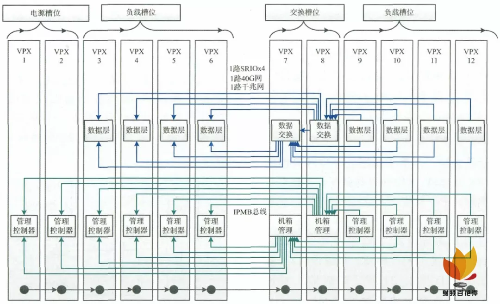

背板信號互聯(lián)示意圖如圖6所示,主要信號連接關系如下:

圖6 數(shù)據(jù)處理平臺背板信號互聯(lián)示意圖

1)平臺供電設計 電源槽位為各功能板卡提供+12V 的電源;

2)高速信號互聯(lián)各功能模塊通過交換模塊實現(xiàn)1路SRIO×4交換;

數(shù)據(jù)處理平臺的內外接口設計示意圖如圖7所示。

圖7 數(shù)據(jù)處理平臺內外接口示意圖

各功能模塊除時序接口模塊外,通過交換模塊實現(xiàn)1路40G以太網(wǎng)和1路千兆以太網(wǎng)交換。

1。4 平臺內外接口設計

1)內部接口設計:平臺內部各功能板卡通過交換模塊實現(xiàn)SRIO、40G以太網(wǎng)和千兆網(wǎng)接口互連,進行數(shù)據(jù)交互和傳輸。

2)對外接口設計:光纖接口主要用于接收雷達回波數(shù)據(jù),發(fā)送波束調度參數(shù)等;網(wǎng)絡接口主要用于接收信號處理送來的雷達點跡參數(shù)等信號,發(fā)送控制指令至其他雷達分系統(tǒng);時統(tǒng)接口接收來自北斗/GPS等時統(tǒng)設備送來的時統(tǒng)信號;時序輸出接口輸出TTL電平或RS422電平的時序信號至其他分系統(tǒng)。

2 平臺設計的關鍵技術

2。1 VPX總線技術的開發(fā)和應用

在雷達數(shù)據(jù)處理平臺的工程設計中,時序接口板、航跡計算機板、通信處理計算機板、顯示計算機板和平臺印制背板全部基于標準VPX總線架構和協(xié)議設計。各功能板卡通過高速串行SRIO總線或者40G以太網(wǎng)實現(xiàn)大容量數(shù)據(jù)的高速交換,突破了傳統(tǒng)地面雷達的數(shù)據(jù)處理平臺并行低速總線為主的技術路線。VPX 總線是基于VITA46協(xié)議的新一代工業(yè)總線標準,采用了最新的接插件技術和高速串行技術,其傳輸速度快,理論傳輸速率可達10Gbit/s,實時響應好,可顯著提升系統(tǒng)實時處理和控制性能;VPX采用專用的RT2高速高密度接插件,可提供更多的自定義信號,擴展性強;同時VPX總線支持熱插拔,也便于系統(tǒng)維護,全面提升平臺性能。

2。2 基于物理位置的板卡槽位自動識別技術

在數(shù)據(jù)處理平臺的總體設計中,航跡處理計算機和通信處理計算機的硬件板卡是相同的,3塊顯示計算機對應不同的任務席位,但其硬件板卡也是相同的。以上各功能計算機板卡通過運行各自的應用程序來實現(xiàn)航跡處理、通信處理、顯示處理等不同的任務。各計算機板卡運行的操作系統(tǒng)也是不同的。例如,波束調度計算機和通信處理計算機因實時性要求采用嵌入式實時操作系統(tǒng);顯示計算機因便于雷達界面顯示和人機交互采用Windows桌面操作系統(tǒng)。為了實現(xiàn)各種不同功能的計算機板卡在同一數(shù)據(jù)處理平臺中混合使用,需要采用板卡槽位自動識別技術來解決以上問題。具體實現(xiàn)如下:

1)在平臺背板上的各個計算機板卡槽位設計硬件撥碼開關,本平臺共有7塊計算機板卡,需要采用三位二進制撥碼開關。

2)依序對各計算機槽位的撥碼開關進行編碼設置,如圖5所示,2塊航跡計算機、1塊波束調度計算機、3塊顯示計算機和1塊通信處理計算機依次編碼為000,001,010,011,100,101和110。

3)計算機在啟動后,首先識別該槽位已分配的硬件編碼值,根據(jù)編碼值在引導區(qū)自動選擇運行對應的操作系統(tǒng)和工作軟件,同時根據(jù)已分配的槽位編碼,各應用軟件自動實現(xiàn)本計算機板卡IP地址的分配,可避免IP地址沖突等問題。

3 結束語

本雷達數(shù)據(jù)處理平臺在設計中采用了先進的VPX總線技術,合理劃分并設計了各功能模塊,具有高性能、模塊化設計、數(shù)據(jù)傳輸速率高、設備易于擴充等技術特點,同時具有較高的可靠性。能適應現(xiàn)代大規(guī)模相控陣雷達對數(shù)據(jù)處理的計算能力和外部接口的需求。本數(shù)據(jù)處理平臺主要性能指標為:

1)數(shù)據(jù)處理能力 點跡處理能力10000點/10秒,航跡處理能力1000批/10秒;

2)顯示能力能對雷達目標進行P顯、A顯、B顯和三維顯示;

3)對外接口能力具備網(wǎng)絡和光纖等數(shù)據(jù)接口,支持TTL,RS422等硬件接口。該雷達數(shù)據(jù)處理平臺已成功應用于工程項目中,通過各種環(huán)境試驗和測試驗證,性能優(yōu)越,穩(wěn)定可靠。

VPX總線以其超大帶寬、高速傳輸能力和高可靠性成為了軍用新一代總線的較佳選擇,將會得到越來越廣泛的應用。(參考文獻略)