因?yàn)楣跔畈《镜拇罅餍校?a class="innerlink" href="http://forexkbc.com/tags/Arm" target="_blank">Arm的年度技術(shù)日活動采取了線上舉辦的模式。在今年的會上,他們正式揭開了全新Neoverse內(nèi)核和處理器設(shè)計的神秘面紗。這些新的內(nèi)核和處理器設(shè)計將被渴望加入的人采用和修改,用于挑戰(zhàn)X86處理器的霸主地位。眾所周知,在現(xiàn)在的數(shù)據(jù)中心和邊緣處理器中,Intel和AMD的CPU建立了相當(dāng)堅固的地位。

從發(fā)布會上我們可以看到,未來的Neoverse服務(wù)器體系結(jié)構(gòu)與一個月前發(fā)布的未來Armv9-A體系結(jié)構(gòu)緊密結(jié)合,并將在Neoverse“ Perseus” N2內(nèi)核中首次亮相。盡管有許多Arm服務(wù)器芯片供應(yīng)商離開了該領(lǐng)域,但Arm Holdings卻一直呆在那里,似乎有許多芯片設(shè)計人員和供應(yīng)商為Arm替代方案提供動力。

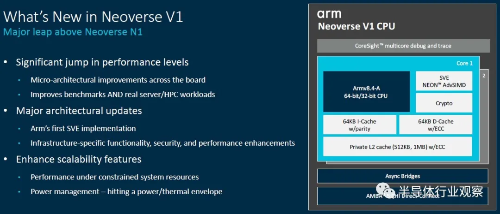

像Neoverse N2內(nèi)核一樣,它的設(shè)計已經(jīng)完成并且可以從Arm Holdings獲得許可,“ Zeus” V1內(nèi)核也已經(jīng)完成,并且在Neoverse設(shè)計系列以及數(shù)據(jù)中心和邊緣的各種CPU中提供了顯著的差異。

實(shí)際上,雖然我們還不知道,但在今年下半年和明年年初的某個時候,我們應(yīng)該可以看到不止一個基于Arm Holdings的Zeus和Perseus平臺打造的的處理器。

在本文中,我們將分別探討Arm在服務(wù)器市場的性能和前景。首先,我們將僅介紹V1和N2架構(gòu)。這是對原始Neoverse平臺路線圖的回顧:

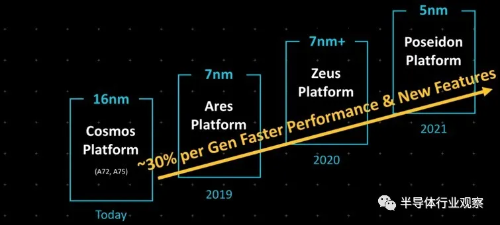

當(dāng)Arm的Neoverse最早于2018年10月提出時,那時Arm的想法是希望能擁有專門針對服務(wù)器的專用IP。而在當(dāng)時,只有16納米的“ Cosmos” N0(實(shí)際上是Cortex-A72和Cortex-A75)設(shè)計,7納米的“Ares”原計劃于2019年面世,使用增強(qiáng)型7納米工藝的“Zeus” 則在2020年面世,5納米的“Poseidon”在2021年。

Arm說,它在每年的設(shè)計中可以提供30%的性能提高約,合作伙伴也可以利用它們在自己的服務(wù)器路線圖中創(chuàng)建的年度節(jié)奏。

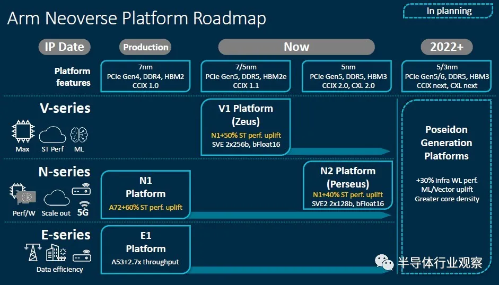

然而事實(shí)證明,這種年度節(jié)奏被證明是棘手的,而且數(shù)據(jù)中心市場已經(jīng)分為核心數(shù)據(jù)中心(N系列),邊緣計算(E系列)和非常高性能(V系列)核心。為此Arm似乎把Zeus N2重新命名為Perseus N2,然后在V1高性能芯片上增加了很多功能,并賦予了舊的Zeus新代號。

去年9月,當(dāng)Arm推出Neoverse V1設(shè)計并將其投入使用時,N2設(shè)計尚不可用。兩大Arm服務(wù)器芯片Ampere Computing Altra和Amazon Web Services Graviton2均是基于N1內(nèi)核和平臺設(shè)計,并進(jìn)行了各種自定義。N1設(shè)計支持常規(guī)DDR4內(nèi)存或HBM2堆疊內(nèi)存,以及PCI-Express 4.0外圍控制器和CCIX 1.0互連器(用于加速器),并在處理器之間提供NUMA共享內(nèi)存。CCIX是許多互連中的一種,以提供CPU和加速器之間的緩存一致性內(nèi)存共享。Arm從一開始就與CCIX一起使用,并一直將其用作CPU互連,就像AMD具有Infinity Fabric(PCI-Express的超集或HyperTransport的子集,取決于您如何看待它)一樣。英特爾CXL的非對稱內(nèi)存模型也被加速器所采用,并運(yùn)行在PCI-Express 5.0傳輸之上,并且正在逐漸被CPU制造商廣泛采用。但這不適用于NUMA鏈接,僅適用于各種存儲和計算加速器。

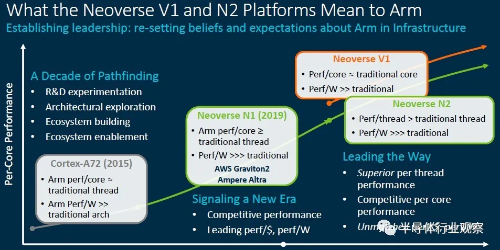

在深入了解具體細(xì)節(jié)之前,Arm整理了一些不錯的圖表,這些圖表顯示了Neoverse平臺中不同核心之間的區(qū)別。這個很有趣:

這是另一個顯示E系列,N系列和V系列在不同熱范圍,內(nèi)核數(shù)和用例中的位置的視圖:

確實(shí),這種區(qū)別并不新鮮。Arm在三年前就針對邊緣和各種數(shù)據(jù)中心計算工作負(fù)載談?wù)摿伺cNeoverse N1設(shè)計有關(guān)的各種設(shè)計SKU。它只是通過三個不同的芯片系列明確完成的,因此Arm許可商為特定市場生產(chǎn)服務(wù)器芯片的某些核心和非核心工作將不再需要做。

深挖V1

V1內(nèi)核將進(jìn)一步突破內(nèi)核數(shù),時鐘速度和每秒操作數(shù)的限制。一切都變成了11個。這并不是因?yàn)锳rm想要炫耀什么,而是因?yàn)橐恍┻\(yùn)行搜索引擎,機(jī)器學(xué)習(xí)培訓(xùn)和推理,HPC仿真和建模以及數(shù)據(jù)分析工作負(fù)載的客戶需要一個怪物來處理他們的數(shù)據(jù)。此外,大型公共云希望擁有一個大型實(shí)例,可以將其分解為小實(shí)例,但重要的是,還可以將大型實(shí)例作為一個昂貴的實(shí)例出售給需要運(yùn)行該實(shí)例的用戶,例如SAP HANA內(nèi)存數(shù)據(jù)庫在云中。

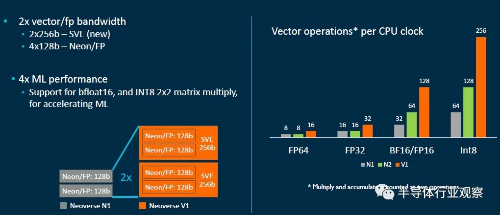

與Ares N1內(nèi)核相比,Zeus V1內(nèi)核在整數(shù)工作負(fù)載上可提供50%的單線程性能提高,這比Arm承諾的每代平均30%的性能還要好。V1設(shè)計具有SVE向量引擎的Armv8-A實(shí)現(xiàn),在這種情況下,它將支持一對256位寬的向量,這些向量可以執(zhí)行Bfloat16以及并行進(jìn)行浮點(diǎn)和整數(shù)運(yùn)算的混合。這將基本上與每個Intel Xeon SP內(nèi)核中的AVX-512矢量單元以及AMD“ Milan” Epyc 7003內(nèi)核中的一對256位FMA單元相匹配。

這是一個整潔的小圖表,解釋了N1,V1和N2內(nèi)核中使用的向量單位的差異:

V1內(nèi)核中的寬矢量與GPU加速器的并行度不高,但是它們運(yùn)行得相當(dāng)快,并且性能差異并不像您想象的那么小。如果您可以獲得GPU的帶寬(大約是GPU的計算密度的一半),并且沒有任何混合編程麻煩,那么也許這是一種更聰明(或者至少更容易)的方式。大家似乎非常清楚,矢量化代碼是性能的未來,而不管它是如何完成的以及使用哪種設(shè)備。

Zeus V1平臺將為需要高帶寬的用戶提供HBM2E堆棧存儲器的DDR5主存儲器支持,并支持PCI-Express 5.0外圍設(shè)備以及CCIX 1.1協(xié)議用于加速器和NUMA互連。這將或多或少地取決于這些技術(shù)的比率,并與英特爾未來的 “Sapphire Rapids”Xeon SP和AMD的“ Genoa” Epyc 7004s相提并論。

這些芯片公司必須在7納米和5納米工藝之間做出非常謹(jǐn)慎的選擇,因此如果我們看到一些使廠商使用CCIX進(jìn)行小芯片互連的小芯片實(shí)現(xiàn),并不會感到驚訝。按照Arm的設(shè)計,允許使用7納米或5納米工藝實(shí)現(xiàn)核心,對于非核心區(qū)域,則可能允許使用14納米或7納米工藝蝕刻,因?yàn)闇p小晶體管尺寸會最大程度地降低其電壓泄漏問題。然而鑒于現(xiàn)在對芯片的巨大需求以及7納米或5納米制造能力的局限,做出這些呼吁將非常困難。

Zeus V1在技術(shù)上符合Armv8.4 ISA和AMBA CHI.D片上互連規(guī)范,這意味著它支持SVE向量。實(shí)際上,這是Arm的第一個本地化SVE實(shí)現(xiàn),它支持將這對256位SVE單元作為128位NEON加速器的四路運(yùn)行,這對于那些將應(yīng)用程序調(diào)整為在Arm GPU加速器上運(yùn)行的用戶來說非常有用。V1核心增強(qiáng)了nested virtualization,內(nèi)存分區(qū)和加密技術(shù),并在可靠性和可伸縮性方面進(jìn)行了許多改進(jìn)。它還從Armv8.5規(guī)范以及Armv8.6規(guī)范的SVE引擎中的Bfloat16和Int8處理中拉開了深遠(yuǎn)的持久性和推測障礙。可以肯定的是,V1內(nèi)核中的內(nèi)容比N1內(nèi)核中的更多。

在設(shè)計中,沒有提到的的是同時多線程或SMT。Arm已從其許多服務(wù)器芯片許可證持有者的觀點(diǎn)出發(fā),認(rèn)為良好的圍墻不會減少嘈雜的鄰居,并且不會對其內(nèi)核進(jìn)行線程化,因此出于性能和安全性原因,可以隔離最小的計算單元(即內(nèi)核)。

此設(shè)計中的許多內(nèi)容都針對百億級HPC,而SiPearl為歐洲第一臺使用V1內(nèi)核的百億級計算機(jī)設(shè)計加速器并非巧合。

“在考慮百億億次級系統(tǒng)時,我們在CMN-700互連和核心中都牢記了一些設(shè)計目標(biāo),” Arm基礎(chǔ)設(shè)施產(chǎn)品管理高級總監(jiān)Brian Jeff告訴The Next Platform。“最重要的是性能,這很重要,因?yàn)樵谶@些系統(tǒng)中,通常您連接到具有真正強(qiáng)大功能的GPU或其他加速器,但根據(jù)Amdahl's law,它們通常可以等待單線程工作負(fù)載。但是性能對于在這些計算機(jī)上運(yùn)行的工作負(fù)載也很重要。”

內(nèi)存和I / O帶寬顯然也很重要,因此保持所有這些平衡也很重要,因此沒有一個組件會等待很多時間。

考慮到所有這些,V1內(nèi)核是Arm進(jìn)入該領(lǐng)域以來性能最高的內(nèi)核,該平臺也將把帶寬限制推到了極限。

這是Zeus V1核心pipeline的外觀:

這是V1核心,并包含CPU元素:

這是深入研究內(nèi)核以及大規(guī)模芯片中V1設(shè)計元素的理論用法:

“這一切都始于一個非常好的前端,”在Arm中央工程部門從事內(nèi)核工作的杰出工程師Chris Abernathy解釋說。

“ V1分支預(yù)測器與N1內(nèi)核中的分支預(yù)測器一樣,已與指令提取分離,這使得分支預(yù)測可以提前運(yùn)行并將指令預(yù)取到L1指令緩存中。這是我們微體系結(jié)構(gòu)的一個非常重要的特征。為了提高基準(zhǔn)測試和實(shí)際工作負(fù)載的性能,我們擴(kuò)大了分支預(yù)測帶寬。”

分支預(yù)測器每個周期有兩個32字節(jié)的flights ,其分支目標(biāo)緩沖區(qū)(BTB)增大了33%,達(dá)到8 KB。Abernathy說,這個想法是要捕獲更多具有更大指令足跡的分支,同時還可以為更緊湊,更小的內(nèi)核降低分支等待時間。其他提高分支準(zhǔn)確性以及將可跟蹤的代碼區(qū)域數(shù)量加倍的調(diào)整,確實(shí)有助于Java工作負(fù)載和其他具有較大且稀疏代碼區(qū)域的應(yīng)用程序。新的V1前端的最終結(jié)果是分支錯誤預(yù)測減少了90%,前端停滯減少了50%。

根據(jù)Abernathy的說法,V1設(shè)計也在推動寬度和深度的極限。內(nèi)核每個周期可以發(fā)送8條指令,是N1內(nèi)核的兩倍,并且指令高速緩存的解碼帶寬每個周期提高4倍至5倍。內(nèi)核中的指令解碼延遲也減少了1個周期。V1內(nèi)核中的亂序執(zhí)行窗口大小也要大一倍,這為內(nèi)核暴露了更多的指令并行性,以使自己能夠處理任務(wù)。整數(shù)分支執(zhí)行單元增加了一倍(到兩個),算術(shù)邏輯單元(ALU)的數(shù)量每個內(nèi)核增加了25%,達(dá)到四個。加載/存儲單元和緩沖區(qū)都得到了提升,許多功能的寬度或帶寬(或兩者)加倍,最終結(jié)果是V1內(nèi)核比N1內(nèi)核的流傳輸帶寬性能提高了45%。

最終結(jié)果是,在相同的頻率下,V1內(nèi)核在N70內(nèi)核上具有比N1內(nèi)核高50%的每個內(nèi)核(IPC)指令,如果客戶希望在時鐘速度上犧牲一點(diǎn)性能,他們可以從根本上減少功率。我們不希望客戶購買基于V1內(nèi)核的服務(wù)器CPU來做到這一點(diǎn)。這是一輛有肌肉的汽車,它將運(yùn)行迅速且充滿激情。

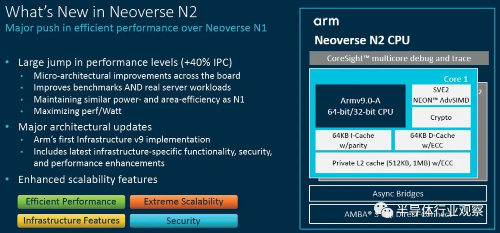

揭開N2的面紗

現(xiàn)在,我們談一下Perseus N2的內(nèi)核和CPU設(shè)計,該設(shè)計針對每美元性能和每瓦性能進(jìn)行了優(yōu)化,而不僅僅是像V1內(nèi)核和CPU那樣不惜一切代價提高性能極限。如果V1是肌肉車,則N2是跨界運(yùn)動型多功能車。

Abernathy說N2內(nèi)核上的前端與V1內(nèi)核上的前端相似,但是該內(nèi)核將基于Armv9-A架構(gòu),該架構(gòu)具有各種有趣的安全功能,坦率地說,這些功能很少用于百億億次計算設(shè)施。

V1設(shè)計針對具有32到128個內(nèi)核且散熱范圍在80瓦到350瓦之間的CPU,而N2內(nèi)核則針對可能具有12到36個內(nèi)核,運(yùn)行功率在30瓦到80瓦之間的主流基礎(chǔ)架構(gòu)服務(wù)器。但這并不是說不會有N2芯片無法突破核心限制,我們認(rèn)為Ampere Computing,AWS以及Nvidia可能會在某些設(shè)備中使用N2內(nèi)核。(Ampere和AWS不太可能在各自的Altra或Graviton芯片中使用V1內(nèi)核。)

N2確實(shí)是對N1的升級,在恒定頻率下IPC提高了40%,功耗與N1大致相同,但其時鐘速度提高了10%,并且內(nèi)核和緩存可能更多,這得益于N1縮小到5納米。

這是N2核心的框圖:

N2設(shè)計具有5個寬的調(diào)度單元,并且較少依賴于深度和寬度攻擊來驅(qū)動V1內(nèi)核具有的最佳性能。正如Abernathy所言,與N1相比,N2設(shè)計中的性能特征必須在功率效率和面積效率上“付出代價”,而這實(shí)際上是對采用新型Armv9-A架構(gòu)的N1的優(yōu)化,以及V1前端嫁接到了它上。可以將分支預(yù)測視為燃料噴射,并且V1的氣缸比N2的多得多,并且還具有更多的燃料噴射器。一種是進(jìn)行拉力賽,其中燃料費(fèi)并不重要,但到達(dá)終點(diǎn)線的時間卻很重要;另一種是在度假時進(jìn)行長途旅行,而不用花費(fèi)比在廉價旅館更多的汽油費(fèi)。

N2內(nèi)核將占用多達(dá)30%的面積,并消耗更多的功率以提供40%的吞吐量,重要的是,N2內(nèi)核將比V1內(nèi)核小25%,因此您可以將更多的N2內(nèi)核塞入給定的芯片中尺寸。那些繁瑣的向量和繁瑣的緩存不是免費(fèi)的。CPU架構(gòu)中沒有任何東西。而且,除了Armv9-A架構(gòu)中的所有安全功能之外,這就是為什么我們希望云構(gòu)建人員希望N2設(shè)計勝于V1設(shè)計。如果他們(或者他們的芯片合作伙伴,如果他們不像AWS那樣設(shè)計自己的芯片,或者微軟正在這樣做),我們不會感到驚訝,可以使用小芯片設(shè)計,再一次使用CCIX作為小芯片互連,并且可能將其核心限制提高到128個以上的內(nèi)核像AMD的Epyc X86服務(wù)器CPU一樣,突破了I / O和內(nèi)存中心的局面。

這就是我們要做的,也許是在單插槽設(shè)計中,這實(shí)際上可以降低系統(tǒng)成本,并增加云實(shí)例的大小以及您可以分割的切片數(shù)量。

這是Abernathy展示的N2參考設(shè)計:

這是針對32核單芯片的,具有四到八個DDR5內(nèi)存通道(運(yùn)行頻率為5.6 GHz,是的)和十二個用于NUMA擴(kuò)展或用作CXL端口的端口。該參考資料沒有施加任何限制,但是其模擬器將幫助公司為N2和硬件工程師編寫軟件,以考慮他們可能會做出的更改,以創(chuàng)建自己的N2設(shè)計。