總線的基本任務是實現(xiàn)數(shù)據(jù)傳送,將一組數(shù)據(jù)從一個設備傳送到另一個設備,當然總線也可以將一個設備的數(shù)據(jù)廣播到多個設備。在處理器系統(tǒng)中,這些數(shù)據(jù)傳送都要依賴一定的規(guī)則,PCI總線并不例外。

PCI總線使用單端并行數(shù)據(jù)線,采用地址譯碼方式進行數(shù)據(jù)傳遞,而采用ID譯碼方式進行配置信息的傳遞。其中地址譯碼方式使用地址信號,而ID譯碼方式使用PCI設備的ID號,包括Bus Number、Device Number、Function Number和Register Number。下文將以圖1?1中的處理器系統(tǒng)為例,簡要介紹PCI總線支持的總線事務及其傳送方式。

如表1?2所示,PCI總線支持多種總線事務。而本節(jié)重點介紹存儲器讀寫總線事務,I/O讀寫總線事務,并在第2.4節(jié)詳細介紹配置讀寫總線事務。值得注意的是,PCI設備只有在系統(tǒng)軟件初始化配置空間之后,才能夠被其他主設備訪問。

當PCI設備的配置空間被初始化之后,該設備在當前的PCI總線樹上將擁有一個獨立的PCI總線地址空間,即BAR((Base Address Register)寄存器所描述的空間,有關BAR寄存器的詳細說明見第2.3.2節(jié)。

處理器與PCI設備進行數(shù)據(jù)交換,或者PCI設備之間進行存儲器數(shù)據(jù)交換時,都將通過PCI總線地址完成。而PCI設備與主存儲器進行DMA操作時,使用的也是PCI總線域的地址,而不是存儲器域的地址,此時HOST主橋將完成PCI總線地址到存儲器域地址的轉換,不同的HOST主橋進行地址轉換時使用的方法并不相同。

PCI總線的配置讀寫總線事務與HOST主橋與PCI橋相關,因此讀者需要了解HOST主橋和PCI橋的詳細實現(xiàn)機制之后,才能深入理解這部分內(nèi)容。本篇將在第2.4節(jié)詳細介紹這些內(nèi)容。在下文中,我們假定所使用的PCI設備的配置空間已經(jīng)被系統(tǒng)軟件初始化。

PCI總線支持以下幾類存儲器讀寫總線事務。

(1) HOST處理器對PCI設備的BAR空間進行數(shù)據(jù)讀寫,BAR空間可以使用存儲器或者I/O譯碼方式。HOST處理器使用PCI總線的存儲器讀寫總線事務和I/O讀寫總線事務訪問PCI設備的BAR空間。

(2) PCI設備之間的數(shù)據(jù)傳遞。在PCI總線上的兩個設備可以直接通信,如一個PCI設備可以訪問另外一個設備的BAR空間。不過這種數(shù)據(jù)傳遞在PC處理器系統(tǒng)中,較少使用。

(3) PCI設備對主存儲器進行讀寫,即DMA讀寫操作。DMA讀寫操作在所有處理器系統(tǒng)中都較為常用,也是PCI總線數(shù)據(jù)傳送的重點所在。在多數(shù)情況下,DMA讀寫操作結束后將伴隨著中斷的產(chǎn)生。PCI設備可以使用INTA#、INTB#、INTC#和INTD#信號提交中斷請求,也可以使用MSI機制提交中斷請求。

1.3.1 PCI總線事務的時序

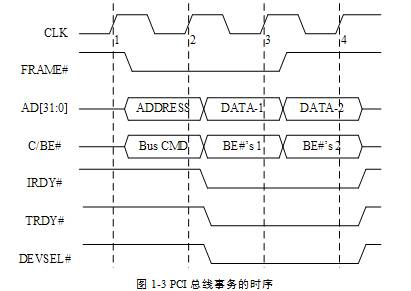

PCI總線使用第1.2節(jié)所述的信號進行數(shù)據(jù)和配置信息的傳遞,一個PCI總線事務的基本訪問時序如圖1-3所示,與PCI總線事務相關的控制信號有FRAME#、IRDY#、TRDY#、DEVSEL#等其他信號。

當一個PCI主設備需要使用PCI總線時,需要首先發(fā)送REQ#信號,通過總線仲裁獲得總線使用權,即GNT#信號有效后,使用以下步驟完成一個完整PCI總線事務,對目標設備進行存儲器或者I/O地址空間的讀寫訪問。

(1) 當PCI主設備獲得總線使用權之后,將在CLK1的上升沿置FRAME#信號有效,啟動PCI總線事務。當PCI總線事務結束后,F(xiàn)RAME#信號將被置為無效。

(2) PCI總線周期的第一個時鐘周期(CLK1的上升沿到CLK2的上升沿之間)為地址周期。在地址周期中,PCI主設備將訪問的目的地址和總線命令分別驅動到AD[31:0]和C/BE#信號上。如果當前總線命令是配置讀寫,那么IDSEL信號線也被置為有效,IDSEL信號與PCI總線的AD[31:11]相連,詳見第2.4.4節(jié)。

(3) 當IRDY#、TRDY#和DEVSEL#信號都有效后,總線事務將使用數(shù)據(jù)周期,進行數(shù)據(jù)傳遞。當IRDY#和TRDY#信號沒有同時有效時,PCI總線不能進行數(shù)據(jù)傳遞,PCI總線使用這兩個信號進行傳送控制。

(4) PCI總線支持突發(fā)周期,因此在地址周期之后可以有多個數(shù)據(jù)周期,可以傳送多組數(shù)據(jù)。而目標設備并不知道突發(fā)周期的長度,如果目標設備不能繼續(xù)接收數(shù)據(jù)時,可以disconnect當前總線事務。值得注意的是,只有存儲器讀寫總線事務可以使用突發(fā)周期。

一個完整的PCI總線事務遠比上述過程復雜的多,因為PCI總線還支持許多傳送方式,如雙地址周期、fast back-to-back(快速背靠背)、插入等待狀態(tài)、重試和斷連、總線上的錯誤處理等一系列總線事務。本篇不一一介紹這些傳送方式。

1.3.2 Posted和Non-Posted傳送方式

PCI總線規(guī)定了兩類數(shù)據(jù)傳送方式,分別是Posted和Non-Posted數(shù)據(jù)傳送方式。其中使用Posted數(shù)據(jù)傳送方式的總線事務也被稱為Posted總線事務;而使用Non-Posted數(shù)據(jù)傳送方式的總線事務也被稱為Non-Posted總線事務。

其中Posted總線事務指PCI主設備向PCI目標設備進行數(shù)據(jù)傳遞時,當數(shù)據(jù)到達PCI橋后,即由PCI橋接管來自上游總線的總線事務,并將其轉發(fā)到下游總線。采用這種數(shù)據(jù)傳送方式,在數(shù)據(jù)還沒有到達最終的目的地之前,PCI總線就可以結束當前總線事務,從而在一定程度上解決了PCI總線的擁塞。

而Non-Posted總線事務是指PCI主設備向PCI目標設備進行數(shù)據(jù)傳遞時,數(shù)據(jù)必須到達最終目的地之后,才能結束當前總線事務的一種數(shù)據(jù)傳遞方式。

顯然采用Posted傳送方式,當這個Posted總線事務通過某條PCI總線后,就可以釋放PCI總線的資源;而采用Non-Posted傳送方式,PCI總線在沒有結束當前總線事務時必須等待。這種等待將嚴重阻塞當前PCI總線上的其他數(shù)據(jù)傳送,因此PCI總線使用Delayed總線事務處理Non-Posted數(shù)據(jù)請求,使用Delayed總線事務可以相對緩解PCI總線的擁塞。Delayed總線事務的詳細介紹見第1.3.5節(jié)。

PCI總線規(guī)定只有存儲器寫請求(包括存儲器寫并無效請求)可以采用Posted總線事務,下文將Posted存儲器寫請求簡稱為PMW(Posted Memory Write),而存儲器讀請求、I/O讀寫請求、配置讀寫請求只能采用Non-Posted總線事務。

下文以圖1?1的處理器系統(tǒng)中的PCI設備11向存儲器進行DMA寫操作為例,說明Posted傳送方式的實現(xiàn)過程。PCI設備11進行DMA寫操作時使用存儲器寫總線事務,當PCI設備11獲得PCI總線x1的使用權后,將發(fā)送存儲器寫總線事務到PCI總線x1。當PCI橋1發(fā)現(xiàn)這個總線事務的地址不在該橋管理的地址范圍內(nèi)將首先接收這個總線事務,并結束PCI總線x1的總線事務。

此時PCI總線x1使用的資源已被釋放,PCI設備11和PCI設備12可以使用PCI總線x1進行通信。PCI橋1獲得PCI總線x0的使用權后,將轉發(fā)這個存儲器寫總線事務到PCI總線x0,之后HOST主橋x將接收這個存儲器寫總線事務,并最終將數(shù)據(jù)寫入主存儲器。

由以上過程可以發(fā)現(xiàn),Posted數(shù)據(jù)請求在通過PCI總線之后,將逐級釋放總線資源,因此PCI總線的利用率較高。而使用Non-Posted方式進行數(shù)據(jù)傳送的處理過程與此不同,Non-Posted數(shù)據(jù)請求在通過PCI總線時,并不會及時釋放總線資源,從而在某種程度上影響PCI總線的使用效率和傳送帶寬。

1.3.3 HOST處理器訪問PCI設備

HOST處理器對PCI設備的數(shù)據(jù)訪問主要包含兩方面內(nèi)容,一方面是處理器向PCI設備發(fā)起存儲器和I/O讀寫請求;另一方面是處理器對PCI設備進行配置讀寫。

在PCI設備的配置空間中,共有6個BAR寄存器。每一個BAR寄存器都與PCI設備使用的一組PCI總線地址空間對應,BAR寄存器記錄這組地址空間的基地址。本書將與BAR寄存器對應的PCI總線地址空間稱為BAR空間,在BAR空間中可以存放I/O地址空間,也可以存放存儲器地址空間。

PCI設備可以根據(jù)需要,有選擇地使用這些BAR空間。值得注意的是,在BAR寄存器中存放的是PCI設備使用的“PCI總線域”的物理地址,而不是“存儲器域”的物理地址,有關BAR寄存器的詳細介紹見第2.3.2節(jié)。

HOST處理器訪問PCI設備I/O地址空間的過程,與訪問存儲器地址空間略有不同。有些處理器,如x86處理器,具有獨立的I/O地址空間。x86處理器可以將PCI設備使用的I/O地址映射到存儲器域的I/O地址空間中,之后處理器可以使用IN,OUT等指令對存儲器域的I/O地址進行訪問,然后通過HOST主橋將存儲器域的I/O地址轉換為PCI總線域的I/O地址,最后使用PCI總線的I/O總線事務對PCI設備的I/O地址進行讀寫訪問。在x86處理器中,存儲器域的I/O地址與PCI總線域的I/O地址相同。

對于有些沒有獨立I/O地址空間的處理器,如PowerPC處理器,需要在HOST主橋初始化時,將PCI設備使用的I/O地址空間映射為處理器的存儲器地址空間。PowerPC處理器對這段“存儲器域”的存儲器空間進行讀寫訪問時,HOST主橋將存儲器域的這段存儲器地址轉換為PCI總線域的I/O地址,然后通過PCI總線的I/O總線事務對PCI設備的I/O地址進行讀寫操作。

在PCI總線中,存儲器讀寫事務與I/O讀寫事務的實現(xiàn)較為類似。首先HOST處理器在初始化時,需要將PCI設備使用的BAR空間映射到“存儲器域”的存儲器地址空間。之后處理器通過存儲器讀寫指令訪問“存儲器域”的存儲器地址空間,HOST主橋將“存儲器域”的讀寫請求翻譯為PCI總線的存儲器讀寫總線事務之后,再發(fā)送給目標設備。

值得注意的是,存儲器域和PCI總線域的概念,PCI設備能夠直接使用的地址為PCI總線域的地址,在PCI總線事務中出現(xiàn)的地址也為PCI總線域的地址;而處理器能夠直接使用的地址為存儲器域的地址。理解存儲器域與PCI總線域的區(qū)別對于理解PCI總線至關重要,本篇將在第2.1節(jié)專門討論這兩個概念。

以上對PCI總線的存儲器與I/O總線事務的介紹并沒有考慮PCI橋的存在,如果將PCI橋考慮進來,情況將略微復雜一些。下文將以圖1?1為例說明處理器如何通過HOST主橋和PCI橋1對PCI設備11進行存儲器讀寫操作。當處理器對PCI設備11進行存儲器寫操作時,這些數(shù)據(jù)需要通過HOST主橋x和PCI橋x1,最終到達PCI設備11,其訪問步驟如下。值得注意的是,以下步驟忽略PCI總線的仲裁過程。

(1) 首先處理器將要傳遞的數(shù)據(jù)放入通用寄存器中,之后向PCI設備11映射到的存儲器域的地址進行寫操作。值得注意的是,處理器并不能直接訪問PCI設備11的PCI總線地址空間,因為這些地址空間是屬于PCI總線域的,處理器所能直接訪問的空間是存儲器域的地址空間。處理器必須通過HOST主橋將存儲器域的數(shù)據(jù)訪問轉換為PCI總線事務才能對PCI總線地址空間進行訪問。

(2) HOST主橋x接收來自處理器的存儲器寫請求,之后處理器結束當前存儲器寫操作,釋放系統(tǒng)總線。HOST主橋x將存儲器域的存儲器地址轉換為PCI總線域的PCI總線地址。并向PCI總線x0發(fā)起PCI寫請求總線事務。值得注意的是,雖然在許多處理器系統(tǒng)中,存儲器地址和PCI總線地址完全相等,但其含義完全不同。

(3) PCI總線x0上的PCI設備01、PCI設備02和PCI橋1將同時監(jiān)聽這個PCI寫總線事務。最后PCI橋x1接收這個寫總線事務,并結束來自PCI總線x0的PCI總線事務。之后PCI橋x1向PCI總線x1發(fā)起新的PCI總線寫總線事務。

(4) PCI總線x1上的PCI設備11和PCI設備12同時監(jiān)聽這個PCI寫總線事務。最后PCI設備11通過地址譯碼方式接收這個寫總線事務,并結束來自PCI總線x1上的PCI總線事務。

由以上過程可以發(fā)現(xiàn),由于存儲器寫總線事務使用Posted傳送方式,因此數(shù)據(jù)通過PCI橋后都將結束上一級總線的PCI總線事務,從而上一級PCI總線可以被其他PCI設備使用。如果使用Non-Posted傳送方式,直到數(shù)據(jù)發(fā)送到PCI設備11之后,PCI總線x1和x0才能依次釋放,從而在某種程度上將造成PCI總線的擁塞。

處理器對PCI設備11進行I/O寫操作時只能采用Non-Posted方式進行,與Posted方式相比,使用Non-Posted方式,當數(shù)據(jù)到達目標設備后,目標設備需要向主設備發(fā)出“回應[1] ”,當主設備收到這個“回應”后才能結束整個總線事務。本節(jié)不再講述處理器如何對PCI設備進行I/O寫操作,請讀者思考這個過程。

處理器對PCI設備11進行存儲器讀時,這個讀請求需要首先通過HOST主橋x和PCI橋x1到達PCI設備,之后PCI設備將讀取的數(shù)據(jù)再次通過PCI橋x1和HOST主橋x傳遞給HOST處理器,其步驟如下所示。我們首先假設PCI總線沒有使用Delayed傳送方式處理Non-Posted總線事務,而是使用純粹的Non-Posted方式。

(1) 首先處理器準備接收數(shù)據(jù)使用的通用寄存器,之后向PCI設備11映射到的存儲器域的地址進行讀操作,

(2) HOST主橋x接收來自處理器的存儲器讀請求。HOST主橋x進行存儲器地址到PCI總線地址的轉換,之后向PCI總線x0發(fā)起存儲器讀總線事務。

(3) PCI總線x0上的PCI設備01、PCI設備02和PCI橋x1將監(jiān)聽這個存儲器讀請求,之后PCI橋1接收這個存儲器讀請求。然后PCI橋x1向PCI總線x1發(fā)起新的PCI總線讀請求。

(4) PCI總線x1上的PCI設備11和PCI設備12監(jiān)聽這個PCI讀請求總線事務。最后PCI設備11接收這個存儲器讀請求總線事務,并將這個讀請求總線事務轉換為存儲器讀完成總線事務之后,將數(shù)據(jù)傳送到PCI橋x1,并結束來自PCI總線x1上的PCI總線事務。

(5) PCI橋x1將接收到的數(shù)據(jù)通過PCI總線x0,繼續(xù)上傳到HOST主橋x,并結束PCI總線x0上的PCI總線事務。

(6) HOST主橋x將數(shù)據(jù)傳遞給處理器,最終結束處理器的存儲器讀操作。

顯然這種方式與Posted傳送方式相比,PCI總線的利用率較低。因為只要HOST處理器沒有收到來自目標設備的“回應”,那么HOST處理器到目標設備的傳送路徑上使用的所有PCI總線都將被阻塞。因而PCI總線x0和x1并沒有被充分利用。

由以上例子,我們可以發(fā)現(xiàn)只有“讀完成”依次通過PCI總線x1和x0之后,存儲器讀總線事務才不繼續(xù)占用PCI總線x1和x0的資源,顯然這種數(shù)據(jù)傳送方式并不合理。因此PCI總線使用Delayed傳送方式解決這個總線擁塞問題,有關Delayed傳送方式的實現(xiàn)機制見第1.3.5節(jié)。

1.3.4 PCI設備讀寫主存儲器

PCI設備與存儲器直接進行數(shù)據(jù)交換的過程也被稱為DMA。與其他總線的DMA過程類似,PCI設備進行DMA操作時,需要獲得數(shù)據(jù)傳送的目的地址和傳送大小。支持DMA傳遞的PCI設備可以在其BAR空間中設置兩個寄存器,分別保存這個目標地址和傳送大小。這兩個寄存器也是PCI設備DMA控制器的組成部件。

值得注意的是,PCI設備進行DMA操作時,使用的目的地址是PCI總線域的物理地址,而不是存儲器域的物理地址,因為PCI設備并不能識別存儲器域的物理地址,而僅能識別PCI總線域的物理地址。

HOST主橋負責完成PCI總線地址到存儲器域地址的轉換。HOST主橋需要進行合理設置,將存儲器的地址空間映射到PCI總線之后,PCI設備才能對這段存儲器空間進行DMA操作。PCI設備不能直接訪問沒有經(jīng)過主橋映射的存儲器空間。

許多處理器允許PCI設備訪問所有存儲器域地址空間,但是有些處理器可以設置PCI設備所能訪問的存儲器域地址空間,從而對存儲器域地址空間進行保護。例如PowerPC處理器的HOST主橋可以使用Inbound寄存器組,設置PCI設備訪問的存儲器地址范圍和屬性,只有在Inbound寄存器組映射的存儲器空間才能被PCI設備訪問,本篇將在第2.2節(jié)詳細介紹PowerPC處理器的這組寄存器。

由上所述,在一個處理器系統(tǒng)中,并不是所有存儲器空間都可以被PCI設備訪問,只有在PCI總線域中有映像的存儲器空間才能被PCI設備訪問。經(jīng)過HOST主橋映射的存儲器,具有兩個“地址”,一個是在存儲器域的地址,一個是在PCI總線域的PCI總線地址。當處理器訪問這段存儲器空間時,使用存儲器地址;而PCI設備訪問這段內(nèi)存時,使用PCI總線地址。在多數(shù)處理器系統(tǒng)中,存儲器地址與PCI總線地址相同,但是系統(tǒng)程序員需要正確理解這兩個地址的區(qū)別。

下文以PCI設備11向主存儲器寫數(shù)據(jù)為例,說明PCI設備如何進行DMA寫操作。

(1) 首先PCI設備11將存儲器寫請求發(fā)向PCI總線x1,注意這個寫請求使用的地址是PCI總線域的地址。

(2) PCI總線x1上的所有設備監(jiān)聽這個請求,因為PCI設備11是向處理器的存儲器寫數(shù)據(jù),所以PCI總線x1上的PCI Agent設備都不會接收這個數(shù)據(jù)請求。

(3) PCI橋x1發(fā)現(xiàn)當前總線事務使用的PCI總線地址不是其下游設備使用的PCI總線地址,則接收這個數(shù)據(jù)請求,有關PCI橋的Secondary總線接收數(shù)據(jù)的過程見第3.2.1節(jié)。此時PCI橋x1將結束來自PCI設備11的Posted存儲器寫請求,并將這個數(shù)據(jù)請求推到上游PCI總線上,即PCI總線x0上。

(4) PCI總線x0上的所有PCI設備包括HOST主橋將監(jiān)聽這個請求。PCI總線x0上的PCI Agent設備也不會接收這個數(shù)據(jù)請求,此時這個數(shù)據(jù)請求將由HOST主橋x接收,并結束PCI橋x1的Posted存儲器寫請求。

(5) HOST主橋x發(fā)現(xiàn)這個數(shù)據(jù)請求發(fā)向存儲器,則將來自PCI總線x0的PCI總線地址轉換為存儲器地址,之后通過存儲器控制器將數(shù)據(jù)寫入存儲器,完成PCI設備的DMA寫操作。

PCI設備進行DMA讀過程與DMA寫過程較為類似。不過PCI總線的存儲器讀總線事務只能使用Non-Posted總線事務,其過程如下。

(1) 首先PCI設備11將存儲器讀請求發(fā)向PCI總線x1。

(2) PCI總線x1上的所有設備監(jiān)聽這個請求,因為PCI設備11是從存儲器中讀取數(shù)據(jù),所以PCI總線x1上的設備,如PCI設備12,不會接收這個數(shù)據(jù)請求。PCI橋x1發(fā)現(xiàn)下游PCI總線沒有設備接收這個數(shù)據(jù)請求,則接收這個數(shù)據(jù)請求,并將這個數(shù)據(jù)請求推到上游PCI總線上,即PCI總線x0上。

(3) PCI總線x0上的設備將監(jiān)聽這個請求。PCI總線x0上的設備也不會接收這個數(shù)據(jù)請求,最后這個數(shù)據(jù)請求將由HOST主橋x接收。

(4) HOST主橋x發(fā)現(xiàn)這個數(shù)據(jù)請求是發(fā)向主存儲器,則將來自PCI總線x0的PCI總線地址轉換為存儲器地址,之后通過存儲器控制器將數(shù)據(jù)讀出,并轉發(fā)到HOST主橋x。

(5) HOST主橋x將數(shù)據(jù)經(jīng)由PCI橋x1傳遞到PCI設備11,PCI設備11接收到這個數(shù)據(jù)后結束DMA讀。

以上過程僅是PCI設備向存儲器讀寫數(shù)據(jù)的一個簡單流程。如果考慮處理器中的Cache,這些存儲器讀寫過程較為復雜。

PCI總線還允許PCI設備之間進行數(shù)據(jù)傳遞,PCI設備間的數(shù)據(jù)交換較為簡單。在實際應用中,PCI設備間的數(shù)據(jù)交換并不常見。下文以圖1?1為例,簡要介紹PCI設備11將數(shù)據(jù)寫入PCI設備01的過程;請讀者自行考慮PCI設備11從PCI設備01讀取數(shù)據(jù)的過程。

(1) 首先PCI設備11將PCI寫總線事務發(fā)向PCI總線x1上。PCI橋x1和PCI設備12同時監(jiān)聽這個寫總線事務。

(2) PCI橋x1將接收這個PCI寫請求總線事務,并將這個PCI寫總線事務上推到PCI總線x0。

(3) PCI總線x0上的所有設備將監(jiān)聽這個PCI寫總線事務,最后由PCI設備01接收這個數(shù)據(jù)請求,并完成PCI寫事務。

1.3.5 Delayed傳送方式

如上文所述,如果處理器使用Non-Posted總線周期對PCI設備進行讀操作,或者PCI設備使用Non-Posted總線事務對存儲器進行讀操作時,如果數(shù)據(jù)沒有到達目的地,那么在這個讀操作路徑上的所有PCI總線都不能被釋放,這將嚴重影響PCI總線的使用效率。

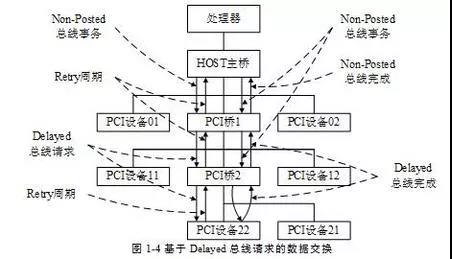

為此PCI橋需要對Non-Posted總線事務進行優(yōu)化處理,并使用Delayed總線事務處理這些Non-Posted總線事務,PCI總線規(guī)定只有Non-Posted總線事務可以使用Delayed總線事務。PCI總線的Delay總線事務由Delay讀寫請求和Delay讀寫完成總線事務組成,當Delay讀寫請求到達目的地后,將被轉換為Delay讀寫完成總線事務。基于Delay總線請求的數(shù)據(jù)交換如圖1-4所示。

假設處理器通過存儲器讀、I/O讀寫或者配置讀寫訪問PCI設備22時,首先經(jīng)過HOST主橋進行存儲器域與PCI總線域的地址轉換,并由HOST主橋發(fā)起PCI總線事務,然后通過PCI橋1、2,最終到達PCI設備22。其詳細步驟如下。

(1) HOST主橋完成存儲器域到PCI總線域的轉換,然后啟動PCI讀總線事務。

(2) PCI橋1接收這個讀總線事務,并首先使用Retry周期,使HOST主橋擇時重新發(fā)起相同的總線周期。此時PCI橋1的上游PCI總線將被釋放。值得注意的是PCI橋并不會每一次都使用Retry周期,使上游設備擇時進行重試操作。在PCI總線中,有一個“16 Clock”原則,即FRAME#信號有效后,必須在16個時鐘周期內(nèi)置為無效,如果PCI橋發(fā)現(xiàn)來自上游設備的讀總線事務不能在16個時鐘周期內(nèi)結束時,則使用Retry周期終止該總線事務。

(3) PCI橋1使用Delayed總線請求繼續(xù)訪問PCI設備22。

(4) PCI橋2接收這個總線請求,并將這個Delayed總線請求繼續(xù)傳遞。此時PCI橋2也將首先使用Retry周期,使PCI橋1擇時重新發(fā)起相同的總線周期。此時PCI橋2的上游PCI總線被釋放。

(5) 這個數(shù)據(jù)請求最終到達PCI設備22,如果PCI設備22沒有將數(shù)據(jù)準備好時,也可以使用Retry周期,使PCI橋2擇時重新發(fā)起相同的總線周期;如果數(shù)據(jù)已經(jīng)準備好,PCI設備22將接收這個數(shù)據(jù)請求,并將這個Delayed總線請求轉換為Delayed總線完成事務。如果Delayed總線請求是讀請求,則Delayed總線完成事務中含有數(shù)據(jù),否則只有完成信息,而不包含數(shù)據(jù)。

(6) Delayed總線完成事務將“數(shù)據(jù)或者完成信息”傳遞給PCI橋2,當PCI橋1重新發(fā)出Non-Posted總線請求時,PCI橋2將這個“數(shù)據(jù)或者完成信息”傳遞給PCI橋1。

(7) HOST主橋重新發(fā)出存儲器讀總線事務時,PCI橋1將“數(shù)據(jù)或者完成信息”傳遞給HOST主橋,最終完成整個PCI總線事務。

由以上分析可知,Delayed總線周期由Delayed總線請求和Delayed總線完成兩部分組成。下文將Delayed讀請求總線事務簡稱為DRR(Delayed Read Request),Delayed讀完成總線事務簡稱為DRC(Delayed Read Completion);而將Delayed寫請求總線事務簡稱為DWR(Delayed Write Request),Delayed寫完成總線事務簡稱為DWC(Delayed Write Completion)。

PCI總線使用Delayed總線事務,在一定程度上可以提高PCI總線的利用率。因為在進行Non-Posted總線事務時,Non-Posted請求在通過PCI橋之后,可以暫時釋放PCI總線,但是采用這種方式,HOST/PCI橋將會擇時進行重試操作。在許多情況下,使用Delayed總線事務,并不能取得理想的效果,因為過多的重試周期也將大量消耗PCI總線的帶寬。

為了進一步提高Non-Posted總線事務的執(zhí)行效率,PCI-X總線將PCI總線使用的Delayed總線事務,升級為Split總線事務。采用Split總線事務可以有效解決HOST/PCI橋的這些重試操作。Split總線事務的基本思想是發(fā)送端首先將Non-Posted總線請求發(fā)送給接收端,然后再由接收端主動地將數(shù)據(jù)傳遞給發(fā)送端。

除了PCI-X總線可以使用Split總線事務進行數(shù)據(jù)傳送之外,有些處理器,如x86和PowerPC處理器的FSB(Front Side Bus)總線也支持這種Split總線事務,因此這些HOST主橋也可以發(fā)起這種Split總線事務。在PCIe總線中,Non-Posted數(shù)據(jù)傳送都使用Split總線事務完成,而不再使用Delayed總線事務。