當(dāng)聽到“半導(dǎo)體”這個詞時,你會想到什么?它聽起來復(fù)雜且遙遠,但其實已經(jīng)滲透到我們生活的各個方面:從智能手機、筆記本電腦、信用卡到地鐵,我們?nèi)粘I钏蕾嚨母鞣N物品都用到了半導(dǎo)體。

每個半導(dǎo)體產(chǎn)品的制造都需要數(shù)百個工藝,泛林集團將整個制造過程分為八個步驟:晶圓加工-氧化-光刻-刻蝕-薄膜沉積-互連-測試-封裝。

為幫助大家了解和認(rèn)識半導(dǎo)體及相關(guān)工藝,我們將以三期微信推送,為大家逐一介紹上述每個步驟。

第一步 晶圓加工

所有半導(dǎo)體工藝都始于一粒沙子!因為沙子所含的硅是生產(chǎn)晶圓所需要的原材料。晶圓是將硅(Si)或砷化鎵(GaAs)制成的單晶柱體切割形成的圓薄片。要提取高純度的硅材料需要用到硅砂,一種二氧化硅含量高達95%的特殊材料,也是制作晶圓的主要原材料。晶圓加工就是制作獲取上述晶圓的過程。

① 鑄錠

首先需將沙子加熱,分離其中的一氧化碳和硅,并不斷重復(fù)該過程直至獲得超高純度的電子級硅(EG-Si)。高純硅熔化成液體,進而再凝固成單晶固體形式,稱為“錠”,這就是半導(dǎo)體制造的第一步。硅錠(硅柱)的制作精度要求很高,達到納米級,其廣泛應(yīng)用的制造方法是提拉法。

② 錠切割

前一個步驟完成后,需要用金剛石鋸切掉鑄錠的兩端,再將其切割成一定厚度的薄片。錠薄片直徑?jīng)Q定了晶圓的尺寸,更大更薄的晶圓能被分割成更多的可用單元,有助于降低生產(chǎn)成本。切割硅錠后需在薄片上加入“平坦區(qū)”或“凹痕”標(biāo)記,方便在后續(xù)步驟中以其為標(biāo)準(zhǔn)設(shè)置加工方向。

③ 晶圓表面拋光

通過上述切割過程獲得的薄片被稱為“裸片”,即未經(jīng)加工的“原料晶圓”。裸片的表面凹凸不平,無法直接在上面印制電路圖形。因此,需要先通過研磨和化學(xué)刻蝕工藝去除表面瑕疵,然后通過拋光形成光潔的表面,再通過清洗去除殘留污染物,即可獲得表面整潔的成品晶圓。

第二步 氧化

氧化過程的作用是在晶圓表面形成保護膜。它可以保護晶圓不受化學(xué)雜質(zhì)影響、避免漏電流進入電路、預(yù)防離子植入過程中的擴散以及防止晶圓在刻蝕時滑脫。

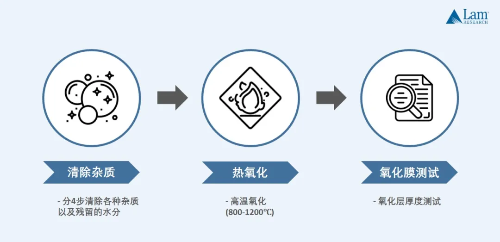

氧化過程的第一步是去除雜質(zhì)和污染物,需要通過四步去除有機物、金屬等雜質(zhì)及蒸發(fā)殘留的水分。清潔完成后就可以將晶圓置于800至1200攝氏度的高溫環(huán)境下,通過氧氣或蒸氣在晶圓表面的流動形成二氧化硅(即“氧化物”)層。氧氣擴散通過氧化層與硅反應(yīng)形成不同厚度的氧化層,可以在氧化完成后測量它的厚度。

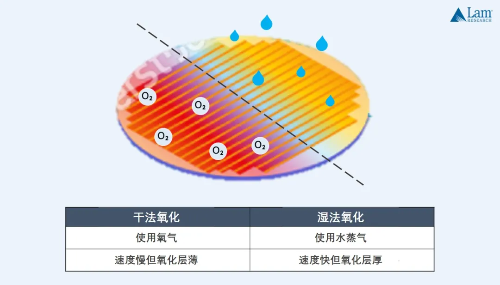

干法氧化和濕法氧化

根據(jù)氧化反應(yīng)中氧化劑的不同,熱氧化過程可分為干法氧化和濕法氧化,前者使用純氧產(chǎn)生二氧化硅層,速度慢但氧化層薄而致密,后者需同時使用氧氣和高溶解度的水蒸氣,其特點是生長速度快但保護層相對較厚且密度較低。

除氧化劑以外,還有其他變量會影響到二氧化硅層的厚度。首先,晶圓結(jié)構(gòu)及其表面缺陷和內(nèi)部摻雜濃度都會影響氧化層的生成速率。此外,氧化設(shè)備產(chǎn)生的壓力和溫度越高,氧化層的生成就越快。在氧化過程,還需要根據(jù)單元中晶圓的位置而使用假片,以保護晶圓并減小氧化度的差異。

第三步 光刻

光刻是通過光線將電路圖案“印刷”到晶圓上,我們可以將其理解為在晶圓表面繪制半導(dǎo)體制造所需的平面圖。電路圖案的精細(xì)度越高,成品芯片的集成度就越高,必須通過先進的光刻技術(shù)才能實現(xiàn)。具體來說,光刻可分為涂覆光刻膠、曝光和顯影三個步驟。

① 涂覆光刻膠

在晶圓上繪制電路的第一步是在氧化層上涂覆光刻膠。光刻膠通過改變化學(xué)性質(zhì)的方式讓晶圓成為“相紙”。晶圓表面的光刻膠層越薄,涂覆越均勻,可以印刷的圖形就越精細(xì)。這個步驟可以采用“旋涂”方法。

根據(jù)光(紫外線)反應(yīng)性的區(qū)別,光刻膠可分為兩種:正膠和負(fù)膠,前者在受光后會分解并消失,從而留下未受光區(qū)域的圖形,而后者在受光后會聚合并讓受光部分的圖形顯現(xiàn)出來。

② 曝光

在晶圓上覆蓋光刻膠薄膜后,就可以通過控制光線照射來完成電路印刷,這個過程被稱為“曝光”。我們可以通過曝光設(shè)備來選擇性地通過光線,當(dāng)光線穿過包含電路圖案的掩膜時,就能將電路印制到下方涂有光刻膠薄膜的晶圓上。

在曝光過程中,印刷圖案越精細(xì),最終的芯片就能夠容納更多元件,這有助于提高生產(chǎn)效率并降低單個元件的成本。在這個領(lǐng)域,目前備受矚目的新技術(shù)是EUV光刻。去年2月,泛林集團與戰(zhàn)略合作伙伴ASML和imec共同研發(fā)出了一種全新的干膜光刻膠技術(shù)。該技術(shù)能通過提高分辨率(微調(diào)電路寬度的關(guān)鍵要素)大幅提升EUV光刻曝光工藝的生產(chǎn)率和良率。

③ 顯影

曝光之后的步驟是在晶圓上噴涂顯影劑,目的是去除圖形未覆蓋區(qū)域的光刻膠,從而讓印刷好的電路圖案顯現(xiàn)出來。顯影完成后需要通過各種測量設(shè)備和光學(xué)顯微鏡進行檢查,確保電路圖繪制的質(zhì)量。

以上是對晶圓加工、氧化和光刻工藝的簡要介紹,下面,我們將為大家介紹半導(dǎo)體制造中兩大重要步驟——刻蝕和薄膜沉積!

第四步 刻蝕

在晶圓上完成電路圖的光刻后,就要用刻蝕工藝來去除任何多余的氧化膜且只留下半導(dǎo)體電路圖。要做到這一點需要利用液體、氣體或等離子體來去除選定的多余部分。

刻蝕的方法主要分為兩種,取決于所使用的物質(zhì):使用特定的化學(xué)溶液進行化學(xué)反應(yīng)來去除氧化膜的濕法刻蝕,以及使用氣體或等離子體的干法刻蝕。

濕法刻蝕

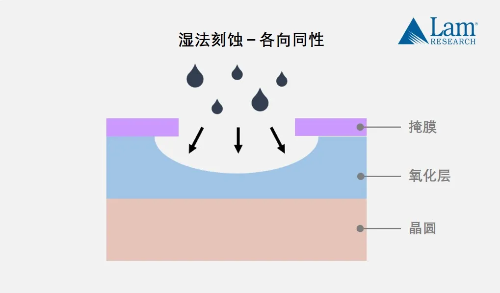

使用化學(xué)溶液去除氧化膜的濕法刻蝕具有成本低、刻蝕速度快和生產(chǎn)率高的優(yōu)勢。然而,濕法刻蝕具有各向同性的特點,即其速度在任何方向上都是相同的。這會導(dǎo)致掩膜(或敏感膜)與刻蝕后的氧化膜不能完全對齊,因此很難處理非常精細(xì)的電路圖。

干法刻蝕

干法刻蝕可分為三種不同類型。第一種為化學(xué)刻蝕,其使用的是刻蝕氣體(主要是氟化氫)。和濕法刻蝕一樣,這種方法也是各向同性的,這意味著它也不適合用于精細(xì)的刻蝕。

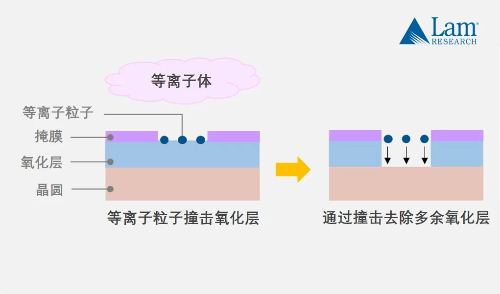

第二種方法是物理濺射,即用等離子體中的離子來撞擊并去除多余的氧化層。作為一種各向異性的刻蝕方法,濺射刻蝕在水平和垂直方向的刻蝕速度是不同的,因此它的精細(xì)度也要超過化學(xué)刻蝕。但這種方法的缺點是刻蝕速度較慢,因為它完全依賴于離子碰撞引起的物理反應(yīng)。

最后的第三種方法就是反應(yīng)離子刻蝕(RIE)。RIE結(jié)合了前兩種方法,即在利用等離子體進行電離物理刻蝕的同時,借助等離子體活化后產(chǎn)生的自由基進行化學(xué)刻蝕。除了刻蝕速度超過前兩種方法以外,RIE可以利用離子各向異性的特性,實現(xiàn)高精細(xì)度圖案的刻蝕。

如今干法刻蝕已經(jīng)被廣泛使用,以提高精細(xì)半導(dǎo)體電路的良率。保持全晶圓刻蝕的均勻性并提高刻蝕速度至關(guān)重要,當(dāng)今最先進的干法刻蝕設(shè)備正在以更高的性能,支持最為先進的邏輯和存儲芯片的生產(chǎn)。

針對不同的刻蝕應(yīng)用,泛林集團提供多個刻蝕產(chǎn)品系列,包括用于深硅刻蝕的DSiE?系列和Syndion?系列、關(guān)鍵介電刻蝕產(chǎn)品Flex?系列、用于導(dǎo)體刻蝕的Kiyo?系列、用于金屬刻蝕的Versys? Metal系列。在行業(yè)領(lǐng)先的Kiyo和Flex工藝模塊的基礎(chǔ)上,泛林集團還于去年3月推出Sense.i?系列,其高性能表現(xiàn)能夠滿足前述生產(chǎn)過程所需的精確性和一致性要求,適合各種關(guān)鍵和半關(guān)鍵性刻蝕應(yīng)用。

第五步 薄膜沉積

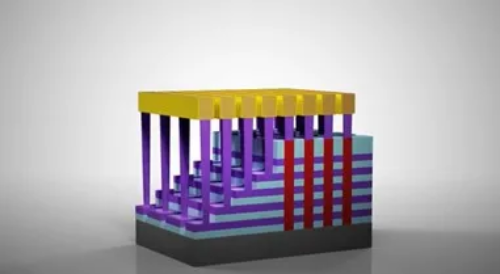

為了創(chuàng)建芯片內(nèi)部的微型器件,我們需要不斷地沉積一層層的薄膜并通過刻蝕去除掉其中多余的部分,另外還要添加一些材料將不同的器件分離開來。每個晶體管或存儲單元就是通過上述過程一步步構(gòu)建起來的。我們這里所說的“薄膜”是指厚度小于1微米(μm,百萬分之一米)、無法通過普通機械加工方法制造出來的“膜”。將包含所需分子或原子單元的薄膜放到晶圓上的過程就是“沉積”。

要形成多層的半導(dǎo)體結(jié)構(gòu),我們需要先制造器件疊層,即在晶圓表面交替堆疊多層薄金屬(導(dǎo)電)膜和介電(絕緣)膜,之后再通過重復(fù)刻蝕工藝去除多余部分并形成三維結(jié)構(gòu)。可用于沉積過程的技術(shù)包括化學(xué)氣相沉積 (CVD)、原子層沉積 (ALD) 和物理氣相沉積 (PVD),采用這些技術(shù)的方法又可以分為干法和濕法沉積兩種。

01.化學(xué)氣相沉積

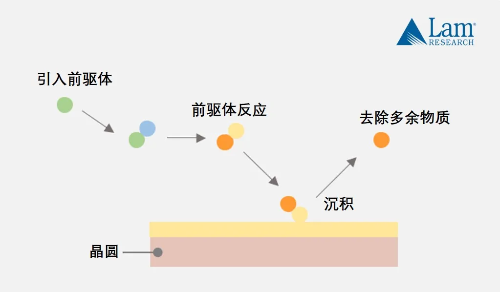

在化學(xué)氣相沉積中,前驅(qū)氣體會在反應(yīng)腔發(fā)生化學(xué)反應(yīng)并生成附著在晶圓表面的薄膜以及被抽出腔室的副產(chǎn)物。

等離子體增強化學(xué)氣相沉積則需要借助等離子體產(chǎn)生反應(yīng)氣體。這種方法降低了反應(yīng)溫度,因此非常適合對溫度敏感的結(jié)構(gòu)。使用等離子體還可以減少沉積次數(shù),往往可以帶來更高質(zhì)量的薄膜。

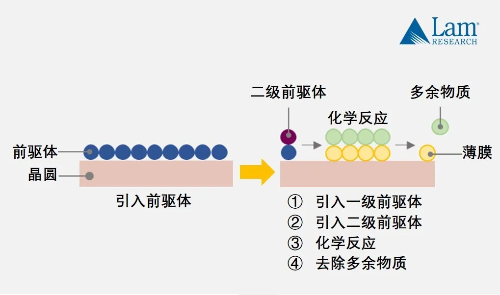

02.原子層沉積

原子層沉積通過每次只沉積幾個原子層從而形成薄膜。該方法的關(guān)鍵在于循環(huán)按一定順序進行的獨立步驟并保持良好的控制。在晶圓表面涂覆前驅(qū)體是第一步,之后引入不同的氣體與前驅(qū)體反應(yīng)即可在晶圓表面形成所需的物質(zhì)。

03.物理氣相沉積

顧名思義,物理氣相沉積是指通過物理手段形成薄膜。濺射就是一種物理氣相沉積方法,其原理是通過氬等離子體的轟擊讓靶材的原子濺射出來并沉積在晶圓表面形成薄膜。

在某些情況下,可以通過紫外線熱處理 (UVTP) 等技術(shù)對沉積膜進行處理并改善其性能。

泛林集團的沉積設(shè)備均具備出色的精度、性能和靈活性,包括適用于鎢金屬化工藝的ALTUS?系列、具有后薄膜沉積處理能力的SOLA?系列、高密度等離子體化學(xué)氣相沉積SPEED?系列、采用先進ALD技術(shù)的Striker?系列以及VECTOR? PECVD系列等。

我們已經(jīng)從前面的了解了半導(dǎo)體制造的前幾大步驟,包括晶圓加工、氧化、光刻、刻蝕和薄膜沉積。我們繼續(xù)介紹最后三個步驟:互連、測試和封裝,以完成半導(dǎo)體芯片的制造。

第六步 · 互連

半導(dǎo)體的導(dǎo)電性處于導(dǎo)體與非導(dǎo)體(即絕緣體)之間,這種特性使我們能完全掌控電流。通過基于晶圓的光刻、刻蝕和沉積工藝可以構(gòu)建出晶體管等元件,但還需要將它們連接起來才能實現(xiàn)電力與信號的發(fā)送與接收。

金屬因其具有導(dǎo)電性而被用于電路互連。用于半導(dǎo)體的金屬需要滿足以下條件:

低電阻率:由于金屬電路需要傳遞電流,因此其中的金屬應(yīng)具有較低的電阻。

熱化學(xué)穩(wěn)定性:金屬互連過程中金屬材料的屬性必須保持不變。

高可靠性:隨著集成電路技術(shù)的發(fā)展,即便是少量金屬互連材料也必須具備足夠的耐用性。

制造成本:即使已經(jīng)滿足前面三個條件,材料成本過高的話也無法滿足批量生產(chǎn)的需要。互連工藝主要使用鋁和銅這兩種物質(zhì)。

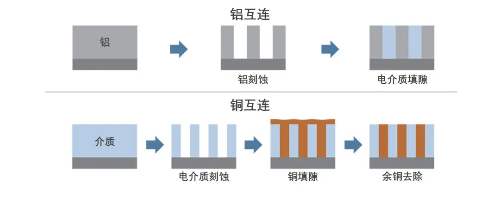

鋁互連工藝

鋁互連工藝始于鋁沉積、光刻膠應(yīng)用以及曝光與顯影,隨后通過刻蝕有選擇地去除任何多余的鋁和光刻膠,然后才能進入氧化過程。前述步驟完成后再不斷重復(fù)光刻、刻蝕和沉積過程直至完成互連。

除了具有出色的導(dǎo)電性,鋁還具有容易光刻、刻蝕和沉積的特點。此外,它的成本較低,與氧化膜粘附的效果也比較好。其缺點是容易腐蝕且熔點較低。另外,為防止鋁與硅反應(yīng)導(dǎo)致連接問題,還需要添加金屬沉積物將鋁與晶圓隔開,這種沉積物被稱為“阻擋金屬”。

鋁電路是通過沉積形成的。晶圓進入真空腔后,鋁顆粒形成的薄膜會附著在晶圓上。這一過程被稱為“氣相沉積 (VD) ”,包括化學(xué)氣相沉積和物理氣相沉積。

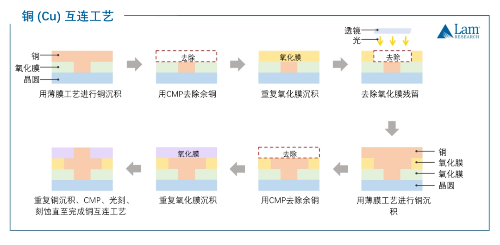

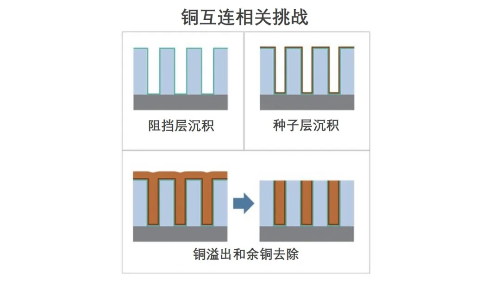

銅互連工藝

隨著半導(dǎo)體工藝精密度的提升以及器件尺寸的縮小,鋁電路的連接速度和電氣特性逐漸無法滿足要求,為此我們需要尋找滿足尺寸和成本兩方面要求的新導(dǎo)體。銅之所以能取代鋁的第一個原因就是其電阻更低,因此能實現(xiàn)更快的器件連接速度。其次銅的可靠性更高,因為它比鋁更能抵抗電遷移,也就是電流流過金屬時發(fā)生的金屬離子運動。

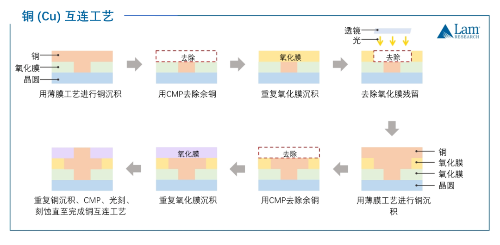

但是,銅不容易形成化合物,因此很難將其氣化并從晶圓表面去除。針對這個問題,我們不再去刻蝕銅,而是沉積和刻蝕介電材料,這樣就可以在需要的地方形成由溝道和通路孔組成的金屬線路圖形,之后再將銅填入前述“圖形”即可實現(xiàn)互連,而最后的填入過程被稱為“鑲嵌工藝”。

隨著銅原子不斷擴散至電介質(zhì),后者的絕緣性會降低并產(chǎn)生阻擋銅原子繼續(xù)擴散的阻擋層。之后阻擋層上會形成很薄的銅種子層。到這一步之后就可以進行電鍍,也就是用銅填充高深寬比的圖形。填充后多余的銅可以用金屬化學(xué)機械拋光 (CMP) 方法去除,完成后即可沉積氧化膜,多余的膜則用光刻和刻蝕工藝去除即可。前述整個過程需要不斷重復(fù)直至完成銅互連為止。

通過上述對比可以看出,銅互連和鋁互連的區(qū)別在于,多余的銅是通過金屬CMP而非刻蝕去除的。

第七步 測試

測試的主要目標(biāo)是檢驗半導(dǎo)體芯片的質(zhì)量是否達到一定標(biāo)準(zhǔn),從而消除不良產(chǎn)品、并提高芯片的可靠性。另外,經(jīng)測試有缺陷的產(chǎn)品不會進入封裝步驟,有助于節(jié)省成本和時間。電子管芯分選 (EDS) 就是一種針對晶圓的測試方法。

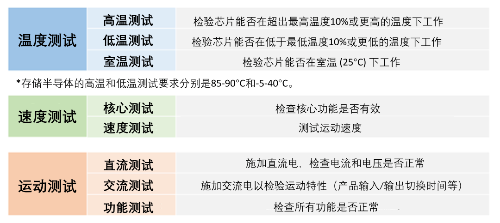

EDS是一種檢驗晶圓狀態(tài)中各芯片的電氣特性并由此提升半導(dǎo)體良率的工藝。EDS可分為五步,具體如下 :

01.電氣參數(shù)監(jiān)控 (EPM)

EPM是半導(dǎo)體芯片測試的第一步。該步驟將對半導(dǎo)體集成電路需要用到的每個器件(包括晶體管、電容器和二極管)進行測試,確保其電氣參數(shù)達標(biāo)。EPM的主要作用是提供測得的電氣特性數(shù)據(jù),這些數(shù)據(jù)將被用于提高半導(dǎo)體制造工藝的效率和產(chǎn)品性能(并非檢測不良產(chǎn)品)。

02.晶圓老化測試

半導(dǎo)體不良率來自兩個方面,即制造缺陷的比率(早期較高)和之后整個生命周期發(fā)生缺陷的比率。晶圓老化測試是指將晶圓置于一定的溫度和AC/DC電壓下進行測試,由此找出其中可能在早期發(fā)生缺陷的產(chǎn)品,也就是說通過發(fā)現(xiàn)潛在缺陷來提升最終產(chǎn)品的可靠性。

03.檢測

老化測試完成后就需要用探針卡將半導(dǎo)體芯片連接到測試裝置,之后就可以對晶圓進行溫度、速度和運動測試以檢驗相關(guān)半導(dǎo)體功能。具體測試步驟的說明請見表格。

04.修補

修補是最重要的測試步驟,因為某些不良芯片是可以修復(fù)的,只需替換掉其中存在問題的元件即可。

05.點墨

未能通過電氣測試的芯片已經(jīng)在之前幾個步驟中被分揀出來,但還需要加上標(biāo)記才能區(qū)分它們。過去我們需要用特殊墨水標(biāo)記有缺陷的芯片,保證它們用肉眼即可識別,如今則是由系統(tǒng)根據(jù)測試數(shù)據(jù)值自動進行分揀。

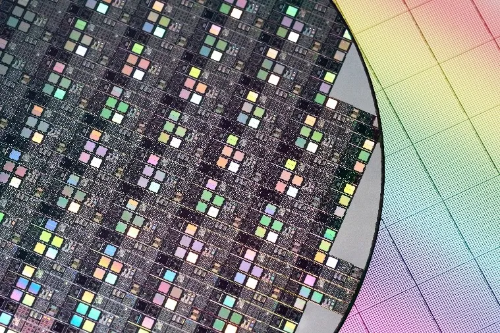

第八步 · 封裝

經(jīng)過之前幾個工藝處理的晶圓上會形成大小相等的方形芯片(又稱“單個晶片”)。下面要做的就是通過切割獲得單獨的芯片。剛切割下來的芯片很脆弱且不能交換電信號,需要單獨進行處理。這一處理過程就是封裝,包括在半導(dǎo)體芯片外部形成保護殼和讓它們能夠與外部交換電信號。整個封裝制程分為五步,即晶圓鋸切、單個晶片附著、互連、成型和封裝測試。

01.晶圓鋸切

要想從晶圓上切出無數(shù)致密排列的芯片,我們首先要仔細(xì)“研磨”晶圓的背面直至其厚度能夠滿足封裝工藝的需要。研磨后,我們就可以沿著晶圓上的劃片線進行切割,直至將半導(dǎo)體芯片分離出來。

晶圓鋸切技術(shù)有三種:刀片切割、激光切割和等離子切割。刀片切割是指用金剛石刀片切割晶圓,這種方法容易產(chǎn)生摩擦熱和碎屑并因此損壞晶圓。激光切割的精度更高,能輕松處理厚度較薄或劃片線間距很小的晶圓。等離子切割采用等離子刻蝕的原理,因此即使劃片線間距非常小,這種技術(shù)同樣能適用。

02.單個晶片附著

所有芯片都從晶圓上分離后,我們需要將單獨的芯片(單個晶片)附著到基底(引線框架)上。基底的作用是保護半導(dǎo)體芯片并讓它們能與外部電路進行電信號交換。附著芯片時可以使用液體或固體帶狀粘合劑。

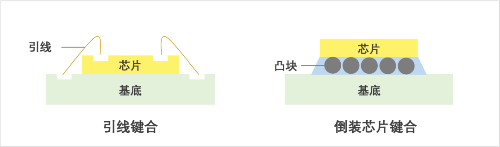

03.互連

在將芯片附著到基底上之后,我們還需要連接二者的接觸點才能實現(xiàn)電信號交換。這一步可以使用的連接方法有兩種:使用細(xì)金屬線的引線鍵合和使用球形金塊或錫塊的倒裝芯片鍵合。引線鍵合屬于傳統(tǒng)方法,倒裝芯片鍵合技術(shù)可以加快半導(dǎo)體制造的速度。

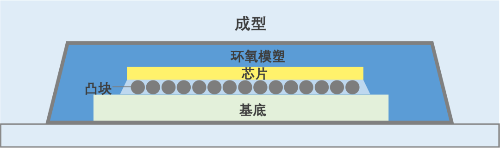

04.成型

完成半導(dǎo)體芯片的連接后,需要利用成型工藝給芯片外部加一個包裝,以保護半導(dǎo)體集成電路不受溫度和濕度等外部條件影響。根據(jù)需要制成封裝模具后,我們要將半導(dǎo)體芯片和環(huán)氧模塑料 (EMC) 都放入模具中并進行密封。密封之后的芯片就是最終形態(tài)了。

05.封裝測試

已經(jīng)具有最終形態(tài)的芯片還要通過最后的缺陷測試。進入最終測試的全部是成品的半導(dǎo)體芯片。它們將被放入測試設(shè)備,設(shè)定不同的條件例如電壓、溫度和濕度等進行電氣、功能和速度測試。這些測試的結(jié)果可以用來發(fā)現(xiàn)缺陷、提高產(chǎn)品質(zhì)量和生產(chǎn)效率。

封裝技術(shù)的演變

隨著芯片體積的減少和性能要求的提升,封裝在過去數(shù)年間已經(jīng)歷了多次技術(shù)革新。面向未來的一些封裝技術(shù)和方案包括將沉積用于傳統(tǒng)后道工藝,例如晶圓級封裝(WLP)、凸塊工藝和重布線層 (RDL) 技術(shù),以及用于前道晶圓制造的的刻蝕和清潔技術(shù)。

下面我們介紹一些基于泛林集團開發(fā)的先進封裝解決方案。

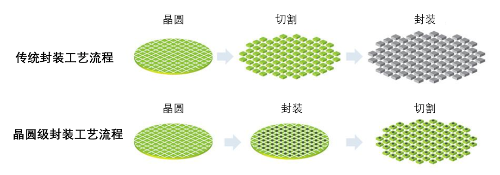

什么是先進封裝?

傳統(tǒng)封裝需要將每個芯片都從晶圓中切割出來并放入模具中。晶圓級封裝(WLP)則是先進封裝技術(shù)的一種, 是指直接封裝仍在晶圓上的芯片。WLP的流程是先封裝測試,然后一次性將所有已成型的芯片從晶圓上分離出來。與傳統(tǒng)封裝相比,WLP的優(yōu)勢在于更低的生產(chǎn)成本。

先進封裝可劃分為2D封裝、2.5D封裝和3D封裝。

更小的2D封裝

如前所述,封裝工藝的主要用途包括將半導(dǎo)體芯片的信號發(fā)送到外部,而在晶圓上形成的凸塊就是發(fā)送輸入/輸出信號的接觸點。這些凸塊分為扇入型(fan-in) 和扇出型 (fan-out) 兩種,前者的扇形在芯片內(nèi)部,后者的扇形則要超出芯片范圍。我們將輸入/輸出信號稱為I/O(輸入/輸出),輸入/輸出數(shù)量稱為I/O計數(shù)。I/O計數(shù)是確定封裝方法的重要依據(jù)。如果I/O計數(shù)低就采用扇入封裝工藝。由于封裝后芯片尺寸變化不大,因此這種過程又被稱為芯片級封裝 (CSP) 或晶圓級芯片尺寸封裝 (WLCSP)。如果I/O計數(shù)較高,則通常要采用扇出型封裝工藝,且除凸塊外還需要重布線層 (RDL) 才能實現(xiàn)信號發(fā)送。這就是“扇出型晶圓級封裝 (FOWLP)”。

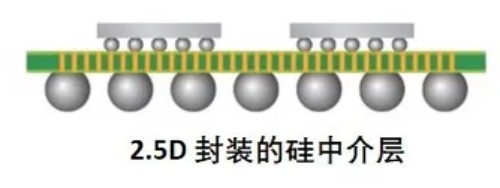

2.5D 封裝

2.5D封裝技術(shù)可以將兩種或更多類型的芯片放入單個封裝,同時讓信號橫向傳送,這樣可以提升封裝的尺寸和性能。最廣泛使用的2.5D封裝方法是通過硅中介層將內(nèi)存和邏輯芯片放入單個封裝。2.5D封裝需要硅通孔 (TSV)、微型凸塊和小間距RDL等核心技術(shù)。

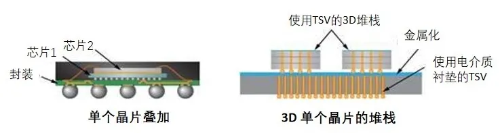

3D 封裝

3D封裝技術(shù)可以將兩種或更多類型的芯片放入單個封裝,同時讓信號縱向傳送。這種技術(shù)適用于更小和I/O計數(shù)更高的半導(dǎo)體芯片。TSV可用于I/O計數(shù)高的芯片,引線鍵合可用于I/O計數(shù)低的芯片,并最終形成芯片垂直排列的信號系統(tǒng)。3D封裝需要的核心技術(shù)包括TSV和微型凸塊技術(shù)。

泛林集團能夠提供上述工藝所需的核心方案,包括硅刻蝕、金屬擴散阻擋層、鍍銅和清洗技術(shù),以及構(gòu)建微型凸塊和微型RDL所需的電鍍、清洗和濕刻蝕方案。

至此,半導(dǎo)體產(chǎn)品制造的八個步驟“晶圓加工-氧化-光刻-刻蝕-薄膜沉積-互連-測試-封裝”已全部介紹完畢,從“沙粒”蛻變到“芯片”,半導(dǎo)體科技正在上演現(xiàn)實版“點石成金”。