滾燙的手機(jī),溫度過高而死機(jī)的電腦,這些問題時(shí)常困擾著廣大的使用者們,這背后的原因多半要?dú)w咎于芯片過熱。實(shí)際上芯片的發(fā)熱問題不僅造成了使用上的不便,也給生產(chǎn)者們帶來了巨大的技術(shù)成本,并限制了芯片性能的進(jìn)一步的提升。

一顆小小的芯片為何會(huì)產(chǎn)生那么大的熱量?芯片的性能與發(fā)熱量有什么關(guān)系?工程師和科學(xué)家們又是用什么方法來解決這一問題?本文就將為你揭曉以上問題的答案。

一,功耗是芯片的夢(mèng)魘

1965年,英特爾創(chuàng)始人之一的戈登·摩爾提出了經(jīng)典的摩爾定律, “每18個(gè)月性能提升一倍,價(jià)格降低一半”,這條金科玉律就像一座路標(biāo),指引著行業(yè)發(fā)展的方向與節(jié)奏。隨之而來的就是更小的晶體管,頻率更高的CPU,集成度更高的數(shù)字電路和更低的成本。一代又一代的芯片和電子產(chǎn)品由專用走向普及,并逐漸滲透到了生活和工作的方方面面。

也正是如此,人們打開了數(shù)字世界的大門,看到了前所未見的光景。但與此同時(shí),芯片性能的躍升也逐漸遇到了瓶頸……

以柵極氧化層為例,在采用CMOS數(shù)字電路構(gòu)造的CPU里,它起到關(guān)鍵的絕緣作用。柵極氧化層不僅要保證表面平整,不能有缺陷,為了符合半導(dǎo)體工藝標(biāo)準(zhǔn),它的厚度也有一個(gè)理論的上限值。當(dāng)制程工藝由90nm向65nm過渡時(shí),雖然芯片的集成度得到了提升,但是想要將小于2nm的這層?xùn)艠O氧化層的厚度繼續(xù)降低,卻是十分困難。這一技術(shù)難題讓英特爾這樣的芯片巨頭也為之頭疼。

隨著芯片的加工工藝精度進(jìn)入原子級(jí)別,任何缺陷都被會(huì)被無限放大,比如在內(nèi)部結(jié)構(gòu)中僅僅缺少一個(gè)原子的厚度,就可能引起非常大的漏電流,這樣的漏電流不僅白白浪費(fèi)了電能,更是引起芯片嚴(yán)重發(fā)熱的原因。以早期的英特爾奔騰四CPU為例,有一半的功耗就是由于漏電被浪費(fèi)了。

如今的CPU的單核速度可達(dá)到4GHz,算力的提升也帶來了功耗和發(fā)熱量的水漲船高,這時(shí)如果還照方抓藥式地采用傳統(tǒng)的風(fēng)扇降溫,CPU內(nèi)部的熱量就會(huì)迅速攀升甚至將其融化。為了兼顧算力和功耗,工程師則采用了雙核芯片及多核的方法,走多核芯片路線以分擔(dān)單顆CPU的工作負(fù)荷間從而降低功耗和發(fā)熱。除此以外,此后材料的革新,也能夠?qū)暮蜕崞鸬搅朔浅4蟮膬?yōu)化作用。

二,神秘的測(cè)試

測(cè)試是檢驗(yàn)真理的唯一標(biāo)準(zhǔn)。就像學(xué)生時(shí)代的臨考前,老師們千叮嚀萬(wàn)囑咐的一句話:做完題目別著急交卷,先檢查檢查,在半導(dǎo)體制造過程中更是如此,從芯片的制造到交付出貨期間,芯片測(cè)試已成為了不可或缺的環(huán)節(jié)。

在所有電子元器件的制造工藝?yán)锩妫嬖谥未嬲娴男枰瑸榱藢?shí)現(xiàn)試驗(yàn)的過程,就需要各種試驗(yàn)設(shè)備,這類設(shè)備就是所謂的ATE(Automatic Test Equipment)。

ATE是一種通過計(jì)算機(jī)控制,進(jìn)行芯片、電路板和子系統(tǒng)等測(cè)試的設(shè)備,通過計(jì)算機(jī)編程取代人工勞動(dòng),自動(dòng)化地完成測(cè)試序列。ATE的應(yīng)用場(chǎng)合涵蓋集成電路整個(gè)產(chǎn)業(yè)鏈,主要包括了芯片的設(shè)計(jì)驗(yàn)證、晶圓制造相關(guān)的測(cè)試到封裝完成后的成品測(cè)試。

ATE市場(chǎng)的發(fā)展可以追溯到1960年代,早期的半導(dǎo)體測(cè)試設(shè)備發(fā)展并不完全是由獨(dú)立的設(shè)備商引導(dǎo),而是由半導(dǎo)體制造公司主導(dǎo)。仙童半導(dǎo)體(Fairchild)、德州儀器(TI)等制造企業(yè)生產(chǎn)ATE都是用于內(nèi)部使用,而從1980年代起,ATE領(lǐng)域開始進(jìn)行整合,2011年惠瑞捷(VERIGY)被收購(gòu)后,形成了以泰瑞達(dá)(Teradyne)和愛德萬(wàn)測(cè)試的雙寡頭格局。

回顧ATE的發(fā)展史,可以說泰瑞達(dá)是“第一個(gè)吃螃蟹的人”。早在1960年,兩位麻省理工高材生在波士頓創(chuàng)立了泰瑞達(dá)公司。如今,在波士頓總部的展示區(qū)域,依舊陳列著世界上第一臺(tái)ATE設(shè)備D133,它是1961年推出的第一臺(tái)二極管測(cè)試機(jī),標(biāo)志著自動(dòng)測(cè)試設(shè)備邁入全新紀(jì)元。Teradyne(泰瑞達(dá))的命名頗有意思,名字中的“Tera”取自10的12次方的前綴,“dyne”是力學(xué)的單位。如此命名,也意味著這家公司將是一股不容小覷的巨大力量。

從70年代到80年代早期的十年間,集成電路經(jīng)歷了由小規(guī)模到中規(guī)模再到大規(guī)模和超大規(guī)模的變遷。這時(shí)計(jì)算機(jī)控制的測(cè)試系統(tǒng)成為主要的測(cè)試設(shè)備。80年代中期,隨著門陣列器件的成功開發(fā),對(duì)于測(cè)試方面要求達(dá)到了256管腳,速度高于40MHz。進(jìn)入到90年代,單片處理器單元(MPU)的問世也帶來了高速高管腳數(shù)的ATE。隨后多媒體器件的出現(xiàn)使ATE變得更加復(fù)雜,需要同時(shí)具有數(shù)字電路、模擬電路和存儲(chǔ)器電路的測(cè)試能力。

近年來,工藝節(jié)點(diǎn)不斷提升,芯片制程工藝不斷逼近物理極限,這些也帶來了更高的集成度。隨之而來,整個(gè)芯片的功耗方案也要作出相對(duì)應(yīng)的改變。

當(dāng)下,先進(jìn)制程芯片具有非常復(fù)雜的供電系統(tǒng),測(cè)試成本不斷增加的同時(shí),測(cè)試環(huán)節(jié)對(duì)產(chǎn)品良率的監(jiān)控將會(huì)愈發(fā)重要,這樣的情況下,ATE該如何測(cè)試?

三,實(shí)際測(cè)試中的挑戰(zhàn)

實(shí)際測(cè)試中的挑戰(zhàn)

應(yīng)用處理器的測(cè)試機(jī)里有兩個(gè)非常重要的單元,其一是數(shù)字芯片測(cè)試的數(shù)字I/O,數(shù)字I/O承擔(dān)了相對(duì)復(fù)雜的工作,可以抓取失效;另一個(gè)就是電源,雖然DC電源看起來比較簡(jiǎn)單,但在實(shí)際的大功率處理器的測(cè)試中,電源在起到非常重要的作用,因?yàn)樗鼪Q定了測(cè)試質(zhì)量,最終測(cè)試的良率也與電源的實(shí)際性能息息相關(guān)。

展開來看,應(yīng)對(duì)不同的挑戰(zhàn),不同測(cè)試環(huán)節(jié)的測(cè)試參數(shù)和應(yīng)用場(chǎng)景稍有區(qū)別,就需要采取不同的解決方案。

對(duì)于復(fù)雜的供電問題,利用模塊化的供電策略可以降低多相位復(fù)雜供電的困擾。通過靈活地分配測(cè)試資源,將電源拆解成一個(gè)個(gè)小的電源模塊,任意組合成小的單元模塊給不同的電源軌供電,同時(shí)還可以利用冗余的電源模塊來幫助已經(jīng)預(yù)設(shè)好的模塊降低供電電源軌的穩(wěn)壓壓力。

簡(jiǎn)單舉例,一個(gè)需要30安培的VDD引腳,如果每個(gè)通道支持5安培的輸出能力,可以組合6個(gè)這樣的單元來供電,同時(shí)利用冗余的通道組合單元與前面的6個(gè)單元組合在一起降低供電壓力。

此外,還可以利用軟件編程的方式設(shè)定上電次序、軟啟動(dòng)等,以減少外圍供電電路。

對(duì)于大多數(shù)應(yīng)用處理器來說,工作頻率與VDD一般呈現(xiàn)正相關(guān)性。在前期的設(shè)計(jì)驗(yàn)證中,廠商會(huì)嘗試尋找sweet point使得芯片在有限的功耗下表現(xiàn)出更好的性能,在實(shí)際的生產(chǎn)測(cè)試中,可能會(huì)直接地設(shè)定一個(gè)指定的VDD,看其能否在這個(gè)特定的VDD下達(dá)到預(yù)期的頻率。

數(shù)據(jù)整理來自泰瑞達(dá)

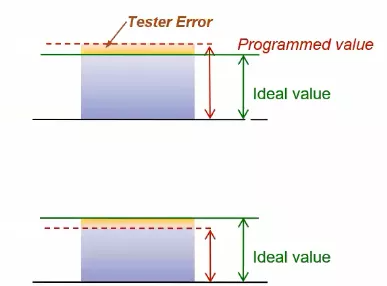

然而,在實(shí)際的測(cè)試中,沒有一款測(cè)試機(jī)是完美的。實(shí)際操作中,芯片會(huì)經(jīng)常性產(chǎn)生誤差,一種方式是嘗試編程稍高于芯片預(yù)設(shè)值的電壓,由于考慮芯片的誤差及所有的損耗,需要保證芯片引腳上的電壓依然高于預(yù)期值。通過這種測(cè)試方法,即使儀表波動(dòng)到最低的電壓情況下,質(zhì)量好的器件仍然可以pass,從而獲得更高的良率。

另一種方式,直接將測(cè)試儀表的輸出編程等于預(yù)期值,由于實(shí)際上一些測(cè)試機(jī)并不能達(dá)到良好的精準(zhǔn)度,在一些情況下略低于輸出,導(dǎo)致這部分的芯片實(shí)際測(cè)試電壓低于預(yù)期值。

這兩種方式會(huì)造成不同的負(fù)面效果。在第一種的情況下,VDD的預(yù)期值需要制定得更高一些,這樣的話實(shí)際的電壓會(huì)高于預(yù)期值,實(shí)際測(cè)試中的熱損耗也會(huì)更大,在測(cè)試中就需要低速的向量幫助降溫。

第二種情況下,雖然實(shí)際出貨的產(chǎn)品都能夠pass預(yù)期值,但是對(duì)于一些誤差比較大的機(jī)器,會(huì)造成額外的良率損失。對(duì)于7nm、5nm的先進(jìn)制程產(chǎn)品來說,良率是極其重要的一個(gè)因素,由于先進(jìn)制程產(chǎn)品尤其是晶圓面積較大時(shí)的良率本身非常低,在此基礎(chǔ)上如果又額外損失一部分良率,這對(duì)于器件制造成本是難以接受的。

面對(duì)種種挑戰(zhàn),我們?cè)撊绾螠y(cè)試?測(cè)試機(jī)應(yīng)該具備怎樣的特性滿足以上的諸多挑戰(zhàn)需求呢?

四,不同測(cè)試挑戰(zhàn)的對(duì)癥下藥

“Millivolts Matter”,每一個(gè)毫伏的精度都非常重要。越來越低的核心電壓對(duì)電源的輸出精度,以及動(dòng)態(tài)響應(yīng)提出了越來越高的要求。泰瑞達(dá)一直把電源儀表的輸出電壓能力作為儀表設(shè)計(jì)最重要的參數(shù)之一,這也是泰瑞達(dá)區(qū)分于眾多ATE廠商的特征之一。

在實(shí)際測(cè)試過程中電源的供電不是完全平坦的,實(shí)際的電源功耗與實(shí)際工況有很大關(guān)系,甚至?xí)?dǎo)致芯片丟失狀態(tài),從而導(dǎo)致器件失效。這樣的問題既難預(yù)測(cè)又很難排查。

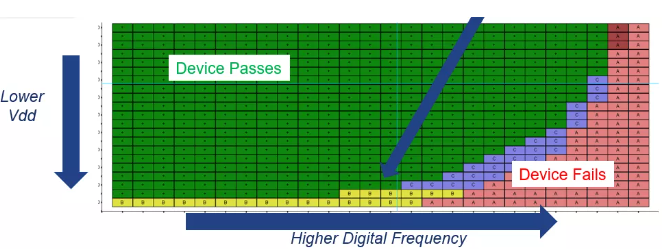

通過不斷改變輸出的VDD與Scan Shift頻率來查看所有測(cè)試向量的輸出結(jié)果,當(dāng)VDD越低頻率越高時(shí),越容易發(fā)生失效。在實(shí)際的Shmoo測(cè)試案例中,泰瑞達(dá)的UltraFLEXplus具有更穩(wěn)定的供電電源,這意味著可獲得更高的邊界良率,使得芯片更加貼近于真實(shí)的本征。這樣一來,在實(shí)際產(chǎn)品中,我們對(duì)于芯片的實(shí)際工況便能夠得到一個(gè)更加準(zhǔn)確的推斷,知道哪些情況是可以工作的,哪些情況是不能工作。總的來說,更好更穩(wěn)定電源不僅能夠提升良率,還能夠認(rèn)識(shí)芯片在真正工況下的工作狀態(tài)。

數(shù)據(jù)整理來自泰瑞達(dá)

目前,很多芯片需要非常大的電流供電能力,輸出一個(gè)非常大的電流能力對(duì)測(cè)試機(jī)來說已經(jīng)不是一個(gè)難題了,很多測(cè)試機(jī)已經(jīng)能夠輕松供給1000A的輸出能力。然而多工位測(cè)試的時(shí)候每個(gè)芯片的單個(gè)電源軌上電都要達(dá)到800 -1000A,測(cè)試機(jī)雖然能夠滿足1000A的靜態(tài)供電,它是否能夠滿足0A到1000A的單步上電過程,成為了一個(gè)難題。在多工位測(cè)試的時(shí)候,泰瑞達(dá)所提供的解決方案就能夠滿足單步上電的大電源供給。

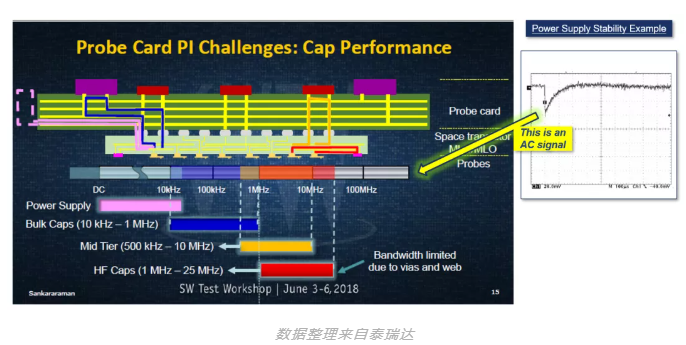

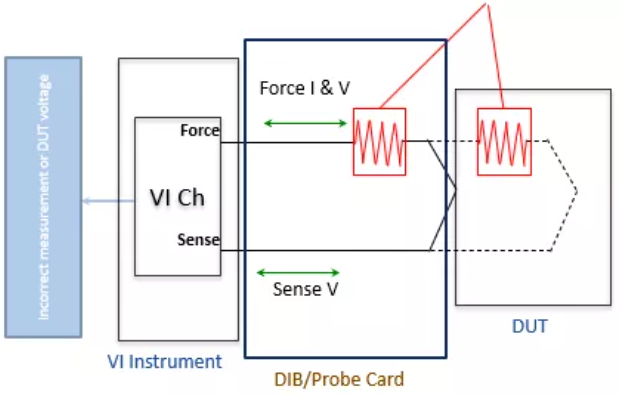

除了關(guān)注電源靜態(tài)、動(dòng)態(tài)的部分,在電源的外圍電路設(shè)計(jì)上,socket、探針卡、loadboard等與電源的性能也是息息相關(guān)。

測(cè)試儀表的動(dòng)態(tài)響應(yīng)對(duì)直流電源的表現(xiàn)影響非常大,優(yōu)秀的電源方案可以幫助減少外圍電源電路的復(fù)雜度。傳統(tǒng)的ATE解決方案首先需要板卡提供能量供給,大多供給從直流部分到100kHz的頻域范圍,針對(duì)低頻、中頻、高頻等其他頻段也需要增加不一樣的外圍電路,致使整體電路比較復(fù)雜。

泰瑞達(dá)側(cè)重于簡(jiǎn)化電路設(shè)計(jì),通過ATE本身就能提供從低頻到中頻的輸出能力,不需要增加額外的外圍電路,盡可能減少電容數(shù)量。在實(shí)際操作中,只需加入較少種類的低ESR/ESL陶瓷電容來幫助改變高頻特性,令單個(gè)型號(hào)就可滿足輸出的動(dòng)態(tài)性能。

這樣的好處在于:1)降低電容值以加速恢復(fù)時(shí)間;2)電容少意味著充放電時(shí)間更快,也就意味著充放電的能量會(huì)變少,這樣可以加速測(cè)試時(shí)間并降低socket被能量損傷的概率;3)降低電容使用種類,在使用單一電容的情況下,可以降低電路發(fā)生諧振、慢恢復(fù)等的可能性。

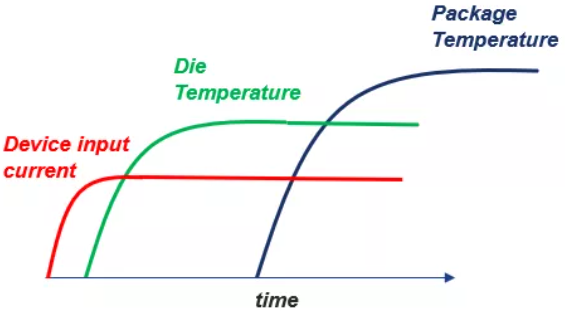

另一個(gè)比較大的挑戰(zhàn)在于測(cè)試單元,大功率的先進(jìn)制程芯片功率耗散非常大,多數(shù)輸出的能量最終都會(huì)轉(zhuǎn)化為熱量。我們?cè)跍y(cè)試時(shí)要避免芯片無限制地升溫導(dǎo)致芯片“被燒壞”,而是希望在測(cè)試參數(shù)的時(shí)候做到可重復(fù)、可重現(xiàn),使芯片維持在穩(wěn)定的情況下測(cè)試,保證所有收取數(shù)據(jù)的一致性。最直接的辦法可采用在測(cè)試單元的時(shí)候使用ATC(Automatic Temperature Control),常見的辦法有三種:方案一)DUT Power Monitor;方案二)Die Temperature Monitor;方案三)Package Temperature Monitor。

數(shù)據(jù)整理來自泰瑞達(dá)

三種方式各有利弊,在時(shí)間上的效益也不同(如上圖),泰瑞達(dá)更加傾向于使用方案一,其優(yōu)點(diǎn)在于可以更早預(yù)判芯片接下來可能發(fā)生的狀態(tài)并提前介入;其次,泰瑞達(dá)測(cè)試機(jī)原身也能夠支持這種方式,輸出每一個(gè)DPS當(dāng)下負(fù)載的百分比以及輸出電壓的大小。

在很多實(shí)際量產(chǎn)的案例中,泰瑞達(dá)已經(jīng)使用了這種監(jiān)控方式,對(duì)比方案二、三可以更早預(yù)知芯片的實(shí)際工況。

芯片功率不斷加大的情況下電路變得更加復(fù)雜,我們希望在測(cè)試的過程中所有的socket、探針卡、loadboard等都能得到比較好的監(jiān)控,保證在短路、接觸不良等異常情況發(fā)生時(shí)不會(huì)因此而損壞測(cè)試部件。

為避免這種情況發(fā)生,泰瑞達(dá)在設(shè)計(jì)大部分測(cè)試板卡的過程中會(huì)添加實(shí)時(shí)的報(bào)警機(jī)制,一旦任何異常發(fā)生,能夠在不影響其他設(shè)備生產(chǎn)和中斷生產(chǎn)的情況下,通過測(cè)試機(jī)作出實(shí)時(shí)警告,提前篩查避免異常情況的出現(xiàn),減少測(cè)試漏測(cè)、質(zhì)量事故等情況的發(fā)生。

數(shù)據(jù)整理來自泰瑞達(dá)

總結(jié)

半導(dǎo)體測(cè)試就是通過測(cè)量半導(dǎo)體的輸出響應(yīng)、預(yù)期輸出、并進(jìn)行比較以確定或評(píng)估集成電路功能和性能的過程,貫穿設(shè)計(jì)、制造、封裝、應(yīng)用全過程。隨著半導(dǎo)體制造工藝要求的提升,測(cè)試環(huán)節(jié)在半導(dǎo)體制造過程中的地位隨之不斷提升。

半導(dǎo)體測(cè)試機(jī)的技術(shù)核心在于功能集成、精度與速度、降低成本與可擴(kuò)展性。在泰瑞達(dá)看來,測(cè)試解決方案要有足夠好的靜態(tài)精度及穩(wěn)壓能力,同時(shí)在邊界情況下獲得更好的魯棒性來幫助降低失效的概率;盡可能簡(jiǎn)化外圍電路的設(shè)計(jì),降低運(yùn)營(yíng)方面的損失,側(cè)面降低測(cè)試成本;最后加入警報(bào)機(jī)制來提前預(yù)判,避免發(fā)生異常情況。