寬帶數(shù)據(jù)轉(zhuǎn)換器應(yīng)用的JESD204B與串行LVDS接口考量

2021-11-02

作者:George Diniz,產(chǎn)品線經(jīng)理

來源:ADI公司

摘要

開發(fā)串行接口業(yè)界標(biāo)準(zhǔn)JESD204A/JESD204B的目的在于解決以高效省錢的方式互連最新寬帶數(shù)據(jù)轉(zhuǎn)換器與其他系統(tǒng)IC的問題。其動(dòng)機(jī)在于通過采用可調(diào)整高速串行接口,對接口進(jìn)行標(biāo)準(zhǔn)化,降低數(shù)據(jù)轉(zhuǎn)換器與其他器件(如現(xiàn)場可編程門陣列FPGA和系統(tǒng)級芯片SoC)之間的數(shù)字輸入/輸出數(shù)量。

趨勢顯示最新應(yīng)用,以及現(xiàn)有應(yīng)用的升級,正不斷需求采樣頻率和數(shù)據(jù)分辨率更高的寬帶數(shù)據(jù)轉(zhuǎn)換器。向這些寬帶轉(zhuǎn)換器傳送和獲取數(shù)據(jù)暴露了一個(gè)非常大的設(shè)計(jì)問題,即現(xiàn)有I/O技術(shù)帶寬的限制導(dǎo)致轉(zhuǎn)換器產(chǎn)品需要使用的引腳數(shù)更多。其結(jié)果便是PCB設(shè)計(jì)隨著互連密度的增加而更復(fù)雜。其挑戰(zhàn)在于進(jìn)行大量高速數(shù)據(jù)信號走線的同時(shí)控制電噪聲,以及提供GSPS級別的寬帶數(shù)據(jù)轉(zhuǎn)換器采樣頻率的能力、使用更少的互連、簡化PCB布局難題并實(shí)現(xiàn)更小的尺寸,且不降低整體系統(tǒng)性能。

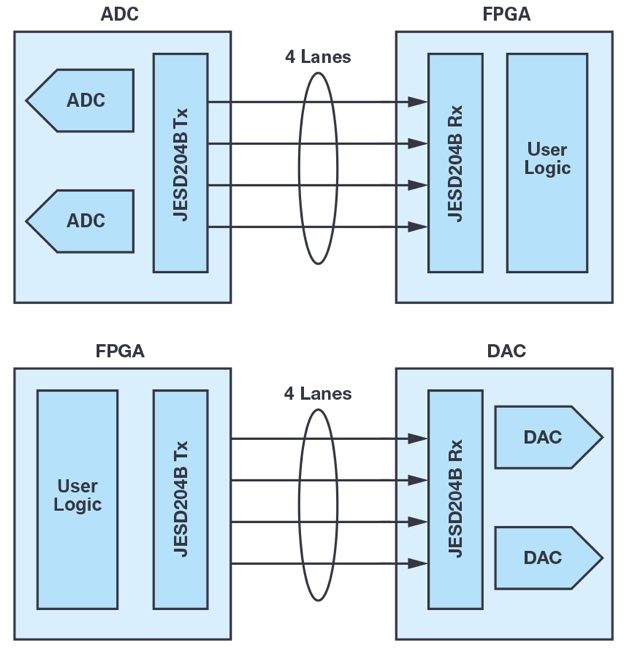

市場力量繼續(xù)施壓,要求給定系統(tǒng)擁有更多特性和功能以及更好的性能,推動(dòng)了對更高數(shù)據(jù)處理能力的要求。高速模數(shù)轉(zhuǎn)換器和數(shù)模轉(zhuǎn)換器至FPGA接口已成為某些系統(tǒng)OEM廠商滿足下一代大量數(shù)據(jù)處理需要的限制因素。JESD204B串行接口規(guī)范專為解決這一關(guān)鍵數(shù)據(jù)鏈路的問題而建立。圖1顯示使用JESD204A/JESD204B的典型高速轉(zhuǎn)換器至FPGA互連配置。

本文余下篇幅將探討推動(dòng)該規(guī)范發(fā)展的某些關(guān)鍵的終端系統(tǒng)應(yīng)用,以及串行低壓差分信號(LVDS)和JESD204B的對比。

圖1.使用JESD204A/JESD204B接口的典型高速轉(zhuǎn)換器至FGPA互連配置(來源:Xilinx?)。

應(yīng)用推動(dòng)對JESD204B的需求

無線基礎(chǔ)設(shè)施收發(fā)器

目前無線基礎(chǔ)設(shè)施收發(fā)器采用LTE等基于OFDM的技術(shù),這類技術(shù)使用部署FPGA或SoC器件的DSP模塊,通過驅(qū)動(dòng)天線陣列元件,單獨(dú)為每個(gè)用戶的手機(jī)產(chǎn)生波束。在發(fā)射和接收模式下,每個(gè)陣列元件每秒可能需要在FPGA和數(shù)據(jù)轉(zhuǎn)換器之間傳輸數(shù)百兆字節(jié)的數(shù)據(jù)。

軟件定義無線電

當(dāng)今的軟件定義無線電技術(shù)利用先進(jìn)的調(diào)制方案,可即時(shí)重配置,并極大地增加了通道帶寬,提供最佳的無線數(shù)據(jù)速率。天線路徑中高效、低功耗、低引腳數(shù)的FPGA至數(shù)據(jù)轉(zhuǎn)換器接口對性能起著決定性的作用。軟件定義無線電架構(gòu)已與收發(fā)器基礎(chǔ)設(shè)施相整合,用于多載波、多模無線網(wǎng)絡(luò),支持GSM、EDGE、W-CDMA、LTE、CDMA2000、WiMAX和TD-SCDMA。

醫(yī)療成像系統(tǒng)

醫(yī)療成像系統(tǒng)包括超聲、計(jì)算機(jī)斷層掃描(CT)的掃描儀、磁共振成像(MRI)等,這些應(yīng)用產(chǎn)生很多通道的數(shù)據(jù),流經(jīng)數(shù)據(jù)轉(zhuǎn)換器至FPGA或DSP。I/O通道數(shù)的持續(xù)增長要求使用內(nèi)插器匹配FPGA和轉(zhuǎn)換器的引腳輸出,迫使元件數(shù)增加,并使PCB復(fù)雜化。這加大了客戶系統(tǒng)的成本支出以及復(fù)雜程度;而這些問題可通過采用更有效的JESD204B接口加以解決。

雷達(dá)和安全通信

目前先進(jìn)雷達(dá)接收器的脈沖結(jié)構(gòu)日益復(fù)雜,迫使信號帶寬上升至1 GHz或更高。最新的有源電子調(diào)整陣列(AESA)雷達(dá)系統(tǒng)可能包含上千個(gè)元件。高帶寬SERDES串行接口用于連接陣列元件數(shù)據(jù)轉(zhuǎn)換器與FPGA或DSP,處理接收到的數(shù)據(jù)流,并將處理后產(chǎn)生的數(shù)據(jù)流發(fā)送出去。

串行LVDS與JESD204B的對比

在串行LVDS和JESD204B接口之間選擇

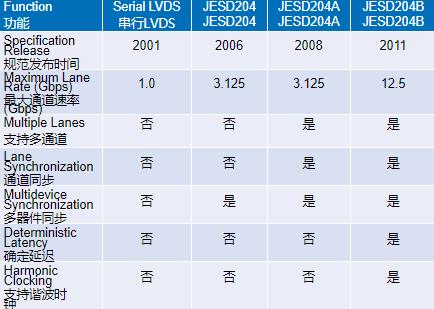

為了在使用LVDS和多種版本JESD204串行接口規(guī)范的轉(zhuǎn)換器產(chǎn)品間做出最佳選擇,對每種接口的特性和功能進(jìn)行比較會非常有用。表1以簡單的表格形式對接口標(biāo)準(zhǔn)進(jìn)行了對比。在SERDES級,LVDS和JESD204之間的顯著區(qū)別是通道數(shù)據(jù)速率,JESD204支持的每通道串行鏈路速率是LVDS的三倍以上。當(dāng)比較諸如多器件同步、確定延遲和諧波時(shí)鐘等高級功能時(shí),JESD204B是提供這些功能的唯一接口。所有通路和通道對確定延遲敏感、需要寬帶寬多通道轉(zhuǎn)換器的系統(tǒng)將無法有效使用LVDS或并行CMOS。

表1.串行LVDS和JESD204規(guī)范對比

LVDS概述

LVDS是連接數(shù)據(jù)轉(zhuǎn)換器與FPGA或DSP的傳統(tǒng)方法。LVDS于1994發(fā)布,目標(biāo)在于提供比已有的RS-422和RS-485差分傳輸標(biāo)準(zhǔn)更高的帶寬和更低的功耗。隨著1995年TIA/EIA-644的發(fā)布,LVDS成為標(biāo)準(zhǔn)。二十世紀(jì)90年代末,LVDS的使用率上升,并隨著2001年TIA/EIA-644-A的發(fā)布,LVDS標(biāo)準(zhǔn)亦發(fā)布了修訂版。

LVDS采用低電壓擺幅的差分信號,用于高速數(shù)據(jù)的傳輸。發(fā)射器驅(qū)動(dòng)的電流典型值為±3.5 mA,通過100 Ω電阻發(fā)送極性匹配的邏輯電平,在接收器端產(chǎn)生±350 mV電壓擺幅。電流始終導(dǎo)通,并被路由至不同方向以便產(chǎn)生邏輯1和邏輯0。LVDS始終導(dǎo)通的特性有助于抑制同步開關(guān)噪聲尖峰和潛在電磁干擾——在單端技術(shù)中,晶體管的開關(guān)動(dòng)作可能產(chǎn)生這些噪聲和干擾。LVDS差分的特征同樣提供了針對共模噪聲源的有效抑制。雖然在理想傳輸介質(zhì)中,該標(biāo)準(zhǔn)預(yù)測速率可能超過1.9 Gbps,但TIA/EIA-644-A標(biāo)準(zhǔn)建議的最大數(shù)據(jù)速率為655 Mbps。

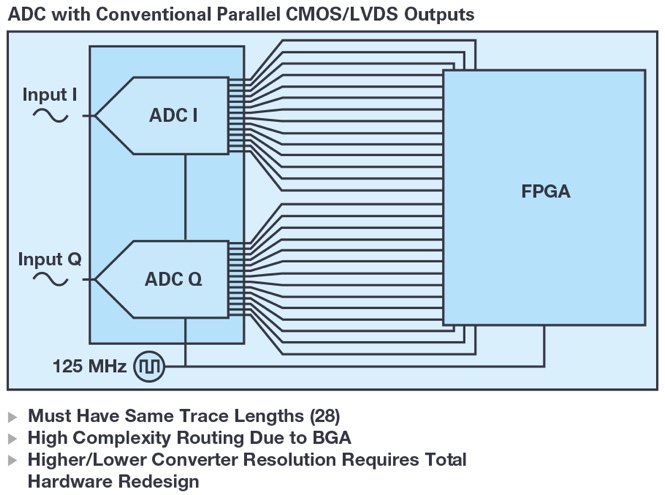

FPGA或DSP與數(shù)據(jù)轉(zhuǎn)換器間數(shù)據(jù)通道和速度的大幅增長——尤其是前文討論的那些應(yīng)用——使LVDS接口暴露了一些問題(見圖2)。現(xiàn)實(shí)中,差分LVDS線的帶寬限制在1.0 Gbps左右。在目前很多應(yīng)用中,這一限制導(dǎo)致需要許多高帶寬PCB互連,而每一處都有可能出故障。大量的走線還增加了PCB的復(fù)雜性或整體尺寸,導(dǎo)致設(shè)計(jì)和制造成本上升。在某些帶寬需求量巨大的應(yīng)用中,數(shù)據(jù)轉(zhuǎn)換器接口已成為滿足所需系統(tǒng)性能的制約因素。

圖2.使用并行CMOS或LVDS帶來的系統(tǒng)設(shè)計(jì)與互連的挑戰(zhàn)。

JESD204B概述

JESD204數(shù)據(jù)轉(zhuǎn)換器串行接口標(biāo)準(zhǔn)由JEDEC固態(tài)技術(shù)協(xié)會JC-16接口技術(shù)委員會建立,目標(biāo)是提供速率更高的串行接口、提升帶寬并降低高速數(shù)據(jù)轉(zhuǎn)換器和其他器件之間的數(shù)字輸入和輸出通道數(shù)。該標(biāo)準(zhǔn)的基礎(chǔ)是IBM開發(fā)的8b/10b編碼技術(shù),它無需幀時(shí)鐘和數(shù)據(jù)時(shí)鐘,支持以更高的速率進(jìn)行單線對通信。

2006年,JEDEC發(fā)布JESD204規(guī)范,使單數(shù)據(jù)通道上的速率達(dá)到3.125 Gbps。JESD204接口是自同步的,因此無需校準(zhǔn)PCB布線長度,避免時(shí)鐘偏斜。JESD204依靠許多FPGA提供的SERDES端口,以便釋放通用I/O。

JESD204A于2008年發(fā)布,增加了對多路時(shí)序一致數(shù)據(jù)通道和通道同步的支持。這種增強(qiáng)使得使用更高帶寬的數(shù)據(jù)轉(zhuǎn)換器和多路同步數(shù)據(jù)轉(zhuǎn)換器通道成為可能,并且對用于蜂窩基站的無線基礎(chǔ)設(shè)施收發(fā)器尤為重要。JESD204A還提供多器件同步支持,這有利于醫(yī)療成像系統(tǒng)等使用大量ADC的應(yīng)用。

JESD204B是該規(guī)范的第三個(gè)修訂版,將最大通道速率提升至12.5 Gbps。JESD204B還增加了對確定延遲的支持,該功能可在接收器和發(fā)射器之間進(jìn)行同步狀態(tài)的通信。JESD204B還支持諧波時(shí)鐘,使得依據(jù)確定相位,通過低速輸入時(shí)鐘獲得高速數(shù)據(jù)轉(zhuǎn)換器時(shí)鐘成為可能。

結(jié)論

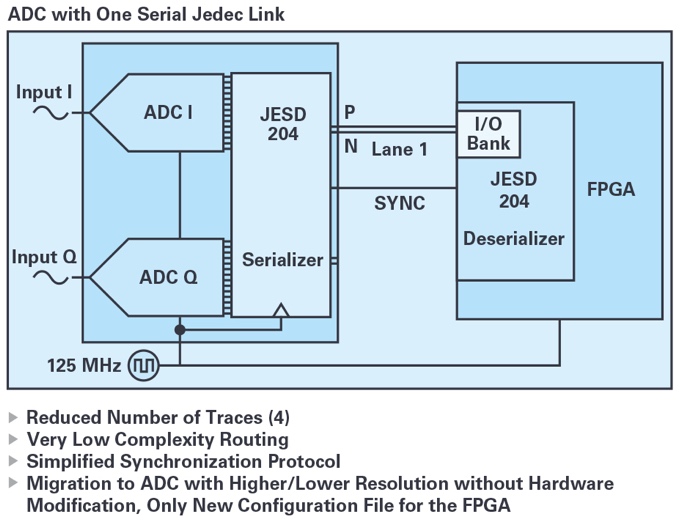

JESD204B工業(yè)串行接口標(biāo)準(zhǔn)降低了高速數(shù)據(jù)轉(zhuǎn)換器和FPGA以及其他器件之間的數(shù)字輸入和輸出通道數(shù)。更少的互連可以簡化布局布線,并讓實(shí)現(xiàn)更小的尺寸設(shè)計(jì)成為可能(見圖3)。這些優(yōu)勢對很多高速數(shù)據(jù)轉(zhuǎn)換器應(yīng)用非常重要,例如無線基礎(chǔ)設(shè)施收發(fā)器、軟件定義無線電、醫(yī)療成像系統(tǒng),以及雷達(dá)和安全通信。ADI公司是JESD204標(biāo)準(zhǔn)委員會的創(chuàng)始成員,我們同時(shí)開發(fā)出了兼容的數(shù)據(jù)轉(zhuǎn)換器技術(shù)和工具,并推出了全面的產(chǎn)品路線圖。通過為客戶提供結(jié)合了我們先進(jìn)數(shù)據(jù)轉(zhuǎn)換器技術(shù)以及集成JESD204A/JESD204B接口的產(chǎn)品,我們有望充分利用這項(xiàng)重大的接口技術(shù)突破,幫助客戶解決系統(tǒng)設(shè)計(jì)難題。

圖3.JESD204具有高速串行I/O能力,能夠解決系統(tǒng)PCB復(fù)雜性挑戰(zhàn)。

作者簡介

George Diniz是ADI公司高速數(shù)模轉(zhuǎn)換器部門(北卡羅來納州格林斯博羅)的產(chǎn)品線經(jīng)理。他領(lǐng)導(dǎo)的開發(fā)團(tuán)隊(duì),負(fù)責(zé)開發(fā)JESD204B接收器和收發(fā)器接口內(nèi)核,用于集成到高速模數(shù)和數(shù)模轉(zhuǎn)換器產(chǎn)品中。他擁有25年半導(dǎo)體行業(yè)工作經(jīng)驗(yàn),擔(dān)任過設(shè)計(jì)工程和產(chǎn)品線管理等各種職務(wù)。在加入ADI之前,George是IBM的一名設(shè)計(jì)工程師,他在IBM從事功率PC處理器的自定義SRAM宏、PLL和DLL函數(shù)的混合信號設(shè)計(jì)。他擁有北卡羅來納州立大學(xué)電氣工程碩士學(xué)位(MSEE)和曼哈頓學(xué)院電氣工程學(xué)士學(xué)位(BSEE)。在娛樂方面,George喜歡戶外活動(dòng)、修理汽車和跑步。