現(xiàn)在云計算、存儲和機器學習等領先應用需要傳輸大量數據,這要求開發(fā)者以最小的延遲集成最新的高速接口,以滿足這些系統(tǒng)的帶寬需求。PCIe作為歷史上使用最廣泛、可擴展最強的互連技術,其創(chuàng)新的步伐正在加快,如今PCIe 6.0標準已然來臨。對于高性能計算、AI和存儲SoC開發(fā)者來說,轉向PCIe 6.0為設計師提供了一系列關于IP、SoC和系統(tǒng)的考慮。及時理解并做好所需要的面對的關鍵變化,以及由此帶來的設計挑戰(zhàn),將有助于其順利過渡到PCIe 6.0時代。

PCIe 6.0的新變化

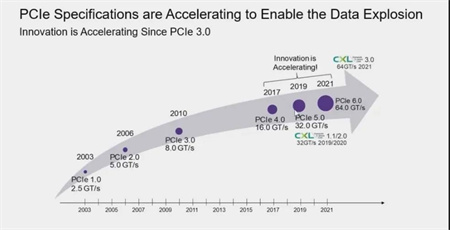

過去,PCIe的標準基本保持在3-4年一更迭的速度,但自PCle 3.0以來,PCIe的標準正在快速演進,基本在2年一更新,到現(xiàn)在已經到了PCIe 6.0的時代。PCle標準的加速也是數據爆炸的使然。

圖1:PCIe標準的演進路線圖(來源:新思科技)

那么,PCIe 6.0有哪些新變化呢?首先是數據速率從32GT/s翻倍至64GT/s,吞吐量在大多數情況下超過兩倍;其次,保持其兼容性,PCIe 6.0向后支持所有PCIe的標準;再者,PCle 6.0 PHY IP必須為所有PCle 6.0數據速率提供出色的性能,所以從NRZ編碼轉換到PAM-4編碼,以及由此帶來的糾錯影響,PAM-4適用于新Gen6 64GT/s。

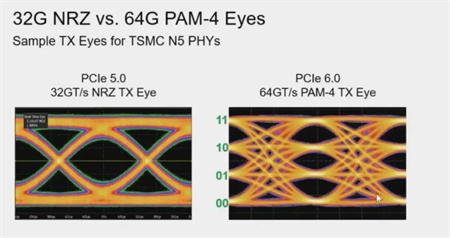

下圖就很好的解釋了為何PCIe 6.0會引入PAM-4。可以看出,當數據速率從16GT/s加倍到32GT/s時,奈奎斯特頻率也從8GHz加倍到16GHz,使得PCIe 5.0的頻率相關損耗比PCIe 4.0要嚴重得多。再加上電容耦合(噪聲和串擾)的增加,使得PCIe 5.0通道成為最難處理的NRZ通道。如果PCIe 6.0仍然保留NRZ信號,則奈奎斯特頻率將增加到32GHz,通道損耗大于60dB,這對于實際系統(tǒng)而言太大了,因此需要從NRZ更改為PAM-4信號。這一變化意味著發(fā)射和接收的信號現(xiàn)在有四個不同的電壓電平,而不是兩個。

圖2:NRZ通道面臨的挑戰(zhàn)(來源:新思科技)

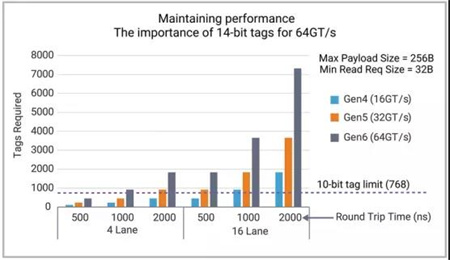

其他額外的變化是,PCIe 6.0采用了新的輕量級FEC,平均往返時延約為2ns;PCIe 6.0引入新的FLIT模式,采用了256B FLIT作為標準大小的數據傳輸單元;由于FEC要求,F(xiàn)LIT模式現(xiàn)在支持所有數據速率;PCIe 6.0引入了一種新的低功耗狀態(tài),稱為L0p,允許PCIe 6.0鏈路在不中斷數據流的情況下擴展帶寬利用率,從而降低功耗;為了在64GT/s下保持性能,PCIe 5.0的768個標簽限制遠遠不足以支持大多數PCIe 6.0系統(tǒng)的性能,因此標簽數量最大值急劇增加,變?yōu)榛?4位的15,360個標簽。除此之外,單個應用程序接口可能不再足夠,所以使用多個應用接口來提高PCIe 6.0鏈路利用率。

下圖顯示了在相同比例的眼圖,圖1(a)顯示了使用NRZ信號的PCIe 5.0的眼圖,包含兩個電壓電平和單眼。圖(b)顯示了使用PAM-4信號的PCIe 6.0的眼圖,包含四個電壓電平和三眼。由于發(fā)射端(TX)的總體電壓擺幅沒有增加,因此PAM-4系統(tǒng)中每只眼的可用電壓僅為NRZ的1/3。因此,信號在TX和接收端(RX)之間遇到的任何噪聲都會對信號完整性造成更大的損害。這也是為什么需要在進行PAM-4信號傳輸時,需要額外的FEC支持的原因。

圖3:32G NRZ VS 64G PAM-4眼圖(來源:新思科技)

PHY IP該如何應對?

要滿足PCIe 6.0的上述新變化,對PHY層來說也有一定的需求變化。因為PCIe 6.0需要支持64GT/s的帶寬,所以速率需要從原來的32G變?yōu)?4G。另外一點是不僅要支持PCIe 6.0 64G的PAM-4,還需要支持從低速的2.5G-32G的NRZ,向后兼容所有PCIe的標準。另外還需要引入輕量級的FEC,使得PHY BER能滿足<=1e-06的要求。輕量級FEC結合CRC和重試,以減少延遲影響。還需要支持新L0p的低功耗要求。在PCle 6.0速率下,支持32db的信道損耗。

大家都知道,新思科技在Serdes中已經可以達到112G的Ethernet,但對于PCIe 6.0來說,并不是只通過降速就可以滿足其要求,還要考慮低延遲、SSC/SRIS的支持、更復雜的發(fā)射機、低功率狀態(tài)、100x更嚴格的誤碼率要求等等。所以對于PCIe 6.0,新思有單獨的支持64G速率的方案。

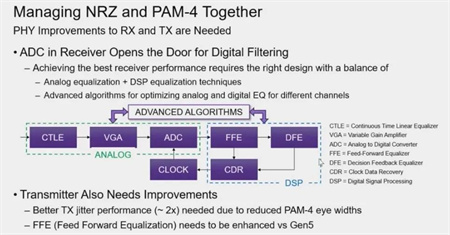

上面我們提到PHY的接收通路不僅要滿足NRZ,也要滿足PAM-4。所以PHY在接收端采用了特別的模擬+DSP的組合架構,可以滿足對于功耗和接收性能的兼顧。再者,發(fā)射通路也需要加以改進,如上圖3所示,PAM-4的信號眼圖相對NRZ會變得更為嚴格,所以對于發(fā)送通路的發(fā)送信號的質量要求會更高。由于減少了PAM-4眼寬,所以需要更好的TX抖動性能(~ 2x);而且與Gen5相比,F(xiàn)FE(前饋均衡)也需要加強。

圖4:為了同時滿足NRZ和PAM-4,需對接收端和發(fā)送端進行改進(來源:新思科技)

PCIe 6.0 FLIT模式的新L0p低功耗狀態(tài),能帶來真正的帶寬/功率縮放。L0p可以根據鏈路的數據吞吐量去動態(tài)改變有效的車道(lane)的數量。比如說在高吞吐量的需求情況下,可以將所有的車道都開起來,當不需要那么高的吞吐量時,可以關閉多余的車道,這樣就可以做到真正的節(jié)省功率。值得一提的是,這種調整是不需要做PHY層的訓練等,這是PCIe 6.0新的L0p的低功耗Power State的功能。

圖5:新的L0p可以根據鏈路的數據吞吐量去動態(tài)改變有效的車道(lane)的數量 (來源:新思科技)

但在數據結構方面,PHY是有所區(qū)別的。前文我們提到PCIe 6.0采用了256B FLIT作為標準大小的數據傳輸單元。這就要求在FLIT模式下需要將可變數量的TLP重新封裝到256B固定長度的FLIT數據結構中。這是IP設計中需要引入的新的變化。此外,F(xiàn)LIT自帶完整性的校驗,所以在吞吐量和數據傳輸方面的開銷對于TLP或者DLP會更有優(yōu)勢,所以可以將TLP或DLP直接封裝到FLIT里面,F(xiàn)LIT的overhead比較小,所以對鏈路的性能是有提升的。

圖6:使用FEC需要固定大小的數據單位,而不是可變的TLP(來源:新思科技)

PCIe 6.0為了滿足高效的post數據傳輸,需要引入高比特tag的需求。如圖7所示,當16個lane都工作的時候,要滿足高性能的要求需要將近7000多個tags的數量,意味著tag的位寬要達到14bit,所以進行控制器設計的時候,需要能夠處理這么多的post的能力。

圖7:達到第4代到第6代鏈路的最大吞吐量所需的tag數量(來源:新思科技)

在應用層接口方面,PCIe 6.0可以做到1024G這樣高的數據傳輸,如果在應用層采用單獨的接口的話,鏈路利用率會比較低,所以PCIe 6.0將采用雙接口的方式。例如在32Byte的Payload下面,兩個接口相對于一個接口的話,其鏈路利用率將能達到80%的提升。

圖8:單接口和雙接口應用程序接口的傳輸鏈路利用率和控制器數據路徑寬度(來源:新思科技)

對驗證IP和系統(tǒng)層面的挑戰(zhàn)

PCie 6.0的到來也為驗證和系統(tǒng)層面帶來的許多新的挑戰(zhàn)。首先,驗證必須要充分涵蓋PAM-4、FEC、FLIT模式、Equalization的更新以及PIPE 6.0接口。再者,驗證需要校驗方案中有大量的協(xié)議檢查,降低PCle 5.0到PCle 6.0遷移的風險。需要增強對模擬誤碼率的功能檢測,還需要完整的FLIT控制和操作的驗證。

所以綜合來講,PCIe 6.0標準下的驗證IP應該能支持最新的PCle 6.0規(guī)范版本;要有一個全面的源代碼測試套件;同時使用分層控制實現(xiàn)廣泛的協(xié)議檢查,可以覆蓋到成千上百的應用需求;支持分岔的多鏈路DUT,對內置(控制器)和客戶(客戶自己)情況的魯棒錯誤注入的支持,支持所有拓撲,包括根復雜,端點,應用程序層,主動/被動監(jiān)控,也要覆蓋到廣泛的PHY驗證。

在系統(tǒng)層面,如果PCIe 6.0和控制器能有綜合完整的解決方案,對于系統(tǒng)的吞吐量、兼容性和有效性來說是非常有利的。另外,PCIe 6.0采用的是PIPE接口選項,PIPE 5接口規(guī)范不支持PCIe 6.0,必須指定支持PCle 6.0的最新版本PIPE 6規(guī)范。再者,PCle 6.0的行業(yè)正在轉向SerDes架構,它簡化了64GT /s PHY設計,支持CXL 3.0對低時延的要求。

此外,還要考慮數據路徑和時間的問題,只有2個可行的選擇,以權衡時間關閉和延遲。一個是在1 GHz定時關閉。要關閉1GHz PIPE接口的計時,必須使用64b (80b) PIPE。對于x16鏈路,需要有16 * 64b = 1024的超寬的數據路寬。另一個是最小延遲選項。為了減少延遲,時鐘可以運行在2GHz,將周期削減到0.5 ns/時鐘,時鐘必須在2GHz的管道接口關閉,對于x16鏈路,控制器數據路徑為512b。

圖9:數據路徑和時間考慮 (來源:新思科技)

對于封裝來說,64G的封裝設計需要新的考慮。因為在同樣的奈奎斯特下,從NRZ 轉換為 PAM-4,其信噪比更惡劣9.6dB。而且PCle 6.0的封裝從TX 到 RX 需要滿足- 60db (PCIe 5.0是50dB)到16Ghz的Xtalk Spec。除此之外,還有一些返回損耗和反射、插入損耗,和串擾控制的要求都很高。

首個PCIe 6.0 完整IP解決方案已出

在PCle 5.0方面,新思科技已經擁有超過170個許可的應用。在PCIe 6.0標準下,目前新思科技已推出業(yè)界首個PCI Express 6.0完整IP解決方案DesignWare IP ,包括控制器、PHY和驗證 IP。可實現(xiàn)PCIe 6.0 SoC設計的早期開發(fā)。

DesignWare IP完全支持PCIe 6.0規(guī)范,其中包括64GT/s PAM-4信號傳輸、FLIT模式和L0p功耗狀態(tài)。新思科技的完整IP解決方案可滿足高性能計算、AI和存儲SoC在延遲、帶寬和功耗效率方面不斷提高的要求。

如前文所列出的諸多挑戰(zhàn),新思科技都做了很好的應對。新思科技面向PCIe 6.0的DesignWare PHY IP在5納米工藝中的高性能PHY采用獨特的模擬和DSP技術,可在芯片對芯片、轉接卡和背板接口上節(jié)省20%的功耗。面向PCIe 6.0的DesignWare PHY IP感知布局架構可最大限度地減少封裝串擾,并支持針對x16鏈路的密集SoC集成。

DesignWare控制器采用了MultiStream架構,可提供相當于Single-Stream設計2倍的性能。該控制器采用1024位架構,可讓開發(fā)者在1GHz時序收斂的條件下實現(xiàn)64GT/s x 16的帶寬。此外,該控制器還可在處理多個數據源以及使用多個虛擬通道時提供最佳流量。

為了通過內置驗證計劃、序列和功能覆蓋來加快測試平臺的開發(fā),面向PCIe的VC驗證IP采用了本地SystemsVerilog/UVM架構,只需小量的工作即可完成集成、配置和定制。

DesignWare IP的推出將是設計者的一大福音,它能幫助開發(fā)者很好的解決從PCIe 5.0過渡到PCIe 6.0的諸多難題,加速其在芯片領域的成功之路。