1. 概述

為了適應未來硬件加速、網絡加速對片外存儲器的帶寬需求,目前市面上的高端FPGA主要采用了兩種解決方法。第一種最常見的就是HBM2高帶寬存儲器,2016年1月,HBM的第二代技術HBM2正式成為工業(yè)標準。集成了HBM2存儲器的高端FPGA可以提供高達460GB/s的帶寬,但是因為HBM2技術工藝要求高,目前芯片的良率和產量都會受到很大的影響,所以集成HBM2的高端FPGA成本一直居高不下。第二種是GDDR6存儲器,2018年,GDDR6發(fā)布,數據速率達到了16Gbps。Achronix看中了GDDR6在數據存儲中的帶寬優(yōu)勢,在新一代7nm工藝的Speedster7t FPGA集成了GDDR6硬核控制器,最高可支持高達512GB/s的帶寬,同時可以有效地控制使用成本。

2. Speedster7t FPGA中的GDDR6控制器

Achronix的Speedster7t FPGA集成了8個GDDR6的硬核,如圖1所示。

圖1 Speedster7t FPGA架構

每個GDDR6的硬核支持雙通道。總的帶寬是16Gbps x 16(位寬) x 2(通道) x 8(控制器)/8 = 512 GB/s,每個控制器有兩個獨立的訪問通道,每個通道的數據位寬為16位。這些GDDR6 控制器和PHY都是硬IP,無需消耗FPGA中的可編程邏輯資源,也無需面對布局布線所帶來的時序收斂挑戰(zhàn)。這些特征共同使GDDR6方案成為當前高端FPGA性能和成本兼顧的絕佳選擇。

3. GDDR6子系統(tǒng)概述

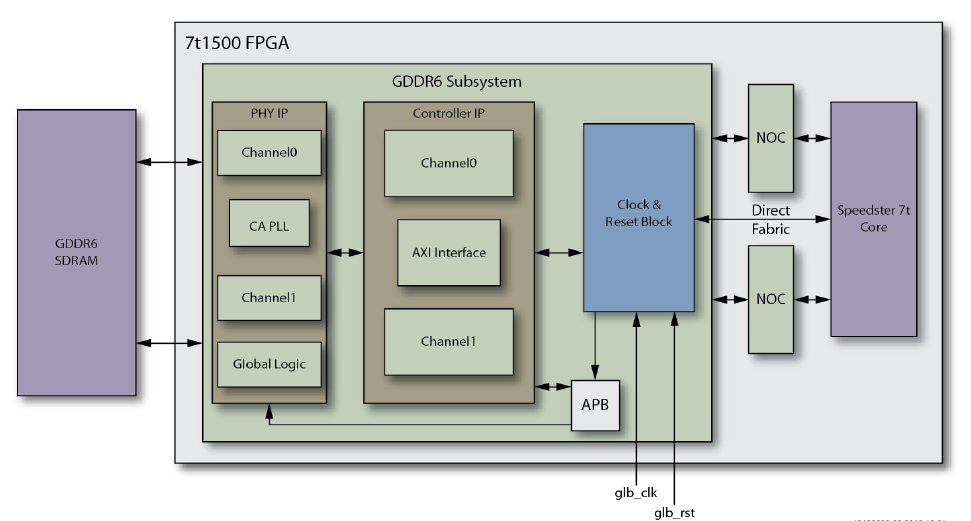

Achronix Speedster7t GDDR6子系統(tǒng)包括GDDR6 PHY和GDDR6控制器,全部采用了硬核設計。整個子系統(tǒng)包括GDDR6 PHY IP、GDDR6控制器IP、時鐘和復位模塊,APB接口和AXI4用戶接口可以連接到二維片上網絡(2D NoC)或者內部編程邏輯,如圖2所示。

圖2 Speedster7t GDDR6子系統(tǒng)框圖

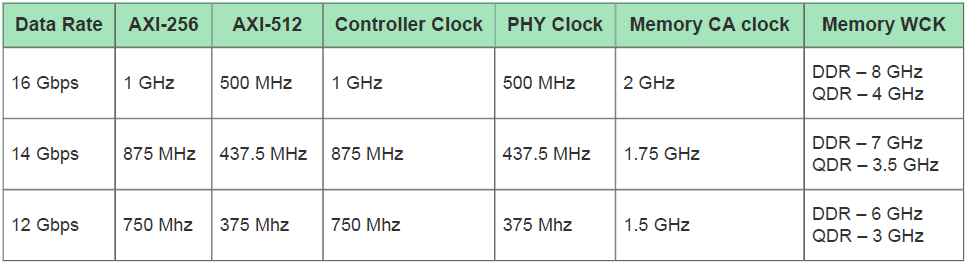

時鐘和復位模塊用來產生支持GDDR6 PHY和GDDR6控制器的時鐘以及所需的復位信號,它的輸入時鐘來自于FPGA片上的PLL。對于數據速率為16Gbps的GDDR6,控制器時鐘為1GHz,PHY時鐘為500MHz,命令地址時鐘跑在2GHz,word clk也就是WCLK運行在8GHz,其他速率需要的時鐘如表1所示。

GDDR6控制器IP支持兩個通道,每個通道為16bit位寬。兩個通道獨立訪問不同的GDDR6空間。控制器的用戶接口為標準的AXI協(xié)議,可以連接到二維片上網絡上或者直接連到內部的可編程邏輯。在另外一邊,控制器和PHY的接口為DFI4.0接口。

表1 GDDR6支持的時鐘頻率模式

PHY IP用來連接器件外圍的高速GDDR6顆粒,它會像其他DRAM PHY一樣產生PRECHARGE、ACTIVE和REFRESH等命令。

APB全稱Advanced Peripheral Bus,字面上是先進外圍總線的意思,該總線協(xié)議是ARM公司提出的AMBA總線結構之一,已成為一種標準的片上總線結構。APB總線接口工作在250MHz,用來配置GDDR6子系統(tǒng)的寄存器,Speedster7t FPGA的配置電路FCU可以在啟動的時候通過APB總線接口配置GDDR6子系統(tǒng)的寄存器,用戶邏輯模塊也可以在FPGA運行的時候通過APB總線接口動態(tài)配置GDDR6子系統(tǒng)的寄存器。

4. GDDR6控制器結構

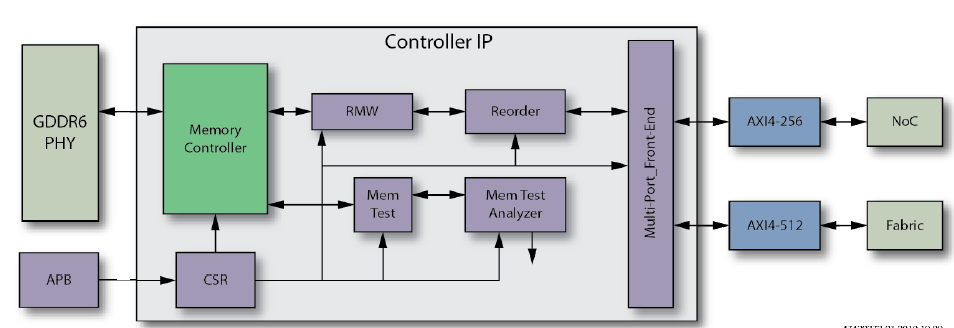

GDDR6控制器模塊的詳細結構如圖3所示。它包括主控部分和其他的一些子模塊,比如Multi-port front-end模塊,Reorder模塊,Read modify Write模塊,內存測試模塊和內存測試分析模塊。

MPFE模塊是前端多端口模塊,Speedster7t上的GDDR6控制器為每個通道提供了兩個MPFE端口,它們支持AXI4協(xié)議,每個端口能夠提供最大256Gbps的帶寬;其中一個AXI端口用于連接到二維片上網絡上,位寬為256位,時鐘是1GHz。另一個AXI端口用于直接連接到FPGA內部的可編程邏輯資源,位寬為512位,時鐘是500MHz。

Reorder模塊用來調整發(fā)給GDDR6控制器的用戶請求的順序。Reorder模塊里有一個深度為64的隊列,用于緩存用戶請求,只要隊列不滿就可以接收新的用戶請求。在接收到用戶請求以后,Reorder模塊可以調整用戶請求的順序,進而可以大大提高DRAM的訪問效率。用戶可以通過設置不同的參數來調整reorder的標準,同時這個模塊也可以bypass掉,維持用戶請求的原來順序。

RMW模塊是讀-修改-寫的模塊,先讀出內存中的數據內容,然后修改單個或者多個bit以后再整體寫回。有了這個模塊,GDDR6控制器支持將地址mask的功能。

Mem Test和Mem Test Analyzer是用于內存測試的模塊,Mem Test內存測試模塊支持生成不同的數據類型去寫入GDDR6;Mem Test Analyzer內存測試分析模塊將讀到的數據與期望的數據進行比較,從而驗證GDDR6的硬件接口和讀寫功能是否正常。

圖3 Speedster7t GDDR6控制器框圖

GDDR6控制器支持兩種模式,正常x16模式和Clamshell x8模式。在x16模式下,控制器提供了每通道16位的雙通道接口,可以連接一個GDDR6顆粒。在Clamshell x8模式下,如圖4所示,控制器提供了每通道8位的雙通道接口,可以連接兩個GDDR6顆粒。Clamshell模式提供了一種在不改變控制器帶寬的情況下,通過在兩個GDDR6顆粒間share地址和命令總線將容量加倍的一種方法。

圖4 GDDR6 Clamshell模式

后面我們還會繼續(xù)深入了解Speedster 7t FPGA上的一些其他特性,以及這些特性如何運用在數據加速和網絡加速應用中,敬請期待。如需更多信息或者有任何疑問您可以通過Achronix公眾號里聯(lián)系方式聯(lián)系我們,也可訪問Achronix公司官方網站https://www.achronix.com

參考文獻:

1.Micron 8Gb/16Gb GDDR6 Product Brief

2.Achronix website www.achronix.com