還剩三天,,被半導(dǎo)體產(chǎn)業(yè)奉為圭臬的“摩爾定律”就將邁入第57個(gè)年頭,,同時(shí),它也將進(jìn)入“將死”的又一年,。自1965年,,摩爾定律首次被提出來以后,全球芯片技術(shù)基本都是在這原理下運(yùn)行,,它見證了人類信息技術(shù)前進(jìn)的腳步,。

回顧過去,從本世紀(jì)初開始,,就不斷有業(yè)界大佬預(yù)測(cè)摩爾定律“將死”,。2004年國(guó)際半導(dǎo)體技術(shù)發(fā)展路線圖(ITRS)修訂版就預(yù)測(cè),摩爾定律這種線性發(fā)展可能繼續(xù)保持10-15年,。

2013年,,美國(guó)國(guó)防部先進(jìn)研究項(xiàng)目局認(rèn)為,2020年,、7納米將是芯片的最后制程節(jié)點(diǎn),。其微系統(tǒng)技術(shù)辦公室主管羅伯特-克羅韋爾表示,預(yù)計(jì)芯片產(chǎn)業(yè)會(huì)花大工夫推進(jìn)5納米制程,,這會(huì)將摩爾定律最初的終結(jié)時(shí)間推遲到2022年,。2015年,博通首席技術(shù)官Henry Samueli表示:“摩爾定律已經(jīng)頭發(fā)花白,,步履蹣跚了,。它還沒死,但是時(shí)候退休了,?!?/p>

在“摩爾定律將死”的無形之劍下,全球半導(dǎo)體產(chǎn)業(yè)經(jīng)歷了一年又一年,到如今芯片制程節(jié)點(diǎn)已經(jīng)沖刺3nm,。而全球研究人員也“頭頂懸劍”,,不斷地開拓新材料、新晶體管,、新設(shè)備等領(lǐng)域,,以此來迎接未來芯片的挑戰(zhàn)。

二維材料有望變革傳統(tǒng)集成電路架構(gòu)

眾所周知,,晶圓的原始材料是硅,,硅作為一種半導(dǎo)體可以通過引入少量雜質(zhì)的方法,調(diào)節(jié)為良好的導(dǎo)體或者絕緣體,。然而,,隨著近年來集成電路的制程進(jìn)入5nm以下,晶體管的尺寸不斷縮小逼近其物理極限,,傳統(tǒng)的硅基材料越來越難以支撐集成電路性能的進(jìn)一步發(fā)展,。

二維材料是一種從2004年發(fā)展起來的新材料,以過渡金屬硫族化合物(TMDC)為代表,,包括通式為MX2的過渡金屬二鹵化物(TMD),,其中M為過渡金屬(例如,Mo或W),,X為硫族元素(例如S,、Se或Te)。這種材料具有極限厚度,、高遷移率和后端異質(zhì)集成等特點(diǎn),,將有望變革傳統(tǒng)集成電路的架構(gòu),受到了學(xué)術(shù)界和工業(yè)界的關(guān)注,。

目前,,英特爾、三星,、臺(tái)積電等處于芯片技術(shù)前沿的大廠們都已布局這個(gè)領(lǐng)域,。為了應(yīng)對(duì)未來芯片危機(jī),歐洲也致力于石墨烯等二維材料研發(fā),。此外,,我國(guó)北京大學(xué),、南京大學(xué)等也在這個(gè)領(lǐng)域取得了技術(shù)突破,。

英特爾-- MoS2解決傳統(tǒng)硅芯片的物理限制

近日,在2021 IEEE國(guó)際電子器件會(huì)議(IEDM)上,,英特爾公布了突破摩爾定律的三種新技術(shù),,這些技術(shù)的目標(biāo)是在2025年之后還能使芯片技術(shù)繼續(xù)發(fā)展,而其中就提及了二維材料。

據(jù)了解,,英特爾提出用一種叫做TMD(過渡金屬硫化物)的二維材料代替硅成為電流通道,,特點(diǎn)是在通道下面,有一層非常薄的,,單層的二硫化物原子層,,可以作為更短的通道。

英特爾制造,、供應(yīng)鏈和營(yíng)運(yùn)集團(tuán)副總裁,、戰(zhàn)略規(guī)劃部聯(lián)席總經(jīng)理盧東暉指出,“硅的問題是無法繼續(xù)往下縮,,再往下縮會(huì)出現(xiàn)很多量子效應(yīng),,但二維材料有自己本身的特質(zhì),所以可以做得非常小,?!庇⑻貭栐诓牧仙献畲蟮耐黄剖怯脙煞N不同的金屬去做金屬接觸,NMOS用的是銻,,PMOS用的是釕,,這樣能讓電容更小。

英特爾表示將單層二硫化鉬MoS?應(yīng)用于硅芯片連接層可以使得間距從15nm縮小至5nm,,解決傳統(tǒng)硅芯片的物理限制,。

臺(tái)積電--- MoS2結(jié)合鉍實(shí)現(xiàn)極低接觸電阻

而臺(tái)積電則是聯(lián)手臺(tái)灣大學(xué)、美國(guó)麻省理工學(xué)院發(fā)現(xiàn)了二維材料結(jié)合半金屬鉍可以實(shí)現(xiàn)極低的接觸電阻,,接近量子極限,,這一研究發(fā)現(xiàn)于今年5月發(fā)表于自然期刊。

據(jù)了解,,受到高電阻與低電流的限制,,石墨烯等二維材料一直無法取代硅基半導(dǎo)體。麻省理工團(tuán)隊(duì)首先發(fā)現(xiàn)二硫化鉬(MoS2)與半金屬鉍結(jié)合可以有效降低電阻,,提升電流的傳輸效率,。臺(tái)積電技術(shù)研究部門隨后對(duì)鉍沉積制程進(jìn)行了優(yōu)化,最后臺(tái)大團(tuán)隊(duì)利用氦離子束微影系統(tǒng)將元件通道成功縮小至納米級(jí),,才得出這一研究成果,。

早在去年3月,臺(tái)積電就曾與臺(tái)灣交通大學(xué)聯(lián)合研制的最薄氮化硼二維絕緣材料,,該材料厚度僅為0.7nm,,可以用于1nm制程的突破。

三星--發(fā)現(xiàn)新材料“非晶態(tài)氮化硼”

去年7月,,三星電子技術(shù)學(xué)院表示,,他們與蔚山科技學(xué)院合作,,成功發(fā)現(xiàn)了新材料“非晶氮化硼(a-BN)”。據(jù)介紹,,研究小組不僅確保了世界上最低1.78的介電常數(shù),,而且還證明了該材料可以在400°C環(huán)境下,在半導(dǎo)體基板上大面積生成,,從而朝著工藝創(chuàng)新邁出了一步,。非晶氮化硼可應(yīng)用于包括存儲(chǔ)器半導(dǎo)體(DRAM、NAND等)的半導(dǎo)體系統(tǒng),,并且有望用于要求高性能的服務(wù)器用內(nèi)存半導(dǎo)體,。

其實(shí)三星對(duì)二維材料的研究已進(jìn)行了多年。2012年,,三星使用石墨烯開發(fā)新的晶體管結(jié)構(gòu),;2014年,三星解決了石墨烯半導(dǎo)體晶片上無法生成的限制,,在晶片上形成了世界上第一層純石墨烯層,,并開發(fā)了用于大規(guī)模生產(chǎn)的源技術(shù);2017年:三星擺脫現(xiàn)有石墨烯的規(guī)則六邊形網(wǎng)格結(jié)構(gòu),,碳原子以無規(guī)形式連接的石墨烯結(jié)構(gòu)開發(fā),,大面積成功合成。

歐盟----致力二維材料研發(fā)

為了應(yīng)對(duì)未來芯片危機(jī),,歐洲也致力于石墨烯等二維材料研發(fā),。早在2013年,歐盟就投資了10億歐元,,以推動(dòng)之后10年內(nèi)的石墨烯技術(shù)發(fā)展,。最近一年來,石墨烯材料的3條試驗(yàn)生產(chǎn)線已經(jīng)投入運(yùn)行,。

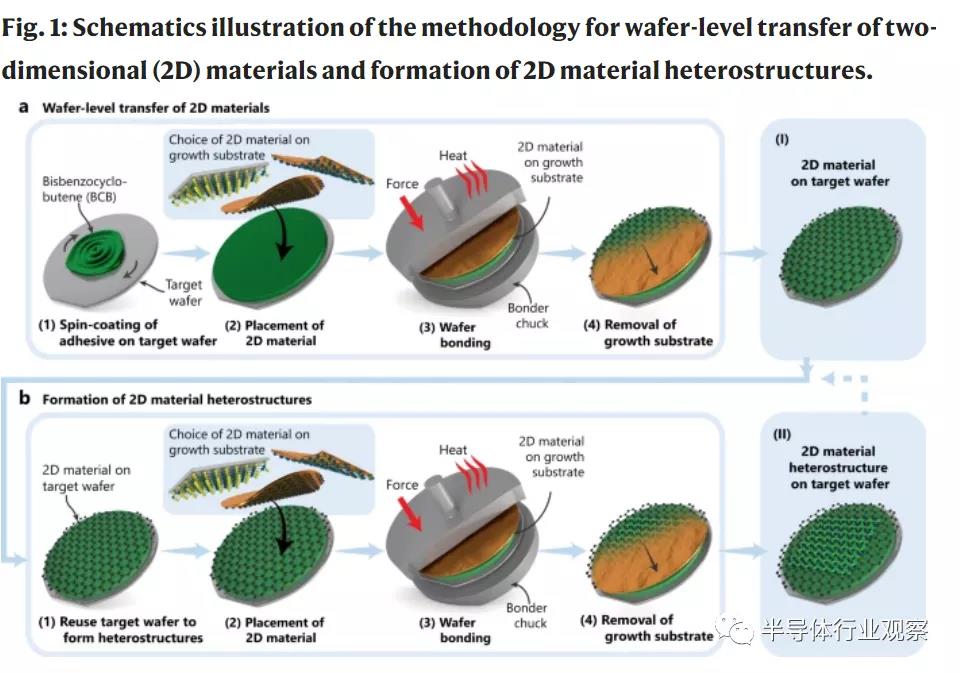

今年年初,,歐盟“石墨烯旗艦計(jì)劃”的一項(xiàng)最新實(shí)驗(yàn),提出了一種將石墨烯和2D材料集成到半導(dǎo)體生產(chǎn)線的新方法,,并發(fā)表在《自然·通訊》上,。

圖片來源:nature

研究人員采用直徑100mm的銅箔作為化學(xué)氣相沉積(CVD)制單層石墨烯的生長(zhǎng)基底、采用直徑為1cm的帶氧化層硅片(SiO2/Si)作為二硫化鉬的生長(zhǎng)基底,,并將這兩種材料轉(zhuǎn)移至直徑100mm的硅基底上,,提升二維材料轉(zhuǎn)移成功率。

北京大學(xué)—實(shí)現(xiàn)2英寸單層單晶WS2的外延制備

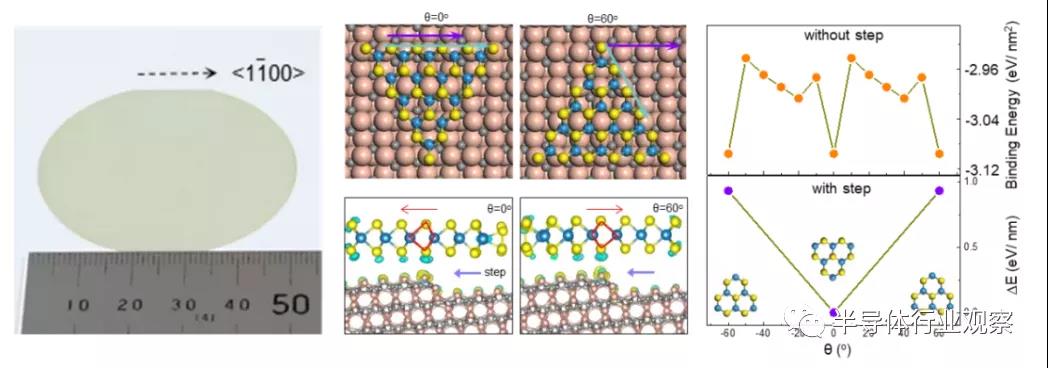

11月15日,,松山湖材料實(shí)驗(yàn)室/北京大學(xué)劉開輝研究員,、王恩哥院士團(tuán)隊(duì)與合作者,在Nature Nanotechnology上發(fā)表了題為“Dual-coupling-guided epitaxial growth of wafer-scale single-crystal WS2 monolayer on vicinal a-plane sapphire”的研究論文,,首次提出“雙耦合協(xié)同調(diào)控”的全新生長(zhǎng)機(jī)理,,成功在藍(lán)寶石襯底上實(shí)現(xiàn)了2英寸單層單晶二硫化鎢(WS2)制備,。

圖片來源:松山湖材料實(shí)驗(yàn)室

研究團(tuán)隊(duì)經(jīng)過深入探索,,提出二維材料與絕緣襯底面內(nèi)范德華耦合作用和臺(tái)階相互作用的“雙耦合協(xié)同調(diào)控”新機(jī)理,,實(shí)現(xiàn)了2英寸單層單晶WS2的外延制備?!半p耦合協(xié)同調(diào)控”機(jī)理的關(guān)鍵物理思想在于:WS2和藍(lán)寶石襯底間的范德華相互作用將WS2晶疇的優(yōu)勢(shì)取向限制為0°與180°,;WS2和藍(lán)寶石臺(tái)階間的相互作用可以打破2個(gè)取向的能量簡(jiǎn)并性,從而使WS2晶疇只保留1個(gè)優(yōu)勢(shì)取向,。

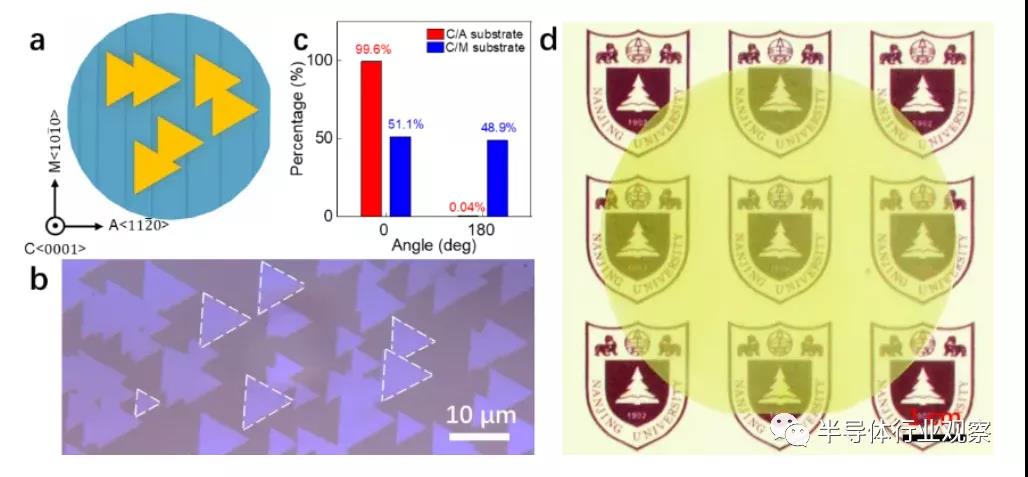

南京大學(xué)----實(shí)現(xiàn)2英寸MoS2單晶薄膜外延生長(zhǎng)

南京大學(xué)電子科學(xué)與工程學(xué)院王欣然教授課題組通過改變藍(lán)寶石表面原子臺(tái)階的方向,,人工構(gòu)筑了原子尺度的“梯田”。利用“原子梯田”的定向誘導(dǎo)成核機(jī)制,,實(shí)現(xiàn)了TMDC的定向生長(zhǎng),。基于此原理,,團(tuán)隊(duì)在國(guó)際上首次實(shí)現(xiàn)了2英寸MoS2單晶薄膜的外延生長(zhǎng),。

圖片來源:南京大學(xué)

得益于材料質(zhì)量的提升,基于MoS2單晶制備的場(chǎng)效應(yīng)晶體管遷移率高達(dá)102.6 cm2/Vs,,電流密度達(dá)到450 μA/μm,,是國(guó)際上報(bào)道的最高綜合性能之一。同時(shí),,該技術(shù)具有良好的普適性,,適用于MoSe2等其他材料的單晶制備,該工作為TMDC在集成電路領(lǐng)域的應(yīng)用奠定了材料基礎(chǔ),。

晶體管結(jié)構(gòu)新變革

隨著工藝一步步演進(jìn),,晶體管的尺寸也在一點(diǎn)點(diǎn)縮小,以便在給定的芯片面積內(nèi)集成更多的電子元件,,從而帶來更強(qiáng)的系統(tǒng)功能和更低的指數(shù)級(jí)成本,。但如今,“摩爾定律”即將迎來其57“大壽”,,芯片制程也邁入了后FinFET時(shí)代,,可以塞進(jìn)單個(gè)芯片的晶體管數(shù)量幾乎達(dá)到了極限。毋庸置疑,,除了新材料外,,晶體管結(jié)構(gòu)也將迎來新變革。

GAA

在上述英特爾公布的突破摩爾定律三種新技術(shù)中,,晶體管微縮面積的提升也是其中之一,。據(jù)悉,英特爾將采用GAA RibbonFET(Gate-All-Around RibbonFET)技術(shù),,通過堆疊多個(gè)(CMOS)晶體管,,實(shí)現(xiàn)高達(dá)30%至50%的邏輯微縮提升,,單位面積的晶體管數(shù)量越多,半導(dǎo)體的性能也就越強(qiáng)大,。RibbonFET是英特爾對(duì)于GAA晶體管的實(shí)現(xiàn),,也是公司自2011年率先推出FinFET以來的首個(gè)全新晶體管架構(gòu)。

與FinFET的不同之處在于,,GAA設(shè)計(jì)通道的四個(gè)面周圍有柵極,,可減少漏電壓并改善對(duì)通道的控制,這是縮小工藝節(jié)點(diǎn)時(shí)的關(guān)鍵,。三星此前也宣布將GAA用于3nm工藝,,預(yù)計(jì)于2022年投產(chǎn)。此外,,臺(tái)積電董事長(zhǎng)劉德音也曾指出,,在2nm之后,臺(tái)積電將轉(zhuǎn)向采用GAA的架構(gòu),,提供比FinFET架構(gòu)更多的靜電控制,,改善芯片整體功耗。

VTFET

在2021 IEDM上,,IBM和三星公布了一種在芯片上垂直堆疊晶體管的新設(shè)計(jì),,即VTFET。VTFET(垂直傳輸場(chǎng)效應(yīng)晶體管)將晶體管垂直于硅晶圓,,并引導(dǎo)電流垂直于硅片表面,。這種新方法通過打破對(duì)晶體管柵極長(zhǎng)度、間隔厚度(spacer thickness)和觸點(diǎn)尺寸的物理限制來解決縮放障礙,,以便優(yōu)化包括性能和功耗在內(nèi)的各種參數(shù),。

根據(jù)IBM和三星的說法,這種設(shè)計(jì)有兩個(gè)優(yōu)點(diǎn),。首先,,它將使他們能夠繞過許多性能限制,使摩爾定律超越IBM目前的納米片技術(shù),。更重要的是,,由于更大的電流流動(dòng),這種設(shè)計(jì)導(dǎo)致了更少的能量浪費(fèi),。他們估計(jì),,VTFET將使處理器的速度比使用FinFET晶體管設(shè)計(jì)的芯片快一倍,或減少85%的功率,。

待VTFET技術(shù)成熟,,已宣布采用GAA技術(shù)的三星,未來是否會(huì)將VTFET用于先進(jìn)制程,,我們也拭目以待,。

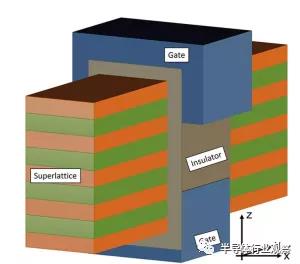

CasFET

CasFET是由普渡大學(xué)工程師推出的新型晶體管,,具有垂直于晶體管傳輸方向的超晶格結(jié)構(gòu),它們的行為類似于量子級(jí)聯(lián)激光器,,而不是傳統(tǒng)的 FET 器件,,從而讓晶體管實(shí)現(xiàn)開關(guān)電壓更低、功耗更低,、設(shè)計(jì)更密集,,體積更小,。

圖片來源:普渡大學(xué)

普渡大學(xué)電氣和計(jì)算機(jī)工程助理教授蒂爾曼·庫比斯(Tillmann Kubis)指出,,“模擬量子級(jí)聯(lián)激光器通過外部電場(chǎng)轉(zhuǎn)換其傳輸性質(zhì),從相干/彈道傳輸?shù)街鸩胶吐曌虞o助隧道傳輸,。這種開關(guān)效應(yīng)是我們添加到 FET 的”標(biāo)準(zhǔn)“場(chǎng)效應(yīng)開關(guān)中的,。

此外,他還補(bǔ)充道,,”與最先進(jìn)的晶體管相比,,CasFET對(duì)柵極更敏感,這也適用于柵極全能 FET,。所有這些晶體管都依賴于單一的開關(guān)機(jī)制,。我們的有兩個(gè)?!澳壳霸?CasFET 設(shè)備還在設(shè)計(jì)中,。

下一代EUV光刻機(jī)也要做好準(zhǔn)備

提到未來芯片工藝制程,光刻機(jī)顯然是必不可缺的話題,,可以說,,制程突破在一定程度上受制于光刻機(jī)。光刻的本質(zhì)其實(shí)是一個(gè)投影系統(tǒng),,光線被投射通過掩模版,,成像在晶圓上,最終在晶圓上一層一層建立起復(fù)雜的晶體管,。隨著光刻技術(shù)不斷朝著”更小“征程邁進(jìn),,下一代光刻機(jī)也需要做好充足的準(zhǔn)備。

High-NA EUV

為了避免 EUV 雙重圖案化,,High-NA EUV成為了焦點(diǎn),,其可以實(shí)現(xiàn)更簡(jiǎn)單的單圖案方法。光刻機(jī)巨頭ASML 將通過重新設(shè)計(jì)光刻系統(tǒng)內(nèi)的光學(xué)器件,,從目前的 0.33 NA 變?yōu)?0.55NA(即 NA 增加 67%),。0.55NA EUV 光刻有望最終實(shí)現(xiàn) 8nm 分辨率,對(duì)應(yīng)于一次曝光中 16nm 間距的印刷線/間距,。

根據(jù)ASML 的10月分享報(bào)告顯示,,其最新的 EUV 光刻機(jī)可以在未來 10 年左右的時(shí)間內(nèi)幫助制造商在硅基板上塞入越來越多的晶體管,。根據(jù)ASML預(yù)測(cè),在2030年,,將會(huì)有集成3000億晶體管的芯片出現(xiàn),。

ASML報(bào)告指出,從 2023 年開始,,ASML計(jì)劃交付第一批下一代 EUV 設(shè)備,,該設(shè)備將從 0.33 NA 到 0.55 NA,使 EUV 數(shù)值孔徑 (NA) 高于當(dāng)前機(jī)器的能力,。而這可以讓芯片制造商開發(fā)出遠(yuǎn)遠(yuǎn)超過當(dāng)前預(yù)期的 2 nm閾值的工藝節(jié)點(diǎn),,并且在對(duì)高級(jí)晶圓層使用單次曝光 EUV 工藝時(shí)還可以節(jié)省一些成本。

EUV 光刻膠

未來工藝節(jié)點(diǎn)向high NA光刻的過渡不僅需要來自ASML等系統(tǒng)供應(yīng)商的工程創(chuàng)新,,還需要對(duì)合適的光刻膠材料進(jìn)行高級(jí)開發(fā),,不斷提高光刻膠的性能。

Lam Research 將使用化學(xué)氣相沉積工藝在金屬光刻膠上分層,,而不是濕式光刻膠(wet photoresist )技術(shù),。Lam Research 干式抗蝕劑技術(shù)的最大優(yōu)勢(shì)之一是使用化學(xué)氣相沉積 (CVD) 工藝來沉積光刻膠,從而可以更精細(xì)地控制光刻膠的可變性和厚度,。

東京電子發(fā)現(xiàn)了一種新的溶劑沖洗工藝,,可以將生產(chǎn)線擴(kuò)展到 ~24nm(12nm 臨界尺寸)。這個(gè)工藝或?qū)⒃试S濕抗蝕劑方法縮放到 24 nm,。

TokyoElectron 和 JSR 聲稱他們有一種新的金屬氧化物抗蝕劑曝光后烘烤工藝,,這將有助于提高光刻膠的靈敏度。

新掩膜類型

除了光刻膠外,,High-NA EUV 還需要新的光掩模類型,。為了減少不必要的圖案放置偏移產(chǎn)生的影響,EUV 掩模需要更薄的吸收劑,。當(dāng)前EUV 掩模中,,鉭吸收劑的厚度為 60nm,雖然它可以做得更薄,,但被限制在50nm,,并不能解決掩膜效應(yīng)。為此,,業(yè)界正在開發(fā)幾種新的 EUV 掩模類型,,例如 2D、無吸收體,、高 k,、非反射和 PSM。

在 SPIE Photomask/EUV 會(huì)議上的演講中,漢陽大學(xué)的研究人員描述了一種相移 EUV 掩模,,它由基板上的釕和硅交替層組成,。釕覆蓋層位于多層結(jié)構(gòu)的頂部,然后是鉭-硼蝕刻停止層,,以及作為相移材料的釕合金,。

High k 掩模在研發(fā)中,業(yè)內(nèi)正在探索鎳等其他材料替代鉭吸收劑,。據(jù)了解,,更薄的鎳吸收劑可以減輕掩模效應(yīng),但同時(shí)也很難使用,。

此外,,初創(chuàng)公司 Astrileux 也描述了一種使用釕材料的新型非反射 EUV 掩模。這家公司還表示,,2D 掩膜等都在研發(fā)中,。

寫在最后

技術(shù)或許有極限,,但人類的智慧沒有極限,。”摩爾定律“何時(shí)會(huì)死去,,沒人會(huì)知道,,但隨著研發(fā)人員不斷地探索,或許它將會(huì)被源源不斷地”續(xù)命“,,未來芯片危機(jī)也或許會(huì)在某一天伴隨著某個(gè)新技術(shù)的誕生迎刃而解,。

最后引用硅谷王川在《為什么摩爾定律一直沒死, 但人們還會(huì)繼續(xù)預(yù)測(cè)摩爾定律要死》中的一段話,,”就是更多錢,,更多人,更好的工具,,更快的通訊,,多個(gè)提高晶體管密度的解決方案齊頭并進(jìn),這些解決方案中冒頭的最佳方案,,肯定會(huì)不斷超越以前的解決方案的效率,。但是在那個(gè)贏家冒頭之前,我們很難提前預(yù)測(cè)哪個(gè)方案會(huì)勝出,?!?/p>