簡(jiǎn)介

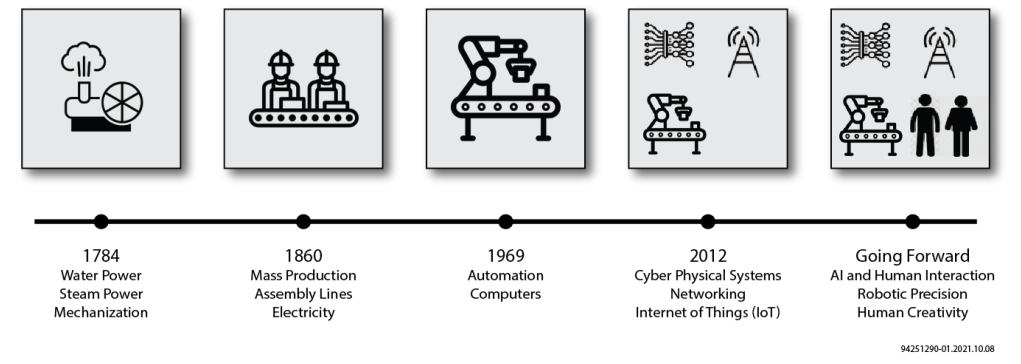

在過(guò)去三百年間,工業(yè)領(lǐng)域取得了長(zhǎng)足的進(jìn)步。機(jī)器設(shè)備最初于18世紀(jì)問(wèn)世,主要以水和蒸汽為動(dòng)力,并引發(fā)了18世紀(jì)末的工業(yè)革命(通常被稱(chēng)為工業(yè)1.0)。盡管流水組裝線的概念可以追溯到中國(guó)古代的青花瓷制作,但直到19世紀(jì)末,亨利·福特才設(shè)立了第一條電動(dòng)流水線,形成了工業(yè)2.0的框架。

自動(dòng)化和計(jì)算機(jī)技術(shù)于1960年代末期開(kāi)始嶄露頭角,并構(gòu)成了工業(yè)3.0的雛形,為如今驅(qū)動(dòng)著工業(yè)4.0的自動(dòng)化、人工智能(AI)和網(wǎng)絡(luò)化解決方案鋪平了道路。雖然這幅圖景中似乎已經(jīng)看不見(jiàn)人類(lèi)的身影,但工業(yè)5.0將帶領(lǐng)我們返璞歸真,利用AI驅(qū)動(dòng)的機(jī)器人系統(tǒng)所具有的精準(zhǔn)和高效,與人類(lèi)大腦的奇思妙想和實(shí)時(shí)思考有機(jī)結(jié)合,創(chuàng)造出更理想的制造環(huán)境。

圖1:工業(yè)技術(shù)的演進(jìn)

人工智能

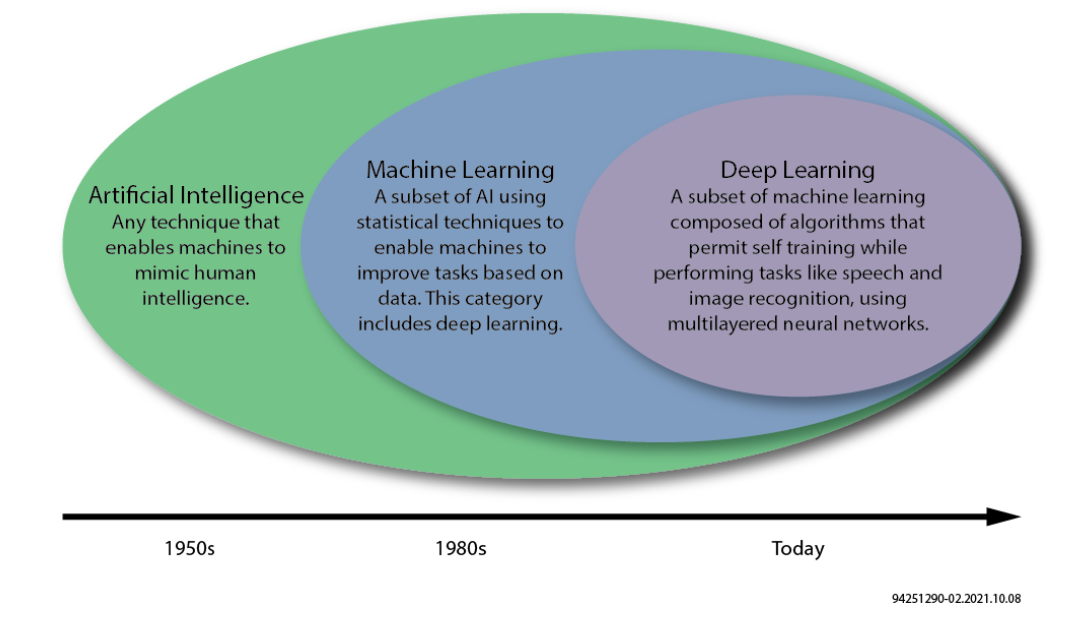

人工智能(AI)是計(jì)算機(jī)科學(xué)的一個(gè)分支,主要專(zhuān)注于開(kāi)發(fā)能夠模擬人類(lèi)行為的機(jī)器。這類(lèi)設(shè)備的范疇林林總總,從可以簡(jiǎn)單地執(zhí)行算法,到可以自主從周邊環(huán)境中學(xué)習(xí)、無(wú)需人類(lèi)介入便自行調(diào)節(jié)算法。機(jī)器學(xué)習(xí)(ML)是人工智能的子集,它通過(guò)運(yùn)用數(shù)據(jù)集衍生的統(tǒng)計(jì)模型來(lái)改進(jìn)特定任務(wù)。作為機(jī)器學(xué)習(xí)的子集,深度學(xué)習(xí)(DL)運(yùn)用了多層神經(jīng)網(wǎng)絡(luò),不僅能執(zhí)行基礎(chǔ)的機(jī)器學(xué)習(xí)推理,還能學(xué)習(xí)新的數(shù)據(jù),從而獲得更高層的認(rèn)知能力(見(jiàn)下圖)。在本篇白皮書(shū)中,所有機(jī)器學(xué)習(xí)和深度學(xué)習(xí)都將被簡(jiǎn)稱(chēng)為ML。

圖2:人工智能/機(jī)器學(xué)習(xí)/深度學(xué)習(xí)譜圖

人工智能(AI)的常見(jiàn)用例包括先進(jìn)駕駛輔助系統(tǒng)(ADAS),即自動(dòng)駕駛汽車(chē)的支柱;語(yǔ)音識(shí)別及合成(例如華為的Celia);醫(yī)療診斷;數(shù)據(jù)與網(wǎng)絡(luò)安全;金融服務(wù)預(yù)測(cè)性模型(例如電子化交易),或電商與流媒體服務(wù)推薦;當(dāng)然還有工業(yè)制造。

隨著工業(yè)4.0在2010年代早期進(jìn)一步演進(jìn),使得AI在制造環(huán)境中的重要性與日俱增。如今,許多應(yīng)用都會(huì)利用AI來(lái)促進(jìn)制造和業(yè)務(wù)經(jīng)營(yíng)、流程、安保和供應(yīng)鏈等更加流暢高效。通過(guò)運(yùn)用預(yù)測(cè)性算法,AI可以監(jiān)控設(shè)備狀況,優(yōu)化維護(hù)日程,最終還能預(yù)報(bào)機(jī)械故障。

與制造相關(guān)的物料供應(yīng)鏈管理也可以充分發(fā)揮預(yù)測(cè)算法的優(yōu)勢(shì),保障流程能夠順利、高效地持續(xù)運(yùn)作。AI算法還可以參考過(guò)往和現(xiàn)在的商業(yè)需求,從而協(xié)助預(yù)測(cè)未來(lái)的業(yè)務(wù)。這些AI系統(tǒng)可以與供應(yīng)鏈和庫(kù)存管理系統(tǒng)結(jié)合,加快獲利時(shí)效,降低間接成本。機(jī)器人早在工業(yè)3.0就成為了其中重要的組成部分。而在我們即將迎來(lái)工業(yè)5.0之際,這些機(jī)器人系統(tǒng)必須擁有適應(yīng)性的AI算法(主要為DL算法)。它們不僅需要自主學(xué)習(xí),還必需能夠解讀人類(lèi)的實(shí)時(shí)輸入。低時(shí)延的實(shí)時(shí)適應(yīng)能力也將成為不可或缺的要素。

AI之外的生態(tài)系統(tǒng)組件

在持續(xù)興旺發(fā)展的工業(yè)4.0和正在演進(jìn)的工業(yè)5.0中,AI依然是一個(gè)重要的組成部分。然而,AI算法的蓬勃發(fā)展離不開(kāi)實(shí)時(shí)數(shù)據(jù)。物聯(lián)網(wǎng)(IoT)是由互聯(lián)的電子設(shè)備組成的系統(tǒng),可以從模擬和數(shù)字世界中獲取與接收數(shù)據(jù)。時(shí)間、壓力、溫度、速度、角度及視聽(tīng)數(shù)據(jù)源必須經(jīng)過(guò)采集,隨后轉(zhuǎn)換成結(jié)構(gòu)化數(shù)據(jù),各類(lèi)基于AI的系統(tǒng)才能對(duì)其進(jìn)行分析和控制。和4G網(wǎng)絡(luò)相比,自2019年起部署的5G網(wǎng)絡(luò)(在韓國(guó)率先部署)可提供100倍的帶寬(最高可達(dá)10 Gbps)和500倍的信道數(shù)量。5G網(wǎng)絡(luò)與IoT結(jié)合之后,海量的輸入數(shù)據(jù)在計(jì)算機(jī)領(lǐng)域中引出了一種新范式,即對(duì)數(shù)據(jù)加速器的需求。

數(shù)據(jù)加速器

在海量的數(shù)據(jù)面前,數(shù)據(jù)中心處理數(shù)據(jù)的負(fù)擔(dān)以及發(fā)現(xiàn)數(shù)據(jù)背后的意義這些工作,已經(jīng)令傳統(tǒng)的計(jì)算服務(wù)器模式不堪重負(fù)。過(guò)去應(yīng)對(duì)數(shù)據(jù)激增的方法就是在數(shù)據(jù)中心增添服務(wù)器。服務(wù)器安裝規(guī)模的提升不僅提高了資本性支出,再加上設(shè)備的運(yùn)行和冷卻需要消耗更多能源,營(yíng)運(yùn)性支出也隨之水漲船高。

取決于數(shù)據(jù)加速器的類(lèi)型與負(fù)載,服務(wù)器中單個(gè)數(shù)據(jù)加速器的運(yùn)算能力可以與15臺(tái)服務(wù)器匹敵,從而大幅削減了資本性支出和營(yíng)運(yùn)性支出。基于硬件的數(shù)據(jù)加速器還帶來(lái)了更多效益,例如較低的時(shí)延和更高的穩(wěn)定性,這在車(chē)輛自動(dòng)駕駛、工業(yè)4.0/5.0、金融服務(wù)和其他對(duì)時(shí)延要求較高的用例中效果尤為突出。優(yōu)秀的數(shù)據(jù)加速器還有最后一項(xiàng)特征,它具備了出色的靈活性,能夠適應(yīng)ML/DL算法的變化,包括算法本身的調(diào)整、負(fù)載的變化和/或ML/DL算法數(shù)據(jù)集的更新。

數(shù)據(jù)加速的賽場(chǎng)上有三種各異的硬件方式,即GPU、FPGA和定制ASIC。如下圖所示。CPU的靈活性始終是最出色的,但與其他專(zhuān)用數(shù)據(jù)加速器相比,在能耗、性能和成本方面存在一定的劣勢(shì)。其它選項(xiàng)便是GPU、ASIC和FPGA。ASIC的效率與性能最為出色,但功能完全固定,缺乏必需的靈活性,無(wú)法適應(yīng)AI算法的變化、新興技術(shù)的參數(shù)改動(dòng)、供應(yīng)商要求和負(fù)載優(yōu)化。GPU是傳統(tǒng)核心數(shù)據(jù)中心的主力,僅限于純粹運(yùn)算這樣的使用場(chǎng)景,而不能提供大多數(shù)場(chǎng)景中需要利用到的聯(lián)網(wǎng)與存儲(chǔ)加速的能力,并且能耗和成本較高。FPGA可以加速聯(lián)網(wǎng)、運(yùn)算和存儲(chǔ),速度與ASIC相仿,也具備了必需的靈活性,能夠?yàn)槿缃竦暮诵呐c邊緣數(shù)據(jù)中心提供理想的數(shù)據(jù)加速。除了數(shù)據(jù)加速之外,F(xiàn)PGA還將在傳感器融合和傳入數(shù)據(jù)流合并等領(lǐng)域發(fā)揮關(guān)鍵作用,為數(shù)據(jù)消費(fèi)打下了堅(jiān)實(shí)的基礎(chǔ)。

圖3:CPU、GPU、FPGA和ASIC的對(duì)比

Achronix提供的精選產(chǎn)品

Achronix為AI/ML運(yùn)算、聯(lián)網(wǎng)和存儲(chǔ)應(yīng)用開(kāi)發(fā)了基于FPGA的數(shù)據(jù)加速產(chǎn)品。與其他高性能FPGA企業(yè)不同,Achronix可同時(shí)提供獨(dú)立FPGA芯片和嵌入式FPGA半導(dǎo)體知識(shí)產(chǎn)權(quán)(IP)解決方案。除了獨(dú)立的FPGA芯片和eFPGA IP之外,Achronix還提供基于PCIe的加速卡,可用于開(kāi)發(fā)、實(shí)地測(cè)試或生產(chǎn)等應(yīng)用場(chǎng)景。

采用臺(tái)積電7納米工藝打造的Speedster?7t系列FPGA擁有業(yè)界最快的輸入/輸出速度,可支持400 GbE、PCIe Gen5和雙存儲(chǔ)接口:標(biāo)準(zhǔn)DDR4和GDDR6存儲(chǔ)接口可以帶來(lái)的驚人速度,相較于DDR4提高了600%。如果數(shù)據(jù)無(wú)法輕松通達(dá)FPGA邏輯陣列,高速接口便無(wú)法發(fā)揮太多作用。

為了避免遇到這一瓶頸,Achronix從架構(gòu)增加了二維片上網(wǎng)絡(luò)(2D NoC),能夠有效充當(dāng)所有外部輸入/輸出數(shù)據(jù)的高速通道,增強(qiáng)了FPGA內(nèi)部的功能單元塊和FPGA邏輯陣列本身。這種2D NoC實(shí)現(xiàn)了超過(guò)20 Tbps的雙向帶寬,遠(yuǎn)遠(yuǎn)超過(guò)了輸入/輸出和功能塊的總帶寬需求,消除了片內(nèi)通信的時(shí)延問(wèn)題。

在對(duì)成本、性能與能耗有較高敏感度的大批量應(yīng)用場(chǎng)景中,用戶(hù)通常會(huì)采用ASIC,但這時(shí)又該如何滿(mǎn)足對(duì)靈活性的需求呢?無(wú)論是算法的演變、需求變化、供應(yīng)商和經(jīng)營(yíng)者的具體要求、協(xié)議適配,還是功能系統(tǒng)單元塊的多樣接口,它們都對(duì)靈活性提出了一定程度的要求。

Speedcore? eFPGA IP便是這一問(wèn)題的最終答案,它可令A(yù)SIC能夠具備“恰到好處”的靈活性。其中查找表(LUT)、內(nèi)存、DSP/MLP和2D NoC的資源量與組合方式可由ASIC開(kāi)發(fā)者決定,Achronix則會(huì)為他們的ASIC或SoC設(shè)計(jì)提供集成在芯片上的定制IP。

VectorPath?加速卡是采用PCIe外形結(jié)構(gòu)的硬件加速平臺(tái),可以考慮用作評(píng)估、開(kāi)發(fā)與現(xiàn)場(chǎng)測(cè)試工具,或也可以用于量產(chǎn)應(yīng)用。該解決方案也可以根據(jù)用戶(hù)的具體要求量身定制。

結(jié)語(yǔ)

AI、ML和DL將繼續(xù)推動(dòng)工業(yè)4.0和5.0的發(fā)展,使生產(chǎn)力與效率更上層樓。在IoT和5G技術(shù)的協(xié)助下,自動(dòng)化和機(jī)器人將與人類(lèi)的奇思妙想和創(chuàng)造力融為一體,孕育出人類(lèi)在10年前未曾想象的制造環(huán)境。FPGA促成了傳感器融合,能夠與眾多物聯(lián)網(wǎng)設(shè)備連接,充分把握制造環(huán)境下人工智能系統(tǒng)所需的高性能與靈活性之間的平衡。