國產(chǎn)化IP創(chuàng)新之路(二)創(chuàng)新篇:突破創(chuàng)新及實現(xiàn)數(shù)據(jù)的高效傳輸

2022-02-28

來源:互聯(lián)網(wǎng)

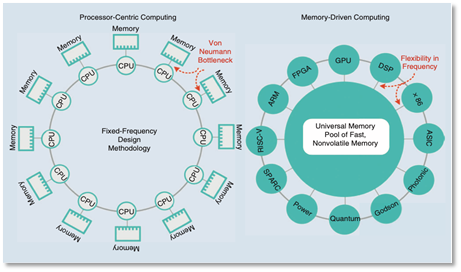

業(yè)界普遍預測未來的計算架構將從以處理器為中心逐漸轉變成以數(shù)據(jù)為中心,內存速度和計算不再是能效瓶頸,數(shù)據(jù)移動的速度正在逐漸成為新的能效瓶頸,本篇文章將詳細介紹后摩爾時代如何通過技術提升來解決瓶頸,實現(xiàn)數(shù)據(jù)的高效傳輸!

從計算為中心到數(shù)據(jù)為中心,急需突破三堵“墻”

算力墻的突破:傳統(tǒng)處理器架構很難突破算力墻,我們需要在處理器架構創(chuàng)新的同時,通過各種DSA異構計算,加上現(xiàn)在普遍看好的Chiplet(芯粒)和先進封裝等技術來突破算力墻。

? 處理器架構創(chuàng)新,多核,并行,片內異構…

? 各種DSA

? Chiplet+先進封裝

內存墻的突破:目前在內存本身往更高密度和更高帶寬的形態(tài)發(fā)展外,可以采用串行內存接口擴展內存,并且基于此做到內存池化,以及利用逐漸成熟的新內存介質來提升內存性能,這些相輔相成,來突破內存墻。

? 更高密度和更高帶寬的內存

? 串行內存接口與內存池化

? 新介質內存

? 近存計算

IO 墻的突破:利用更高速的IO接口,更高效的傳輸協(xié)議以及更低的傳輸延時來突破IO墻。

? 更高速的IO接口

? 更高效的數(shù)據(jù)傳輸協(xié)議,更低的時延

? 在網(wǎng)計算

算力墻:Chiplet與D2D互聯(lián)-后摩爾時代的芯片集成趨勢

由于傳統(tǒng)處理器架構對算力的限制,近年來采用先進封裝和D2D互聯(lián)的Chiplet方案流行,一方面,通過高速低延遲的D2D接口可以對所連接的SOC進行擴展/分割,另一方面,D2D可以靈活有效地實現(xiàn)IO口的聚合和分離,針對不同應用實現(xiàn)性能最優(yōu)解。所以,可以預見,采用高速,低延遲,高性能的先進封裝D2D互聯(lián)chiplet方案正在成為后摩爾時代芯片集成趨勢。

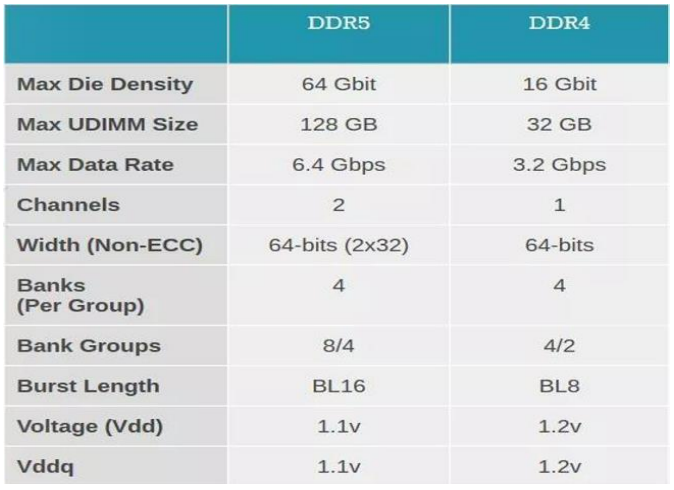

內存墻:DDR5&HBM帶來高帶寬、高容量,將有更廣泛的應用空間

高性能計算,人工智能,以及高性能圖形領域,對內存的帶寬有巨大的要求,因此高帶寬內存 DDR5/HBM在這個領域變得重要起來。目前在數(shù)據(jù)中心和服務器上,DDR4顯得有些吃力,急需更高帶寬更大容量的產(chǎn)品,DDR5應運而生,相比較DDR4,DDR5速率和帶寬均翻倍,在功耗性能上相比于DDR4也做了大量優(yōu)化。隨著Intel和AMD宣布在2022年發(fā)布的下一代處理器上支持DDR5,可以預見,服務器,數(shù)據(jù)中心,和高性能計算等將在2023年大量采用DDR5以滿足其對內存帶寬和容量的需求。

另一種高帶寬內存HBM是用空間換時間,通過堆疊,高互聯(lián)密度,利用較低的頻率來獲得最大帶寬。其最大IO速度可以到達8.4Gbps,最新一代HBM3帶寬已經(jīng)達到驚人的1TB/s。目前除了在一開始的GPU和后來的AI領域被應用外,HBM在CPU領域也逐漸被采用,未來HBM的應用前景將更為廣闊。

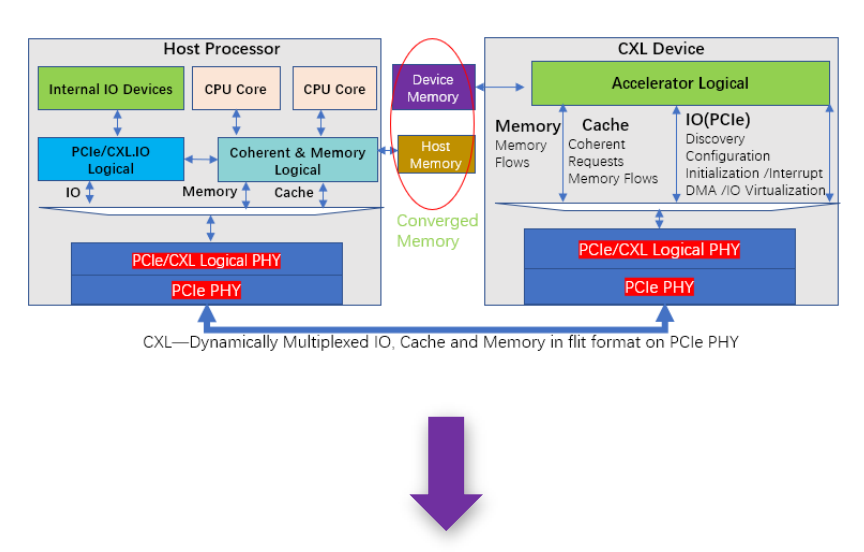

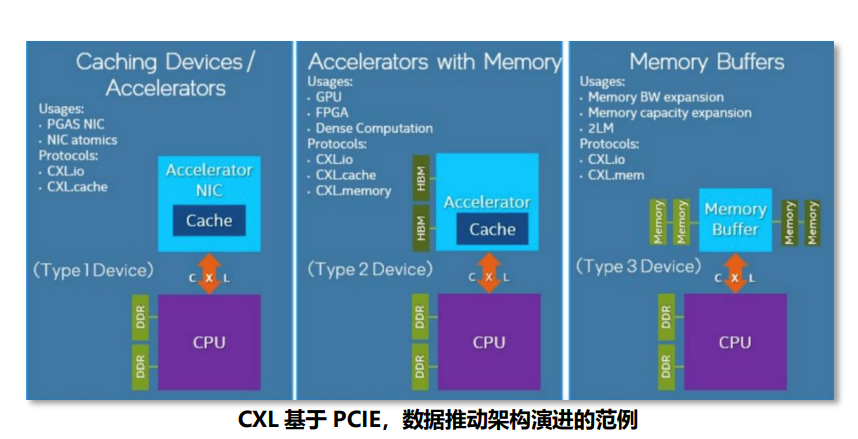

IO墻:基于PCIE的CXL帶來異構計算效率變革

說到計算節(jié)點內數(shù)據(jù)傳輸接口,就不得不提PCIe,自從PCI-SIG組織在2003年推出了PCI-Express之后,計算機內部高速總線迎來了串行時代,當計算需求越來越高時,以太網(wǎng)開始回到摩爾定律的2年帶寬改進周期,但是PCIe卻沒有跟上,成為瓶頸。PCIe 4.0 雖然姍姍來遲,但也滿足了燃眉之急,使得GPU,F(xiàn)PGA等加速器和host之間的交互瓶頸得到緩解。近年來PCIe演進正在加速,以滿足對日益增長的帶寬需求。目前PCIe 5.0也已經(jīng)商用,未來PCIe 6.0的協(xié)議也已經(jīng)基本完成,單個PCIe 6.0 x16就可以支持800G以太網(wǎng)絡。

由于PCIe本身有很多問題,限制了目前計算架構的突破(例如樹形結構,不支持一致性等),因此業(yè)界曾經(jīng)產(chǎn)生了不少新的協(xié)議,例如開始由Xilinx主推后來由Arm商用的CCIX, IBM自己搞的OpenCAPI, AMD的Infinity Fabric以及NVidia的NVLink,以及多年前提出來的Gen-Z協(xié)議,到現(xiàn)在Intel最新的CXL。

目前看起來由于Intel在服務器市場強大的市占率和話語權,CXL的前景還是被普遍看好。其底層是沿用PCIe PHY(目前是5.0),上層協(xié)議進行了重新的建構。

除了我們熟悉的針對PCIE的局限性做出的新的設計,CXL也帶了很多新的應用,內存是最典型的,它可以將內存和處理器解耦,串行化,并且CXL2.0的switch的支持,可以做到內存池化。這會大大提高訪存效率,極大降低成本,增加靈活性。對服務器和數(shù)據(jù)中心的新計算架構帶來更多可能性。CXL的推廣將會持續(xù)推動PCIe快速成長。

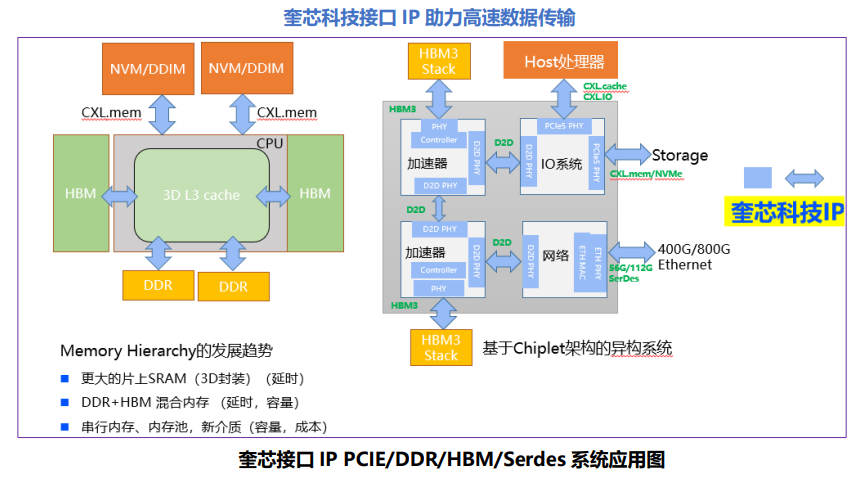

奎芯科技接口IP助力高速數(shù)據(jù)傳輸

奎芯接口IP PCIE/DDR/HBM/Serdes系統(tǒng)應用圖

在未來的計算架構將從處理器為中心逐漸轉變成以數(shù)據(jù)為中心同時,奎芯科技攜手優(yōu)秀研發(fā)團隊已完成PCIe3/4的芯片認證(Silicon-Proven),被廣泛應用于各類設備的數(shù)據(jù)傳輸,PCIe5正處于研發(fā)階段。同時用于Chiplet高速互聯(lián)的D2D/Serdes接口以及高帶寬DDR5/HBM3也在同步開發(fā)中,預計2022~2023年將陸續(xù)推向市場,阻力高速數(shù)據(jù)傳輸。奎芯科技通過一系列的技術創(chuàng)新及優(yōu)化升級,打破能效墻、優(yōu)化墻、內存墻和高速IO墻,進一步釋放計算潛能,秉持國產(chǎn)化IP的專業(yè)研發(fā)技術,結合半導體行業(yè)發(fā)展趨勢,提供優(yōu)秀的解決方案助力芯片設計企業(yè)!

關于奎芯科技(MSQUARE):

奎芯科技(M SQUARE)于2021年在上海注冊成立,是一家專業(yè)的集成電路IP供應商。作為芯片產(chǎn)業(yè)鏈上游關鍵技術環(huán)節(jié)的企業(yè),公司推出的高速接口IP,涵蓋USB、PCIe、SATA、SerDes、MIPI、DDR、HDMI、DP、HBM等產(chǎn)品,聚焦高性能計算、人工智能、消費類電子、汽車電子、物聯(lián)網(wǎng)等領域,致力于通過先進半導體IP研發(fā)與定制服務,打造市場急需的IP組合,積極響應中國快速發(fā)展的芯片和應用需求﹐全面賦能芯片設計產(chǎn)業(yè)。