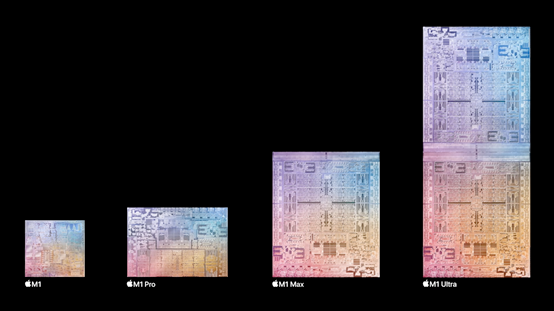

昨日凌晨的蘋(píng)果春季發(fā)布會(huì)上,蘋(píng)果發(fā)布了最強(qiáng)的 “M1 Ultra”芯片。

本文引用地址:http://www.eepw.com.cn/article/202203/432003.htm

在大會(huì)上,蘋(píng)果公布了 M1 Ultra 芯片很多牛逼的參數(shù),比如:晶體管數(shù)量1140億顆;20核CPU(16 個(gè)高性能內(nèi)核和 4 個(gè)高效內(nèi)核);最高64核GPU;32核神經(jīng)網(wǎng)絡(luò)引擎;2.5TB/s數(shù)據(jù)傳輸速率;800GB/s內(nèi)存帶寬;最高128GB統(tǒng)一內(nèi)存。

M1 Ultra 是 Apple 芯片的又一個(gè)游戲規(guī)則改變者,它將再次震撼 PC 行業(yè)。通過(guò)將兩個(gè)M1 Max 芯片與我們的 UltraFusion 封裝架構(gòu)相連接,我們能夠?qū)?Apple 芯片擴(kuò)展到前所未有的新高度。

蘋(píng)果公司硬件技術(shù)高級(jí)副總裁Johny Srouji表示:“憑借其強(qiáng)大的CPU、龐大的 GPU、令人難以置信的神經(jīng)引擎、ProRes 硬件加速和海量統(tǒng)一內(nèi)存,M1 Ultra 完善了M1系列,成為世界上最強(qiáng)大、功能最強(qiáng)大的個(gè)人計(jì)算機(jī)芯片。”

蘋(píng)果的Ultra Fushion架構(gòu)

眾所周知,要做更強(qiáng)大的芯片,就需要堆更多的電路,更多的晶體管,而工藝越先進(jìn),同樣的面積就能塞進(jìn)去更多晶體管,芯片性能上限就越高,這也是為何大家追求更先進(jìn)制程的原因之一。

但在當(dāng)下的工藝技術(shù)條件下,晶體管多了,良率就會(huì)降低,良率低了,那每個(gè)芯片就會(huì)變得非常昂貴,那么如何才能在降低成本的前提下,做出超越極限的芯片呢?

蘋(píng)果的做法是采用M1 Max中隱藏的芯片互連模塊,通過(guò)UltraFushion架構(gòu)把兩塊芯片像拼拼圖一樣“合二為一”。

蘋(píng)果的“UltraFushion”其實(shí)就是Die to Die Connection,就是在芯片設(shè)計(jì)時(shí)在同一個(gè)封裝(package)里面使用多枚硅片(silicon),并且在其中設(shè)計(jì)極其高速的互聯(lián)通道,使得這兩塊硅片可以形同一塊芯片一樣共同工作。

UltraFusion使用了1萬(wàn)條DTD連接,提供了高達(dá)2.5TB/s的互聯(lián)速度,它的帶寬極高、能耗極低,而且由于是數(shù)塊die共同封裝,其對(duì)良率的敏感度要遠(yuǎn)低于一塊超巨型芯片,因此DTD也被認(rèn)為是未來(lái)芯片性能發(fā)展的一條具有巨大潛力的道路。

值得一提的是,M1 Max是一個(gè)基于小芯片(Chiplet)的設(shè)計(jì)中將多個(gè)芯片堆疊在一起的芯片模塊(MCM),其2-tile的規(guī)格使其從CPU到GPU到NPU到內(nèi)存帶寬到內(nèi)存容量,全部都是2xM1 Max的規(guī)格。

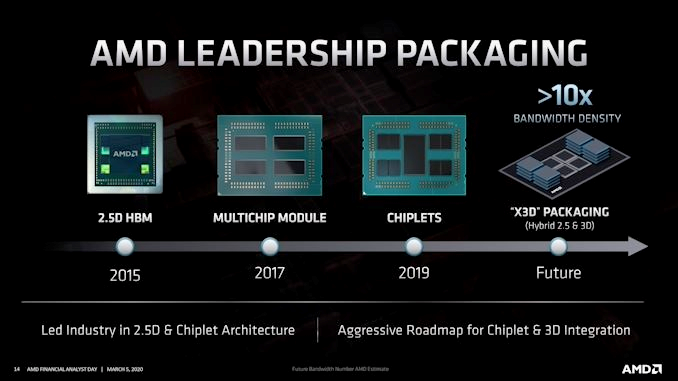

與華為的“芯片疊加專(zhuān)利”思路一致

當(dāng)然這條道路也不是只有蘋(píng)果在走,AMD 早在 2017 年就引入了MCM 并且在 2019 年引入了Chiplet 設(shè)計(jì),未來(lái)的發(fā)展趨勢(shì)是進(jìn)一步提升堆疊能力,實(shí)現(xiàn)所謂的 3D 堆疊,也就是不僅在 2D 上擴(kuò)展,還要在垂直方向上擴(kuò)展。

而國(guó)內(nèi)企業(yè)有同樣思路的就是華為海思了。在2021年5月份的時(shí)候,華為將“雙芯疊加”的專(zhuān)利進(jìn)行了公開(kāi),并表示14nm技術(shù)可以到達(dá)7nm的性能,此消息一出頓時(shí)在世界范圍內(nèi)引起熱議,得到全球的關(guān)注。簡(jiǎn)單來(lái)講14nm與7nm之間,它們的主要差別就是在芯片面積相同的情況下,7nm可以擁有更多的晶體管數(shù)量,在性能方面自然也會(huì)有所提升。

高性能產(chǎn)品走Chiplet這條路走得通

知乎用戶(hù)@超合金彩虹糖表示,這顆M1Ultra是蘋(píng)果野心的進(jìn)一步延續(xù),連最有錢(qián)的蘋(píng)果也轉(zhuǎn)向Chiplet了,這預(yù)示著也許未來(lái)在消費(fèi)級(jí)領(lǐng)域,高性能產(chǎn)品走Chiplet這條路可以走得通。目前來(lái)看,芯片組合疊加已經(jīng)從理論變成現(xiàn)實(shí),從芯片封裝的角度來(lái)看,逐漸從2.5D封裝走向3D封裝,芯粒(Chiplet) 將提供最佳性能和最大靈活性。臺(tái)積電、英特爾、三星、AMD等十家公司已經(jīng)行動(dòng)了,聯(lián)合創(chuàng)建UCIe聯(lián)盟。(詳情:英特爾、AMD、Arm等九大企業(yè)宣布UCle開(kāi)放標(biāo)準(zhǔn),推動(dòng)Chiplet發(fā)展)

UCIe聯(lián)盟創(chuàng)建的初衷是將小芯片打造成開(kāi)放,互聯(lián)的產(chǎn)業(yè)發(fā)展生態(tài),讓不同客戶(hù)也能通過(guò)各類(lèi)小芯片產(chǎn)品滿足更多的需求。

未來(lái),以Chiplet模式集成的芯片會(huì)是一個(gè)“超級(jí)”異構(gòu)系統(tǒng),可以帶來(lái)更多的靈活性和新的機(jī)會(huì)。

芯原股份創(chuàng)始人、董事長(zhǎng)兼總裁戴偉民曾表示,對(duì)于產(chǎn)業(yè)來(lái)說(shuō),Chiplet帶來(lái)了新的機(jī)會(huì),在標(biāo)準(zhǔn)與生態(tài)層次上,Chiplet建立了新的可互操作的組件、互連協(xié)議和軟件生態(tài)系統(tǒng);對(duì)于芯片制造與封裝來(lái)說(shuō),增設(shè)了多芯片模塊 (Multi-Chip Module,MCM) 業(yè)務(wù),Chiplet迭代周期遠(yuǎn)低于ASIC,可提升晶圓廠和封裝廠的產(chǎn)線利用率;對(duì)于半導(dǎo)體IP來(lái)說(shuō),升級(jí)為Chiplet供應(yīng)商,可提升IP的價(jià)值且有效降低芯片客戶(hù)的設(shè)計(jì)成本;最后對(duì)于芯片設(shè)計(jì)來(lái)說(shuō),降低了大規(guī)模芯片設(shè)計(jì)的門(mén)檻。

戴偉民建議國(guó)內(nèi)企業(yè)持續(xù)推進(jìn)Chiplet量產(chǎn)和2.5D/3D封測(cè)技術(shù)開(kāi)發(fā)。