存儲器是現(xiàn)代信息系統(tǒng)的關(guān)鍵組件之一,其應(yīng)用廣泛,市場龐大。由DRAM與NAND Flash所主導(dǎo)的主導(dǎo)的傳統(tǒng)存儲市場規(guī)模已超過1600億美元,而且長遠來看,DRAM和NAND仍將占據(jù)主流市場很久。那么存儲技術(shù)發(fā)展到現(xiàn)在,這兩大主流的傳統(tǒng)存儲技術(shù)背后的供應(yīng)商們都在比拼什么?

NAND Flash廠商在拼什么?

一、拼層數(shù),蓋高樓

幾十年來,NAND Flash一直是低成本和大密度數(shù)據(jù)存儲應(yīng)用的主要技術(shù)。這種非易失性存儲器存在于所有主要的電子終端市場,例如智能手機、服務(wù)器、PC、平板電腦和 USB 驅(qū)動器。NAND Flash的成功與其不斷擴展存儲密度和成本的能力有關(guān),大約每兩年,NAND Flash 行業(yè)就能夠大幅提高位存儲密度,現(xiàn)在位存儲密度的進一步增加是通過向三維過渡,2014年,3D NAND技術(shù)進入市場。而為了維持NAND Flash路線圖,3D NAND Flash進入了層數(shù)的堆疊比拼。

2022年是NAND閃存的35周年,而今年或許是NAND閃存又一個重要的一年。現(xiàn)在幾乎頭部的存儲廠商都在制造200層以上的存儲芯片,甚至500層已經(jīng)陸續(xù)出現(xiàn)在存儲廠商們的路線圖中。閃存芯片中的層數(shù)越多,容量就越高。下表顯示了幾大NAND 制造商的3D NAND 的層數(shù)的主要計劃:

圖源:blocks&files

在NAND FLash領(lǐng)域,三星電子將在2022年底推出200層或更多層的第8代NAND閃存。據(jù)businesskorea的報道,有業(yè)內(nèi)人士認為,三星已經(jīng)通過“雙棧”的方式獲得了256層技術(shù)。用于連接單元的孔越少,芯片丟失的數(shù)據(jù)就越少。因此,單棧技術(shù)比雙棧技術(shù)更先進。然而,100層被認為是單棧技術(shù)的技術(shù)極限。目前,三星電子是世界上唯一一家可以使用單堆疊方式堆疊超過 100 層(128 層)的芯片制造商。全球第二大 NAND 閃存生產(chǎn)商 SK 海力士和美國美光科技一直在使用雙堆棧技術(shù)堆疊72層或更多層。

業(yè)內(nèi)人士預(yù)測,三星電子將加快200層以上NAND閃存的量產(chǎn)步伐,他們表示三星電子將成為第一家通過在128層單堆棧中增加96層來發(fā)布224層NAND 閃存的芯片制造商。與 176層相比,224層NAND閃存的生產(chǎn)效率和數(shù)據(jù)傳輸速度將提高30%。

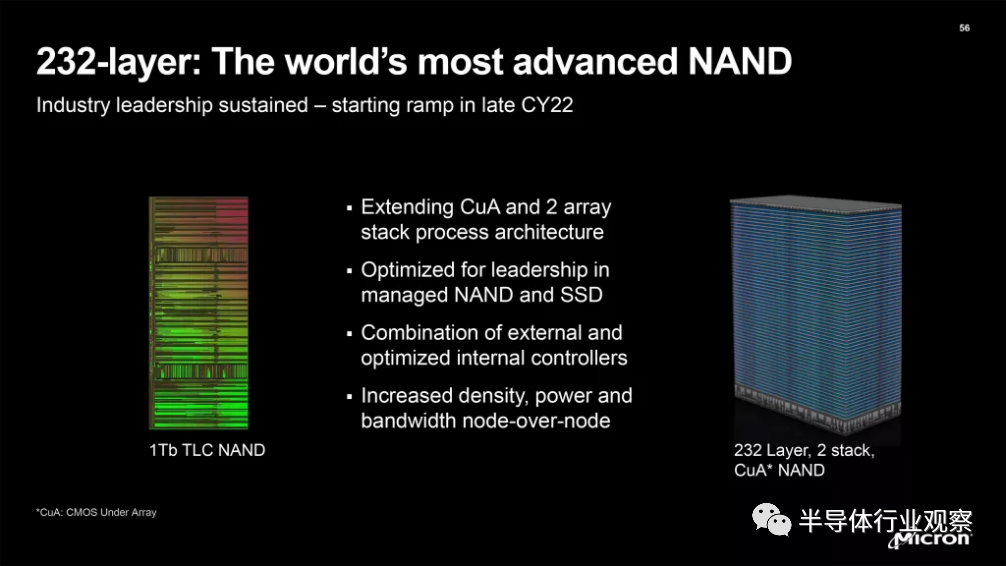

美光正在批量生產(chǎn)176層的閃存芯片,這是其第五代3D NAND。3D NAND是通過在垂直堆棧中將多組單元相互層疊來制造的。美光近日表示,其正在開發(fā)232層的3D NAND,并聲稱其232層技術(shù)代表了世界上最先進的NAND,路線圖規(guī)劃到了500層(但沒具體指明時間表)。

美光的232層NAND芯片采用3D TLC架構(gòu),原始容量為1Tb (128GB)。該芯片基于美光的 CuA(CMOS under array)架構(gòu),并使用 NAND串堆疊技術(shù)在彼此之上構(gòu)建兩個3D NAND陣列。CuA的設(shè)計加上232層的NAND將大大減少美光1Tb 3D TLC NAND存儲器的裸片尺寸,這將降低生產(chǎn)成本,使美光能夠具有芯片定價權(quán)。

(圖片來源:美光)

西部數(shù)據(jù)和鎧俠近日表示,他們正在構(gòu)建162層的NAND,該公司計劃在2022年底推出其第6代 BiCS。西部數(shù)據(jù)聲稱他們將通過使用新材料來縮小存儲單元的尺寸,從而縮小芯片尺寸。西部數(shù)據(jù)計劃將這些芯片用于從USB驅(qū)動器到PCIe 5.0 SSD的等多種產(chǎn)品中。

資料來源:西部數(shù)據(jù)

此外,西部數(shù)據(jù)還將于2024年推出具有超過200層的BiCS+內(nèi)存,與BiCS6相比,它的每個晶圓的位數(shù)將增加55%,傳輸速度提高60%,寫入速度提高15%。值得注意的是,BiCS+僅用于數(shù)據(jù)中SSD,因為該公司計劃為消費者存儲提供不同級別的2xx層 NAND,稱為BiCS-Y。除此之外,西部數(shù)據(jù)還表示,他們正在研究多種技術(shù)以提高密度和容量,包括 PLC,并計劃在2032年構(gòu)建500層以上的NAND。

SK海力士在200層的跨越上可能稍微晚些,目前為止SK海力士最新的3D NAND是512Gb 176層堆疊的3D NAND,不過早在去年3月份的IEEE IRPS上,SK海力士CEO李錫熙就已經(jīng)展望到600層。

國內(nèi)方面主要競爭者是長江存儲,長江存儲這幾年的發(fā)展很快,此前長江存儲CEO楊士寧層表示:“長江存儲用短短3年時間實現(xiàn)了從32層到64層再到128層的跨越。長江存儲3年完成了他們6年走過的路”。而現(xiàn)在,據(jù)Digitimes的報道,業(yè)內(nèi)人士透露,長江存儲最近已向少數(shù)客戶交付了其內(nèi)部開發(fā)的192 層3D NAND閃存樣品。

這些巨頭廠商清晰明確的NAND路線圖也證明了NAND 和 SSD 市場的技術(shù)健康和活力。總體而言,NAND閃存供應(yīng)商都準備在2022年底至2023年之間推出其200 層以上的芯片產(chǎn)品,這是該行業(yè)向更高密度3D NAND 閃存過渡的里程碑。

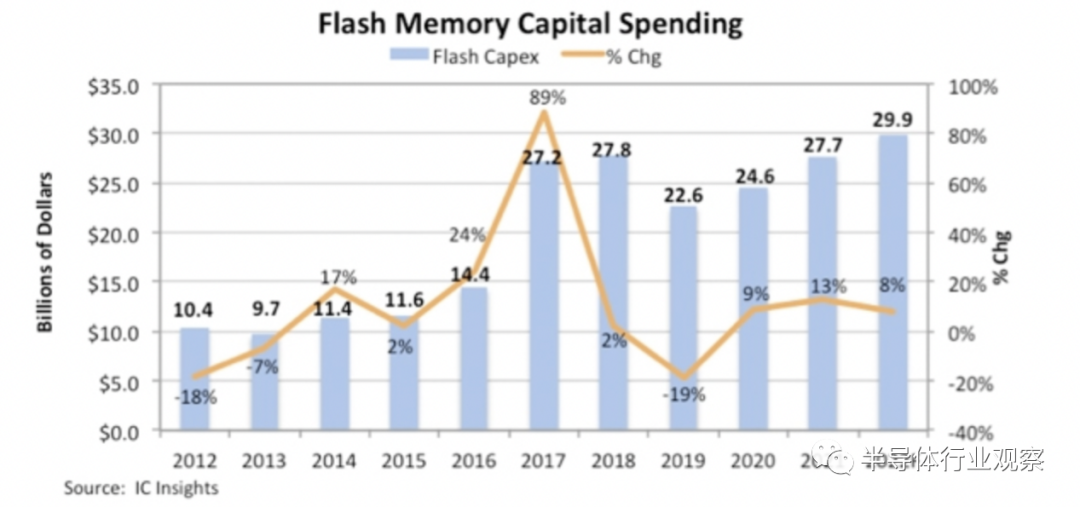

二、拼資本支出,拼產(chǎn)能

對于存儲廠商來說,重資本是行業(yè)的特點,產(chǎn)能的保障也是企業(yè)保持致勝的一大關(guān)鍵。而隨著NAND閃存供應(yīng)商加入200層以上NAND閃存芯片的競爭,必將需要新的晶圓廠和新設(shè)備。

IC Insights預(yù)測今年NAND閃存資本支出將增8%至299億美元,超過2018年278 億美元的歷史新高。閃存資本支出在2017年飆升,當(dāng)時該行業(yè)向3D NAND過渡,此后每年資本支出都超過200億美元。299億美元的支出占2022年整個IC行業(yè)1904億美元資本支出預(yù)測的16%,僅落后于代工部門,該部門預(yù)計將占今年行業(yè)資本支出的41%。

來源:IC insights

新的和最近升級的NAND閃存工廠包括三星的平澤P1和P2(也用于 DRAM 和代工),以及三星在中國西安的二期投資;鎧俠在日本巖手的 Fab 6 (Flash Ventures) 和 Fab K1;美光在新加坡的第三家閃存工廠。SK海力士為其 M15 工廠的剩余空間配備了 NAND閃存。

此外,據(jù)TheElec獲悉,三星計劃于今年5月初在其平澤工廠的新先進晶圓廠P3上安裝晶圓廠設(shè)備,該公司的目標(biāo)是在今年下半年內(nèi)完成工廠的建設(shè),消息人士稱,三星將首先在5月的第一周為NAND閃存生產(chǎn)安裝晶圓廠設(shè)備。P3是一家混合工廠,將同時生產(chǎn)存儲芯片和邏輯芯片,其中就包括第七代176層V-NAND芯片。預(yù)計三星未來幾年將在P3上花費至少30萬億韓元到近50萬億韓元。

而SK海力士也在大連建設(shè)新的3D NAND閃存晶圓廠,該項目于5月16日開工。2021年底,SK海力士完成了收購英特爾NAND閃存及SSD業(yè)務(wù)案的第一階段,從英特爾手中接管了SSD業(yè)務(wù)及其位于大連的NAND閃存制造廠的資產(chǎn)。為加快推動項目發(fā)展,所以SK海力士決定在大連繼續(xù)擴大投資并建設(shè)新工廠。

DRAM廠商拼什么?

不可不爭的EUV

隨著DRAM要想進入到10nm工藝一下,EUV儼然已成必不可少。我們也看到,三星、SK海力士和美光這三大DRAM廠商已經(jīng)先后擁抱了EUV技術(shù)。

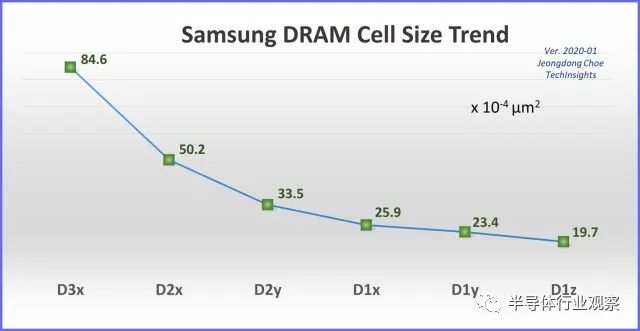

三星電子基于極紫外(EUV)光刻技術(shù)的1z-nm工藝的DRAM已于今年2月份完成了量產(chǎn)。半導(dǎo)體分析機構(gòu)TechInsights拆解了采用EUV光刻技術(shù)和ArF-i光刻技術(shù)的三星1z-nm工藝DRAM,它認為該技術(shù)提升了三星的生產(chǎn)效率,并減小了DRAM的核心尺寸。DRAM 單元尺寸和 D/R 縮放最近越來越難,但三星將 D1z 的 D/R 降低到 15.7 nm,比 D1y 縮小了 8.2%。據(jù)了解,三星還將繼續(xù)為下一代DRAM增加EUV步驟。上文中提到的三星的P3工廠也將采用EUV工藝生產(chǎn)10nm DRAM。

三星 DRAM 單元尺寸趨勢,D3x 到 D1z

(圖源:TechInsights)

美光有望從2024年開始生產(chǎn)基于極紫外 (EUV) 光刻工藝的DRAM 芯片,在1γ(Gamma)節(jié)點的有限的層數(shù)中部署 EUV,然后會將其擴展到具有更大層采用率的1δ(Delta)節(jié)點。旨在通過允許制造更小的芯片特征來保持摩爾定律的存在。這一舉措有望幫助其在技術(shù)上保持領(lǐng)先于競爭對手。

SK海力士也引入了EUV光刻設(shè)備來解決以往DUV光刻的局限性,制程工藝能輕松達到10nm以下,以此來提升生產(chǎn)效率。2021年2月1日,SK海力士完成首個用于DRAM的EUV晶圓廠M16,并引進了EUV光刻設(shè)備。2021年7月,SK海力士宣布量產(chǎn)了1anm工藝的8千兆的LPDDR4 EUV DRAM。

3D堆疊成為DRAM新未來

但是對于DRAM來說,目前業(yè)界的共識或者面臨的挑戰(zhàn)是,在平面工藝下,DRAM最重要也最艱難的挑戰(zhàn),就是儲存電容的高深寬比,儲存電容的深寬比通常會隨著組件工藝微縮而呈倍數(shù)增加,也就是說,平面DRAM的工藝微縮會越來越困難,即使是通過極紫外光刻 (EUV) 工藝,也不足以為整個未來十年提供所需的位密度改進。因此,主要設(shè)備供應(yīng)商和領(lǐng)先的DRAM制造商正在考慮將單片3D DRAM(類似 3D NAND)作為長期擴展的潛在解決方案。

據(jù)了解,3D DRAM是將存儲單元(Cell)堆疊至邏輯單元上方以實現(xiàn)在單位晶圓面積上產(chǎn)出上更多的產(chǎn)量,這樣3D DRAM就可以有效地解決平面DRAM的挑戰(zhàn)。除了晶圓的裸晶產(chǎn)出量增加外,使用3D堆疊技術(shù)也能因為可重復(fù)使用儲存電容而有效降低 DRAM的單位成本。

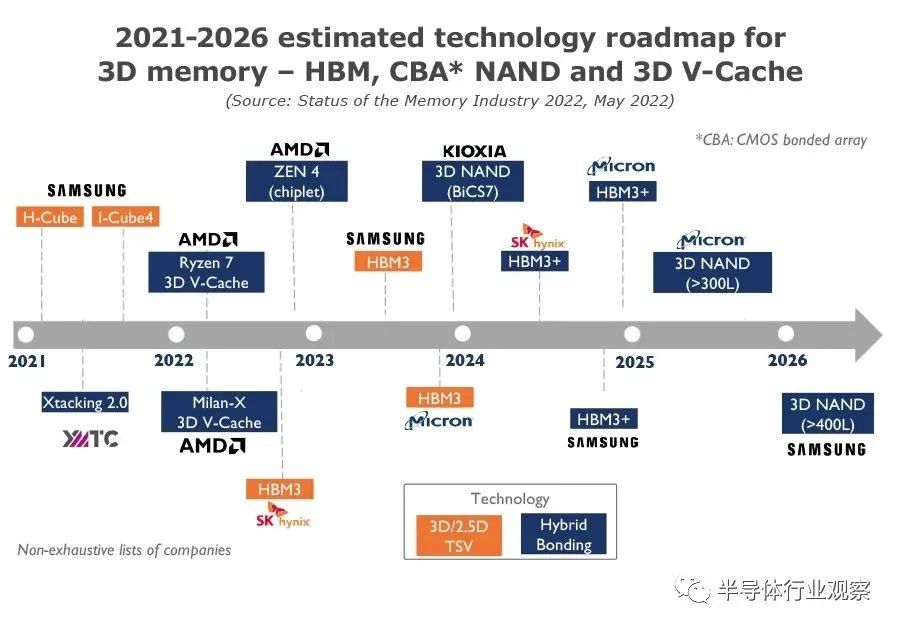

在這其中,HBM(High Bandwidth Memory,高帶寬存儲器)技術(shù)可謂是DRAM從傳統(tǒng)2D向立體3D發(fā)展的主要代表產(chǎn)品,使DRAM開啟了3D化道路。HBM是通過TSV技術(shù)進行芯片堆疊,以增加吞吐量并克服單一封裝內(nèi)帶寬的限制。HBM能充分利用空間并縮小面積,并且突破了內(nèi)存容量與帶寬瓶頸。

據(jù)Yole的觀點和預(yù)測,這種新穎的3D技術(shù)將在2029-2030年期間進入市場。在此之前,我們預(yù)計混合鍵合系統(tǒng)可能會開始滲透 DRAM 設(shè)備市場,用于制造3D堆疊 DRAM,例如高帶寬內(nèi)存 (HBM),可能從HBM3+一代開始。

寫在最后

現(xiàn)在諸如數(shù)據(jù)中心、汽車、5G等對內(nèi)存的需求越來越大,要求也越來越高,技術(shù)的演進也一直在滾滾向前。不同時代,不同需求下,這些存儲廠商們總能研發(fā)出新的技術(shù)來滿足時代的發(fā)展。當(dāng)然新型存儲也是時代發(fā)展的產(chǎn)物,它們不是為了取代現(xiàn)有的存儲解決方案,而是在延遲、生產(chǎn)力等方面對現(xiàn)有的存儲進行很好的補充。最后說一句,存儲是不得不發(fā)展的國家戰(zhàn)略性高技術(shù)產(chǎn)業(yè),我國應(yīng)該抓住存儲器技術(shù)發(fā)展多元化的新機遇,實現(xiàn)突破。