芯片行業(yè)對(duì)于流片都不陌生。

所謂流片,,就是像流水線一樣通過(guò)一系列工藝步驟制造芯片,該環(huán)節(jié)處于芯片設(shè)計(jì)和芯片量產(chǎn)的中間階段,,是芯片制造的關(guān)鍵環(huán)節(jié),。

簡(jiǎn)單來(lái)說(shuō)就是將設(shè)計(jì)好的方案,交給芯片制造廠,,先生產(chǎn)幾片幾十片樣品,,檢測(cè)一下設(shè)計(jì)的芯片能不能用,然后進(jìn)行優(yōu)化,。如果測(cè)試通過(guò),,就按照這樣開始大規(guī)模生產(chǎn)了。

所以為了測(cè)試集成電路設(shè)計(jì)是否成功,,必須進(jìn)行流片,。這也是芯片設(shè)計(jì)企業(yè)一般都在前期需要投入很大成本的重要原因。

一顆芯片從設(shè)計(jì)到量產(chǎn),,流片屬于非常關(guān)鍵的環(huán)節(jié),。當(dāng)芯片完全設(shè)計(jì)出來(lái)以后需要按照?qǐng)D紙?jiān)诰A上進(jìn)行蝕刻,采用什么樣的制程工藝,,多大尺寸的晶圓,,芯片的復(fù)雜程度都會(huì)影響這顆芯片的流片成功率和成本,而且許多芯片都不是一次就能流片成功的,,往往需要進(jìn)行多次流片才能獲得較為理想的效果,。

但流片是一件非常燒錢的事,多幾次流片失敗,,可能就會(huì)把公司搞垮,。2019年就曾傳出小米旗下松果電子的澎拜S2系列芯片連續(xù)5次流片失敗,,設(shè)計(jì)團(tuán)隊(duì)重組的慘痛案例,。

有芯片大廠算過(guò)這筆賬,14nm工藝芯片,,流片一次需要300萬(wàn)美元左右,,7nm工藝芯片,,流片一次需要3000萬(wàn)美元,5nm工藝芯片,,流片一次更是達(dá)到4725萬(wàn)美元,。可見,,流片對(duì)于芯片設(shè)計(jì)企業(yè)來(lái)說(shuō)是一筆巨大花費(fèi),,尤其是對(duì)于行業(yè)中小企業(yè)來(lái)講,實(shí)際流片的價(jià)格比大廠又高很多,,讓本不富裕的“生活”更是雪上加霜,。

流片為什么這么貴?

那芯片流片的價(jià)格為什么這么貴,?

這就要提到芯片的制造原理了,。

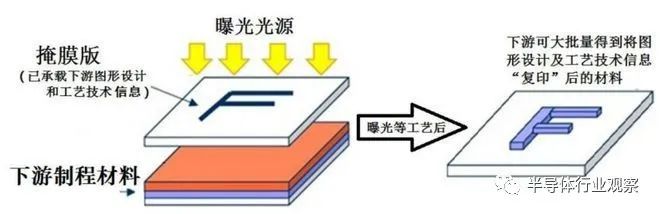

芯片制造要在很小的芯片里放上億個(gè)晶體管,制造工藝已經(jīng)到了納米級(jí),,只能用光刻來(lái)完成,。光刻就是用光刻出想要的圖形,光刻需要用到掩膜版(又稱光罩,,Mask),,掩膜版就是把設(shè)計(jì)好的電路圖雕刻在上面,讓光通過(guò)后,,在晶圓上刻出圖形,。

流片貴,一方面是因?yàn)閯傞_始有許多工藝需要驗(yàn)證,,從一個(gè)電路圖到一塊芯片,,檢驗(yàn)每一個(gè)工藝步驟是否可行,檢驗(yàn)電路是否具備所要的性能和功能,。芯片流片過(guò)程至少持續(xù)三個(gè)月(包括原料準(zhǔn)備,、光刻、摻雜,、電鍍,、封裝測(cè)試),一般要經(jīng)過(guò)1000多道工藝,,生產(chǎn)周期較長(zhǎng),,因此也是芯片制造中最重要最耗錢的環(huán)節(jié)。

如果流片成功,,就可以據(jù)此大規(guī)模地制造芯片,;反之,就需要找出其中的原因,,并進(jìn)行相應(yīng)的優(yōu)化設(shè)計(jì),。

其中,,芯片流片貴,主要貴在掩膜版和晶圓,,這兩項(xiàng)價(jià)格不菲且都是消耗品,,其中掩膜版最貴,一套中端工藝制程的掩膜版價(jià)格大約在50萬(wàn)美元左右,,而一片晶圓的價(jià)額也在數(shù)千美元,。

掩膜貴還是晶圓貴?

掩膜版是一種由石英為材料制成的,,是微電子制造過(guò)程中的圖形轉(zhuǎn)移工具或母版,,其功能類似于傳統(tǒng)照相機(jī)的“底片”,根據(jù)客戶所需要的圖形,,通過(guò)光刻制版工藝,,將微米級(jí)和納米級(jí)的精細(xì)圖案刻制于掩膜版基板上,是承載圖形設(shè)計(jì)和工藝技術(shù)等內(nèi)容的載體,。

然后把這種從掩膜版的圖形轉(zhuǎn)換到晶圓上的過(guò)程,,想象成印鈔機(jī)的工作流程。把光刻機(jī)想象成印鈔機(jī),,晶圓相當(dāng)于印鈔紙,,掩膜就是印版,把鈔票母版的圖形印到紙張上的過(guò)程,,就像光刻機(jī)把掩膜版上的芯片圖形印到晶圓上一樣,。

光刻需要用到掩膜版,掩膜版就是把設(shè)計(jì)好的電路圖雕刻在上面,,讓光通過(guò)后,,在晶圓上刻出圖形。

光刻工作原理

掩膜版的質(zhì)量會(huì)直接影響光刻的質(zhì)量,,掩膜版上的制造缺陷和誤差也會(huì)伴隨著光刻工藝被引入到芯片制造中,。因此,掩膜版是下游產(chǎn)品精度和質(zhì)量的決定因素之一,。

掩膜版的價(jià)格主要取決于芯片所選用的“工藝節(jié)點(diǎn)”,,工藝節(jié)點(diǎn)越高、流片價(jià)格就越貴,。這是因?yàn)樵较冗M(jìn)的工藝節(jié)點(diǎn),,所需要使用的掩膜版層數(shù)就越多。據(jù)了解,,在14nm工藝制程上,,大約需要60張掩膜版,7nm可能需要80張甚至上百?gòu)堁谀ぐ妗?/p>

掩膜版層數(shù)多了,不僅僅是因?yàn)檠谀ぐ宓膬r(jià)格貴,,還因?yàn)槊慷喑鲆粚?“掩膜板”,就要多進(jìn)行一次“光刻”,,就要再多涂抹一次 “光刻膠”,,就要再多一次 “曝光”,然后再來(lái)一次 “顯影” ...,,整個(gè)流程下來(lái)耗費(fèi)的成本就大大增加了,。

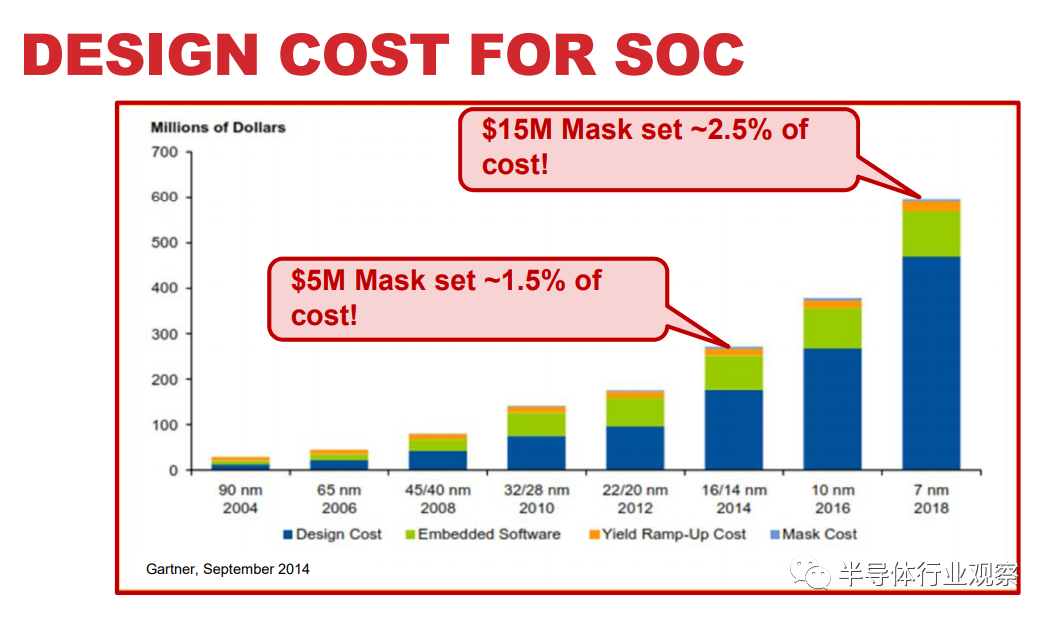

據(jù)IBS數(shù)據(jù)顯示,在16/14nm制程中,,所用掩膜成本在500萬(wàn)美元左右,,到7nm制程時(shí),掩膜成本迅速升至1500萬(wàn)美元,。

7nm制程中,,掩膜成本大概為1500萬(wàn)美元

(圖源:IBS)

掩膜版的總體費(fèi)用,,包括石英,,光刻膠等原材料的成本,Mask Writer和Inspection等機(jī)臺(tái)的使用成本,,另外還有掩膜版相關(guān)數(shù)據(jù)的生成,,包括OPC、MDP等軟件授權(quán),、服務(wù)器使用和人工開發(fā)成本等等,。對(duì)于一款芯片,動(dòng)輒幾十層的掩膜版,,需要如此多的步驟,,設(shè)備、軟件,、人員缺一不可,,費(fèi)用自然昂貴。

在流片中,,Mask的費(fèi)用更是占很大一塊,,是因?yàn)榍捌诹髌A段就是生產(chǎn)5-25片作為產(chǎn)品驗(yàn)證用的,主要成本是Mask成本,。對(duì)應(yīng)的,,正式生產(chǎn)時(shí),Mask的費(fèi)用只算一次,,后面有大量的晶圓可以分?jǐn)偝杀?,自然就便宜了?/p>

準(zhǔn)確的說(shuō)應(yīng)該是平均到每一顆芯片上的費(fèi)用便宜了,而不是總的流片費(fèi)用便宜了。

據(jù)業(yè)內(nèi)人士透露,,某晶圓代工廠(Foundry) 40nm的流片成本大概在60-90萬(wàn)美元,。Mask占據(jù)大頭,大約60-90萬(wàn)美元,;晶圓成本每片在3000-4000美元左右,。

所以,如果生產(chǎn)10片晶圓,,每片晶圓的成本是(90萬(wàn)+ 4000*10)/10=9.4萬(wàn)美元,;但是如果生產(chǎn)10000片晶圓,那么每片晶圓的成本是(90萬(wàn)+4000*10000)/10000=4090美元,。

可見,,進(jìn)入量產(chǎn)之后,生產(chǎn)上萬(wàn)片晶圓,,每片晶圓可能3000-4000美元左右,,Mask的成本平攤到每片晶圓以后就很少了,這時(shí)候晶圓的成本就是主要的成本來(lái)源,。所以,,如果只是量小的流片階段,那么Mask成本是主要的,。反之如果量產(chǎn)很多,,那么則是晶圓主導(dǎo)成本。

另外,,半導(dǎo)體制造廠的機(jī)臺(tái)便宜的上百萬(wàn)美元,,貴的上億美元。據(jù)了解,,28nm的Mask機(jī)臺(tái)就超過(guò)5000萬(wàn)美元一臺(tái),,這些儀器,機(jī)臺(tái)需要七年折舊完畢,。也就是說(shuō),,大概使用一年就要損失14%的機(jī)臺(tái)價(jià)值。

晶圓代工行業(yè)設(shè)備折舊年限通常是5-7年,。據(jù)報(bào)道,,中芯國(guó)際2019年折舊費(fèi)用超過(guò)了14億,主要是因?yàn)橄冗M(jìn)制程的投入需要購(gòu)置部分單價(jià)較高的機(jī)器設(shè)備,,使得折舊費(fèi)用逐年增加,。臺(tái)積電2021年折舊費(fèi)用更是達(dá)到近千億新臺(tái)幣,創(chuàng)史上最高,。

從工藝研發(fā)周期來(lái)講,,機(jī)器的成本和折舊費(fèi)已然很高,但將工藝的良率及可靠性調(diào)到量產(chǎn)要求也是一項(xiàng)有挑戰(zhàn)的工作。(據(jù)悉某廠搞28nm,,機(jī)器2011/2012年就全部到位了, 可是5,、6年后良率都還沒(méi)調(diào)到嚴(yán)格的量產(chǎn)標(biāo)準(zhǔn),可見有多難,。同時(shí)還白白損失了多年的設(shè)備折舊費(fèi)用,。)

其次還有人力成本,維護(hù)成本以及耗材費(fèi)等,,這些都是Mask成本高的原因,。

據(jù)etnews報(bào)道,,隨著當(dāng)前供需狀況惡化,,掩膜版的價(jià)格還在上漲,交貨時(shí)間也一再被推遲,,即使支付額外費(fèi)用,,也很難及時(shí)購(gòu)買到。通常需要4-7天的交期最近增至14天,,部分企業(yè)的交期延長(zhǎng)到了原來(lái)的7倍,。

此外,為了跟上摩爾定律,,F(xiàn)oundry升級(jí)換代所需的設(shè)備和技術(shù)研發(fā)的投資不斷增大,,由于Foundry對(duì)先進(jìn)生產(chǎn)線的投資巨大,必然會(huì)將其成本轉(zhuǎn)嫁到客戶的投片費(fèi)用上,。這也導(dǎo)致了制造芯片的費(fèi)用在不斷上漲,。

如何降低流片成本?

上述種種因素影響下,,芯片流片費(fèi)用成為擺在設(shè)計(jì)企業(yè)面前的一個(gè)難題,。那么,面對(duì)流片價(jià)格高的問(wèn)題,,有沒(méi)有什么辦法來(lái)降低成本,?

摩爾精英資深總監(jiān)王龍向筆者表示,MPW (Multi Project Wafer) 就是一種可以幫助設(shè)計(jì)企業(yè)降低成本的流片方式,。MPW是指由多個(gè)項(xiàng)目共享某個(gè)晶圓,,同一次制造流程可以承擔(dān)多個(gè)IC設(shè)計(jì)的制造任務(wù),將多個(gè)使用相同工藝的集成電路設(shè)計(jì)放在同一晶圓上流片,,制造完成后,,每個(gè)設(shè)計(jì)可以得到數(shù)十片芯片樣品,這一數(shù)量對(duì)于原型設(shè)計(jì)階段的實(shí)驗(yàn),、測(cè)試已經(jīng)足夠,。

通俗來(lái)講就是幾家公司或機(jī)構(gòu)一起購(gòu)買一套掩膜版,然后生產(chǎn)出來(lái)的同一片晶圓上會(huì)同時(shí)存在有好幾款芯片,待晶圓切割后,,再把各自的芯片“領(lǐng)回家”,。而該次制造費(fèi)用就由所有參加MPW的項(xiàng)目按照芯片面積分?jǐn)偅瑯O大地降低了產(chǎn)品開發(fā)風(fēng)險(xiǎn),。

據(jù)王龍介紹,,MPW有一定的流程,通常由晶圓代工廠或者第三方服務(wù)機(jī)構(gòu)來(lái)進(jìn)行組織,,各種工藝在某一年之中的MPW時(shí)間點(diǎn)是預(yù)先設(shè)定好的,,通常是越先進(jìn)的工藝,安排的MPW頻率越高,。晶圓代工廠事先會(huì)將晶圓劃好多個(gè)區(qū)域并報(bào)價(jià),,各家公司根據(jù)自己情況去預(yù)訂一個(gè)或多個(gè)區(qū)域。

這對(duì)參與者來(lái)說(shuō),,在設(shè)計(jì)和開發(fā)方面有一定的進(jìn)度壓力,。但是相比之下,MPW帶來(lái)的好處是顯而易見的,,采用多項(xiàng)目晶圓能夠降低芯片的生產(chǎn)成本,,為設(shè)計(jì)人員提供實(shí)踐機(jī)會(huì),并促進(jìn)了芯片設(shè)計(jì)的成果轉(zhuǎn)化,,對(duì)IC設(shè)計(jì)人才的培訓(xùn),,中小設(shè)計(jì)公司的發(fā)展,以及新產(chǎn)品的開發(fā)研制都有相當(dāng)大的促進(jìn)作用,。

對(duì)比來(lái)看,,共享Mask的好處就是省錢,但是可能要等代工廠的時(shí)間節(jié)點(diǎn),,需要更多的時(shí)間,。對(duì)于那些不差錢或趕時(shí)間的企業(yè)當(dāng)然可以自己利用一套Mask(Full- Mask,全掩膜),,制造流程中的全部掩膜都為自己的設(shè)計(jì)來(lái)服務(wù),,通常用于設(shè)計(jì)定型后的量產(chǎn)階段。機(jī)器一響,,黃金萬(wàn)兩,。

但是,在當(dāng)前產(chǎn)能嚴(yán)重緊缺的情況下,,代工廠面對(duì)不同客戶的產(chǎn)品需求,、競(jìng)爭(zhēng)優(yōu)勢(shì)、市場(chǎng)前景和計(jì)劃等態(tài)度是完全不同的,,代工廠會(huì)綜合考慮客戶下單量,,后續(xù)下單穩(wěn)定性以及產(chǎn)品所面向的市場(chǎng)前景來(lái)做判斷,。

實(shí)際上,對(duì)于大部分的中小企業(yè)來(lái)說(shuō),,除了價(jià)格以外,,在流片或量產(chǎn)環(huán)節(jié)還面臨著包括產(chǎn)能、交期在內(nèi)的諸多挑戰(zhàn):

1.對(duì)Foundry體系不了解,,缺乏工藝選型的經(jīng)驗(yàn)和Foundry打交道的經(jīng)驗(yàn),;

2.主流Foundry準(zhǔn)入門檻高,新興玩家難以申請(qǐng)預(yù)期的工藝或支持,,溝通成本高,;

3.缺乏系統(tǒng)的供應(yīng)鏈管理能力,尤其在量產(chǎn)產(chǎn)能爬坡階段,,對(duì)產(chǎn)能,、交期、質(zhì)量過(guò)于樂(lè)觀,;

4.產(chǎn)能緊缺情況下,,缺乏備貨機(jī)制,,恐慌性下單或有了訂單再下單導(dǎo)致產(chǎn)能跟不上市場(chǎng)需求,。此外,交期的變化,、產(chǎn)能的波動(dòng)都會(huì)大大增加初創(chuàng)公司與晶圓代工廠的溝通成本,,降低效率。

對(duì)此,,中小芯片設(shè)計(jì)企業(yè)可以尋求有資源,、有實(shí)力、有經(jīng)驗(yàn)的第三方運(yùn)營(yíng)服務(wù)機(jī)構(gòu)進(jìn)行合作,,一同來(lái)解決遇到的供應(yīng)鏈難題,。

以摩爾精英流片業(yè)務(wù)為例,可以提供完整的工藝平臺(tái),,對(duì)接數(shù)十家主流晶圓代工廠,,提供MPW、Full-mask及量產(chǎn)在內(nèi)的不同工藝節(jié)點(diǎn)的流片服務(wù),,能夠顯著降低客戶的商務(wù)成本和溝通成本,。

另一方面,憑借自建的專業(yè)流片F(xiàn)AE團(tuán)隊(duì),,不僅為合作晶圓代工廠提供長(zhǎng)尾客戶的高效支持管理,,也幫助中小公司的產(chǎn)品快速得到支持,協(xié)助客戶選擇最優(yōu)工藝,,并保障客戶的數(shù)據(jù)安全,。

在產(chǎn)能方面,,利用摩爾精英的know-how協(xié)助中小客戶去爭(zhēng)取產(chǎn)能(包括大訂單、訂單量趨勢(shì),、提前排隊(duì),、及時(shí)跟蹤產(chǎn)能動(dòng)態(tài)等),幫助客戶降低成本和縮短芯片研發(fā)周期,。

綜合來(lái)看,,無(wú)論是從技術(shù)、商務(wù)還是產(chǎn)能方面,,選擇一家靠譜的第三方機(jī)構(gòu)都可以協(xié)助設(shè)計(jì)公司解決當(dāng)前所遇到的供應(yīng)鏈難點(diǎn),,提供最優(yōu)解。

總而言之,,處于這些需求賽道中的公司們都可能從流片服務(wù)廠商的業(yè)務(wù)中獲利,。

寫在最后

一個(gè)芯片開發(fā)項(xiàng)目,需要經(jīng)歷從產(chǎn)品定義,、設(shè)計(jì),、驗(yàn)證仿真一直到最終流片的漫長(zhǎng)過(guò)程,而作為“終極大考”的流片,,此前漫長(zhǎng)過(guò)程中的任何一個(gè)小疏忽都可能導(dǎo)致流片失敗,,而一旦流片失敗往往意味著企業(yè)將面臨數(shù)千萬(wàn)美元起的損失和至少半年市場(chǎng)機(jī)遇的錯(cuò)失。

這對(duì)于許多企業(yè)而言,,流片失敗是無(wú)法承受之痛,。

對(duì)此,芯片設(shè)計(jì)企業(yè),、制造商以及相關(guān)的行業(yè)服務(wù)平臺(tái)和機(jī)構(gòu)應(yīng)緊密合作,,優(yōu)勢(shì)互補(bǔ),攜手解決困擾開發(fā)者的“流片難題”,。