交互式人工智能(CAI)簡介

什么是交互式人工智能(AI)?

交互式人工智能(CAI)使用機(jī)器學(xué)習(xí)(ML)的子集深度學(xué)習(xí)(DL),通過機(jī)器實現(xiàn)語音識別、自然語言處理和文本到語音的自動化。CAI流程通常用三個關(guān)鍵的功能模塊來描述:

1. 語音轉(zhuǎn)文本(STT),也稱為自動語音識別(ASR)

2 自然語言處理(NLP)

3 文本轉(zhuǎn)語音(TTS)或語音合成

圖1:交互式AI構(gòu)建模塊

本篇白皮書詳細(xì)介紹了自動語音識別(ASR)的應(yīng)用場景,以及Achronix如何在實現(xiàn)ASR解決方案的同時將相關(guān)成本降低高達(dá)90%。

細(xì)分市場和應(yīng)用場景

僅在美國就有超過1.1億個虛擬助手在發(fā)揮作用[1],大多數(shù)人對使用CAI服務(wù)都很熟悉。主要示例包括移動設(shè)備上的語音助手,例如蘋果的Siri或亞馬遜的Alexa;筆記本電腦上的語音搜索助手,例如微軟的Cortana;自動呼叫中心應(yīng)答助理;以及支持語音功能的設(shè)備,例如智能音箱、電視和汽車等。

支持這些CAI服務(wù)的深度學(xué)習(xí)算法可以在本地電子設(shè)備上進(jìn)行處理,或者聚集在云中進(jìn)行遠(yuǎn)程大規(guī)模處理。支持?jǐn)?shù)百萬用戶交互的大規(guī)模部署是一個巨大的計算處理挑戰(zhàn),超大規(guī)模的提供商已經(jīng)通過開發(fā)專用的芯片和設(shè)備來處理這些服務(wù)。

現(xiàn)在,大多數(shù)小型企業(yè)都可以使用亞馬遜、IBM、微軟和谷歌等公司提供的云API,輕松地將語音接口添加到他們的產(chǎn)品中。然而,當(dāng)這些工作負(fù)載的規(guī)模增加時(本白皮書后面將介紹一個具體的示例),使用這些云API的成本將會變得過高,迫使企業(yè)尋求其他解決方案。此外,許多企業(yè)運(yùn)營對數(shù)據(jù)安全性有更高的要求,因此需要將解決方案必須保留在企業(yè)的數(shù)據(jù)安全范圍內(nèi)。

企業(yè)級CAI解決方案可用于以下應(yīng)用場景:

· 自動呼叫中心

· 語音和視頻通信平臺

· 健康和醫(yī)療服務(wù)

· 金融和銀行服務(wù)

· 零售和售貨販賣設(shè)備

詳細(xì)介紹ASR處理過程

ASR是CAI流程的第一步,在這里語音被轉(zhuǎn)錄為文本。一旦文本可用,就可以使用自然語言處理(NLP)算法以多種方式對其進(jìn)行處理。NLP包括關(guān)鍵內(nèi)容識別、情感分析、索引、語境化內(nèi)容和分析。在端到端的交互式AI算法中,語音合成用于生成自然的語音響應(yīng)。

最先進(jìn)的ASR算法是通過端到端的深度學(xué)習(xí)來實現(xiàn)。不同于卷積神經(jīng)網(wǎng)絡(luò)(CNN),遞歸神經(jīng)網(wǎng)絡(luò)(RNN)在語音識別中很常見。正如來自TechTarget [10]的David Petersson在《CNN與RNN:它們有何不同?》文章中提到:RNN更適合處理時間數(shù)據(jù),與ASR應(yīng)用非常適配。基于RNN的模型需要較高的計算能力和存儲帶寬來處理神經(jīng)網(wǎng)絡(luò)模型,并滿足交互式系統(tǒng)所需的嚴(yán)格的延遲目標(biāo)。當(dāng)實時或自動響應(yīng)太慢時,它們會顯得遲緩和不自然。通常只有犧牲處理效率才能實現(xiàn)低延遲,這會增加成本,并且對于實際部署來說會變得過于龐大。

Achronix與采用現(xiàn)場可編程邏輯門陣列(FPGA)進(jìn)行AI推理的專業(yè)技術(shù)公司Myrtle.ai展開合作。Myrtle.ai利用其MAU推理加速引擎在FPGA上實現(xiàn)基于RNN的高性能網(wǎng)絡(luò)。該設(shè)計已集成到Achronix Speedster?7t AC7t1500 FPGA器件中,可以利用Speedster7t架構(gòu)的關(guān)鍵架構(gòu)優(yōu)勢(將在本白皮書后面進(jìn)行探討),大幅提高實時ASR神經(jīng)網(wǎng)絡(luò)的加速處理,從而與服務(wù)器級中央處理器(CPU)相比,可處理的實時數(shù)據(jù)流(RTS)的數(shù)量增加2500%。

數(shù)據(jù)加速器:如何實現(xiàn)資源的合理平衡分配

數(shù)據(jù)加速器可以卸載通常由主CPU執(zhí)行的計算、網(wǎng)絡(luò)和/或存儲處理工作負(fù)載,從而可以顯著減少服務(wù)器的占用空間。本白皮書介紹了用一臺服務(wù)器和一個Achronix基于ASR的加速卡可取代多達(dá)25臺服務(wù)器。這種架構(gòu)大大降低了工作負(fù)載成本、功耗和延遲,同時提高了工作負(fù)載吞吐量。然而,只有在硬件得到有效使用并且部署具有成本效益的情況下,使用數(shù)據(jù)加速硬件來實現(xiàn)高性能和低延遲才有意義。

ASR模型對現(xiàn)代數(shù)據(jù)加速器來說是一種挑戰(zhàn),通常需要手動調(diào)整以實現(xiàn)比平臺主要性能規(guī)格的個位數(shù)效率更高的性能。實時ASR工作負(fù)載需要高存儲帶寬以及高性能計算。這些大型神經(jīng)網(wǎng)絡(luò)所需的數(shù)據(jù)通常存儲在加速卡上的DDR存儲器中。將數(shù)據(jù)從外部存儲器傳輸?shù)接嬎闫脚_是該工作負(fù)載中的性能瓶頸,特別是在進(jìn)行實時部署的時候。

圖形處理器(GPU)架構(gòu)是基于數(shù)據(jù)并行模型,較小的批處理量(batch size)會導(dǎo)致GPU加速硬件的利用率較低,從而導(dǎo)致成本增加和效率降低。硬件加速解決方案數(shù)據(jù)表(以TOPS即每秒萬億次操作為單位進(jìn)行衡量)中的性能數(shù)據(jù)并不能總是很好地表示實際性能,因為許多硬件加速器件由于與器件架構(gòu)相關(guān)的瓶頸而未得到充分利用。這些數(shù)據(jù)以TOPS為單位,強(qiáng)調(diào)了加速器計算引擎的處理能力,但忽略了關(guān)鍵因素,例如外部存儲器的批處理量、速度和規(guī)模,以及在外部存儲器和加速器計算引擎之間傳輸數(shù)據(jù)的能力。對于ASR工作負(fù)載,關(guān)注存儲帶寬和在加速器內(nèi)高效地傳輸數(shù)據(jù)為加速器性能和效率的實現(xiàn)提供了更強(qiáng)有力的指導(dǎo)。

加速器必須具有更大的外部存儲規(guī)模和非常高的帶寬。當(dāng)今的高端加速器通常使用高性能的外部存儲器,存儲規(guī)模達(dá)8-16 GB,運(yùn)行速度可高達(dá)4 Tbps。它還必須能夠?qū)⑦@些數(shù)據(jù)傳輸?shù)接嬎闫脚_而不會影響性能。然而,無論如何去實現(xiàn)高速存儲和計算引擎之間的數(shù)據(jù)通道,它幾乎在所有情況下都是系統(tǒng)性能的瓶頸,特別是在實時ASR這樣的低延遲應(yīng)用中。

FPGA設(shè)計旨在存儲和計算之間提供最佳的數(shù)據(jù)路由通道,從而為這些工作負(fù)載提供一個出色的加速平臺。

Achronix解決方案與其他FPGA解決方案的對比

在機(jī)器學(xué)習(xí)(ML)加速領(lǐng)域中,已有FPGA架構(gòu)宣稱其推理速度可高達(dá)150 TOPS。然而在實際應(yīng)用中,尤其是在那些對延遲敏感的應(yīng)用(如ASR)中,由于無法在計算平臺和外部存儲器之間高效地傳輸數(shù)據(jù),所以這些FPGA遠(yuǎn)不能達(dá)到其聲稱的最高推理速度。由于數(shù)據(jù)從外部存儲器傳輸?shù)紽PGA器件中的計算引擎時出現(xiàn)了瓶頸,從而造成了這種性能上的損失。Achronix Speedster7t架構(gòu)在計算引擎、高速存儲接口和數(shù)據(jù)傳輸之間取得了良好的平衡,使Speedster7t FPGA器件能夠為實時、低延遲的ASR工作負(fù)載提供高性能,可實現(xiàn)最高TOPS速率的64%等級。

圖2:Speedster7t器件的計算、存儲和數(shù)據(jù)傳輸能力

Speedster7t架構(gòu)如何實現(xiàn)更高的計算效率

在Speedster7t上搭載的機(jī)器學(xué)習(xí)處理器(MLP)是一種優(yōu)化的矩陣/向量乘法模塊,能夠在單個時鐘周期內(nèi)進(jìn)行32次乘法和1次累加,是計算引擎架構(gòu)的基礎(chǔ)。AC7t1500器件中的Block RAM(BRAM)與2560個MLP實例都處于同一位置,這意味著更低的延遲和更高的吞吐量。

借助于這些關(guān)鍵的架構(gòu)單元,Myrtle.ai的MAU低延遲、高吞吐量的ML推理引擎已集成到Speedster7t FPGA器件中。

在構(gòu)建最佳的ASR解決方案時,集成了之前提到的來自Myrtle.ai的MAU推理引擎,使用了2560個MLP中的2000個。由于MLP是一個硬模塊,它可以運(yùn)行在比FPGA邏輯陣列本身更高的時鐘速率上。

圖3:機(jī)器學(xué)習(xí)處理器

在AC7t1500器件中使用了8個GDDR6存儲控制器,它們總共可提供高達(dá)4 Tbps的雙向帶寬。如上所述,強(qiáng)大的計算引擎和大容量、高帶寬的存儲依賴于高速、低延遲和確定性的數(shù)據(jù)傳輸,以提供低延遲ASR應(yīng)用所需的實時結(jié)果。

隨后這些數(shù)據(jù)進(jìn)入到Speedster7t的二維片上網(wǎng)絡(luò)(2D NoC)。該二維片上網(wǎng)絡(luò)是Speedster7t架構(gòu)中的另一種硬結(jié)構(gòu),時鐘頻率高達(dá)2 GHz,可與所有I/O、內(nèi)部硬模塊和FPGA邏輯陣列本身互連。憑借20 Tbps的總帶寬,2D NoC提供了最高的吞吐量,并通過適當(dāng)?shù)膶崿F(xiàn)方式,可以在外部GDDR6存儲器和支持MLP的計算引擎之間提供最具確定性的、低延遲的數(shù)據(jù)傳輸。

圖4:總帶寬為20 Tbps的2D NoC

與其他競爭性廠商的解決方案不同,2D NoC消除了Speedster7t ASR解決方案在存儲器和計算引擎之間的任何瓶頸,在這些非常低的批處理速率下,硬件加速器的利用率達(dá)到最佳狀態(tài)。

將所有這些功能放在一個roofline圖中,就可以清楚地說明Achronix Speedster7t器件在低延遲ASR應(yīng)用中相對于其他競爭性FPGA解決方案的優(yōu)勢。該roofline圖使用了由每個制造商公布的經(jīng)過驗證的TOPS數(shù)據(jù),展示了這些器件在實際應(yīng)用中可以達(dá)到的效果。

下圖顯示了一個有效TOPS的roofline模型,它使用了Achronix為微基準(zhǔn)(GEMV和MLP)和測試而構(gòu)建的子集,以及公司A [4] [5]和公司B(基于架構(gòu))發(fā)布的數(shù)據(jù)。橙色的豎線表示批處理量為8毫秒和80毫秒音頻模塊的最佳操作點(diǎn),用于低延遲、實時ASR數(shù)據(jù)流應(yīng)用。在這個最佳操作點(diǎn)上,Achronix的有效TOPS比公司A提高了44%,比公司B的解決方案提高了260%。

圖5:有效TOPS的Roofline模型

在一年內(nèi)實現(xiàn)ASR處理成本降低高達(dá)90%的目標(biāo)

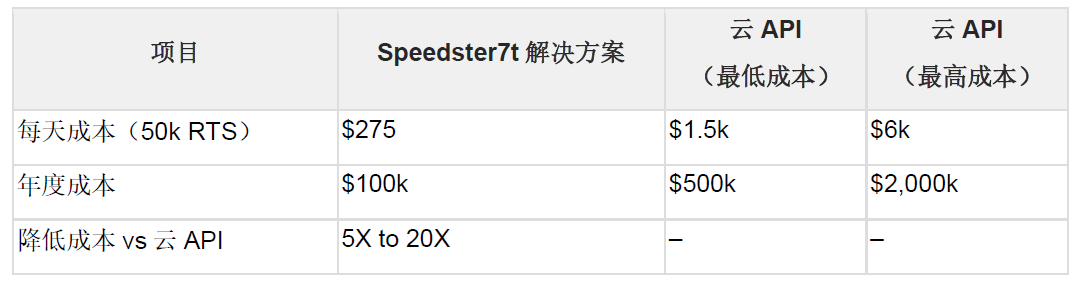

大多數(shù)ASR解決方案由Google、Amazon、Microsoft Azure和Oracle等大型云服務(wù)提供商提供。隨著運(yùn)營規(guī)模的擴(kuò)大,以及這些產(chǎn)品在市場上取得的成功,在這些云API基礎(chǔ)上構(gòu)建產(chǎn)品的服務(wù)提供商面臨著越來越高的成本壓力。較大規(guī)模的ASR提供商公開宣傳成本從每分鐘0.01美元到0.025美元不等[6]、[7]、[8]、[9]。行業(yè)報告顯示,呼叫中心的平均呼叫時間約為5分鐘。考慮一個大型企業(yè)數(shù)據(jù)或呼叫中心服務(wù)公司每天要處理50,000通電話,每通電話5分鐘。按照上述費(fèi)率計算,ASR處理成本將是每天1,500至6,000美元或每年50萬至200萬美元。Achronix和Myrtle.ai的解決方案可以集成在一個加速卡上支持處理4000個RTS,每天可以處理超過一百萬次的呼叫。

有許多因素會決定獨(dú)立ASR設(shè)備的成本。在這個特定示例中,假設(shè)Achronix ASR加速解決方案是通過基于FPGA的PCIe卡提供,并集成到基于x86架構(gòu)的2U服務(wù)器中。該設(shè)備從系統(tǒng)集成商那里出售,價格可能為50,000美元,而每年運(yùn)行服務(wù)器的成本可能是這個成本的兩倍。這樣一來,本地ASR設(shè)備第一年的費(fèi)用就達(dá)到了10萬美元。將這種本地解決方案與云API服務(wù)進(jìn)行比較,終端用戶可以在第一年節(jié)省5到20倍的費(fèi)用。

表1:Achronix ASR解決方案與云API服務(wù)的對比總結(jié)

高度緊湊的系統(tǒng)使企業(yè)能夠隨著其業(yè)務(wù)的增加而擴(kuò)展,而無需依賴日益昂貴的ASR云API,也無需構(gòu)建龐大的數(shù)據(jù)中心基礎(chǔ)設(shè)施來提供本地解決方案。

總結(jié)

CAI中的ASR功能要求RNN機(jī)器學(xué)習(xí)算法具有低延遲、高吞吐量的計算,這對現(xiàn)代AI加速器提出了挑戰(zhàn)。聲稱推理速度高達(dá)150 TOPS的FPGA硬件加速器在大型計算引擎和高速存儲器之間傳輸數(shù)據(jù)時會遇到瓶頸,這些瓶頸可能導(dǎo)致硬件利用率低至5%。Achronix和Myrtle.ai攜手推出一個ASR平臺,該平臺由一個200W、x16 PCIe Gen4加速卡和相關(guān)軟件組成,可以同時支持多達(dá)4000個RTS,每24小時可以處理多達(dá)100萬個、時長5分鐘的轉(zhuǎn)錄文件。將單臺x86服務(wù)器上的PCIe加速卡與云ASR服務(wù)的成本相比,第一年的資本支出(CAPEX)和運(yùn)營成本(OPEX)就可以降低高達(dá)90%。

參考資料:

1.https://www.statista.com/statistics/973815/worldwide-digital-voice-assistant-in-use/

2.https://www.microsoft.com/en-us/research/project/project-brainwave/

3.Myrtle.ai未發(fā)表的白皮書,關(guān)于在Speedster AC7t1500器件中托管的ASR應(yīng)用

4.M. Langhammer, G. Baeckler和S. Gribok,《SpiderWeb-高性能FPGA NoC》,2020 IEEE國際并行和分布式處理研討會(IPDPSW),2020年,第115-118頁,doi:10.1109/IPDPSW50202.2020.00025。

5.https://arxiv.org/pdf/2010.06075.pdf

6.https://aws.amazon.com/transcribe

7.https://cloud.google.com/speech-to-text

8.https://www.ibm.com/cloud/watson-speech-to-text

9.https://docs.microsoft.com/en-us/azure/cognitive-services/speech-service

更多信息可以來這里獲取==>>電子技術(shù)應(yīng)用-AET<<