引言:我們繼續(xù)介紹FPGA PCB設(shè)計(jì)相關(guān)知識,本章介紹7系列FPGA的配電系統(tǒng)(PDS),包括去耦電容器的選擇、放置和PCB幾何結(jié)構(gòu),并為每個(gè)7系列FPGA提供了一種簡單的去耦方法。另外,還介紹了PDS的基本設(shè)計(jì)原則,以及仿真和分析方法。本章包括以下部分:

PCB去耦電容器

基本PDS原則

仿真方法

PDS測量

噪聲故障排除

1. PCB去耦電容

1.1 各型FPGA器件推薦的PCB去耦電容

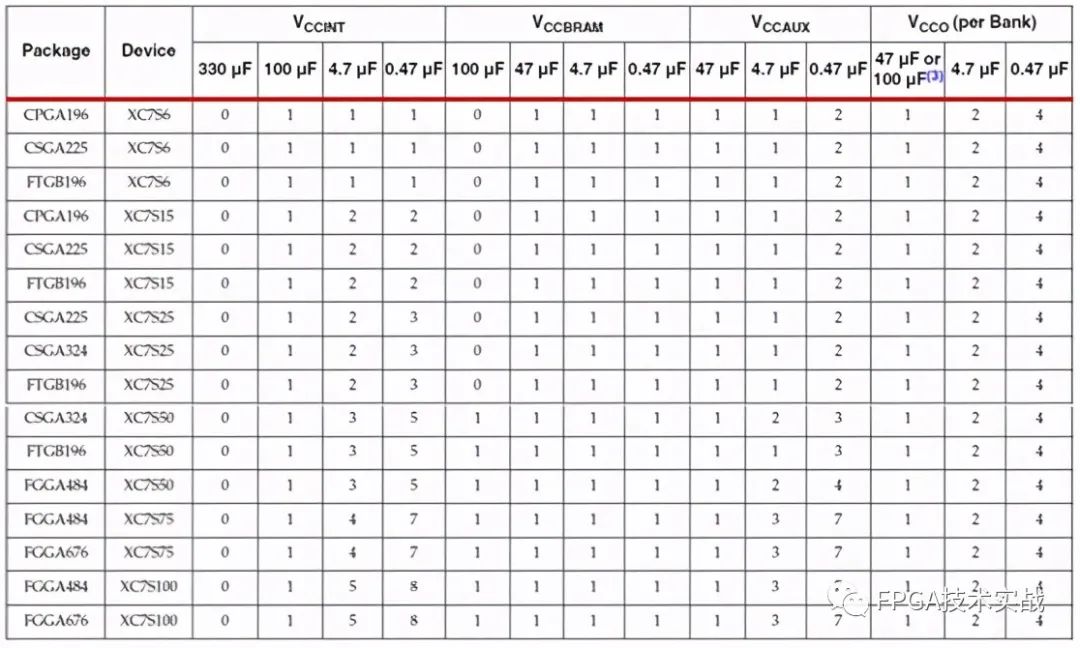

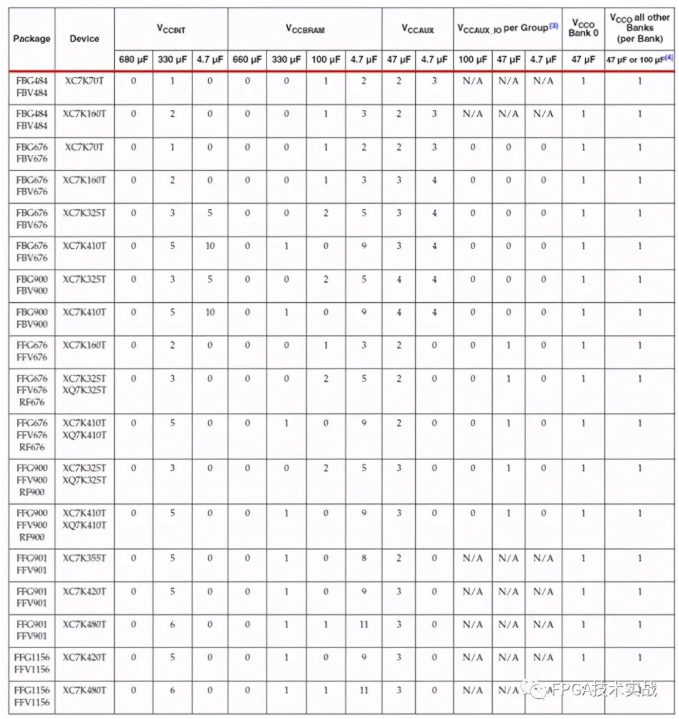

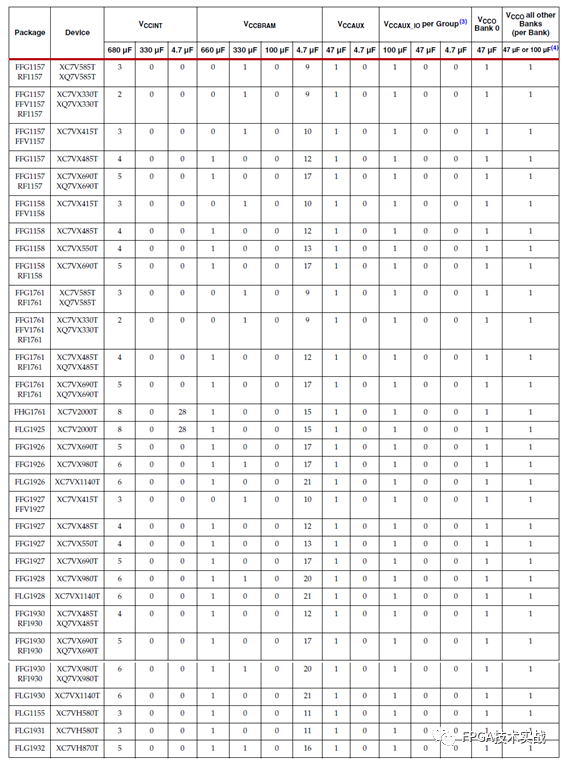

表1-1~1-4分別列出了適用于Spartan?-7器件、 ArtixTM-7器件、 KintexTM-7以及VirtexTM-7器件的去耦網(wǎng)絡(luò)電容參數(shù)。在表1-1、表1-2、表1-3和表1-4中,PCB去耦電容器的優(yōu)化數(shù)量假設(shè)電壓調(diào)節(jié)器具有穩(wěn)定的輸出電壓并滿足穩(wěn)壓器制造商的最小輸出電容要求。

可以使用這些表中所示方法以外的去耦方法,但去耦網(wǎng)絡(luò)的設(shè)計(jì)應(yīng)滿足或超過此處所示簡單去耦網(wǎng)絡(luò)的性能。在100 KHz到10 MHz的頻率范圍內(nèi),備用網(wǎng)絡(luò)的阻抗必須小于或等于推薦網(wǎng)絡(luò)的阻抗。

由于設(shè)備電容要求隨CLB和I/O利用率的變化而變化,因此基于非常高的利用率以每個(gè)器件為基礎(chǔ)提供PCB去耦指南,以便涵蓋大多數(shù)用例。資源使用(部分)包括:

1.80% of LUTs and registers at 245 MHz

2.80% block RAM and DSP at 491 MHz

3.50% MMCM and 25% PLL at 500 MHz

4.100% I/O at SSTL 1.2/1.35 at 1,200/800 MHz

Xilinx的XPE工具可以用于估計(jì)每個(gè)電源的電流,DS189、DS181、DS182、DS183文檔分別為Spartan-7、Artix-7、Kintex-7和Virtex-7器件提供各種電源軌DC和AC電氣開關(guān)特性。PCB設(shè)計(jì)師應(yīng)確保交流(AC)紋波加上電壓調(diào)節(jié)器的直流(DC)誤差不超過工作范圍。本用戶指南中顯示的電容器數(shù)量基于以下假設(shè):

VCCINT電壓允許范圍:3%;

假設(shè)DC誤差:1%;

因此,允許的AC紋波:3% - 1% = 2%

利用2% AC紋波和XPE軟件工具對上述資源利用率的電流估計(jì)值計(jì)算目標(biāo)阻抗,以得出電容器建議值。

VCCINT、VCCAUX和VCCBRAM電容器列為每個(gè)器件使用的數(shù)量,而VCCO電容器列為每個(gè)I/O組的數(shù)量。當(dāng)使用這些推薦的網(wǎng)絡(luò)時(shí),所有設(shè)備在充分利用率下的設(shè)備性能是等效的。

注意:表1-1~1-4沒有提供GTP、GTX和GTH收發(fā)器電源去耦要求,對于收發(fā)器去偶設(shè)計(jì)要求需要參考各收發(fā)器對應(yīng)的用戶指導(dǎo)手冊。對于補(bǔ)充本用戶指南的綜合原理圖檢查清單,請參考文檔XMP277,該文檔給出了詳細(xì)的原理圖設(shè)計(jì)要求(關(guān)注公眾號 FPGA技術(shù)實(shí)戰(zhàn),回復(fù) SCH01,下載該文件)。

表1-1:每個(gè)器件所需的PCB電容器數(shù)量:Spartan-7器件

表1-2:每個(gè)器件所需的PCB電容器數(shù)量:Artix-7器件

表1-3:每個(gè)器件所需的PCB電容器數(shù)量:Kintex-7器件

表1-4:每個(gè)器件所需的PCB電容器數(shù)量:Virtex-7器件

說明:

PCB電容器規(guī)格見表1-5。

總計(jì)包括所有電源所需電容器,但MGT電源MGTAVCC、MGTVCAUX和MGTAVTT除外,這些在7系列FPGA收發(fā)器用戶指南中。

請參閱UG471,7系列FPGA SelectIO資源用戶指南,了解VCCAUX_IO 電源軌規(guī)范的說明,以了解在每個(gè)VCCAUX_IO組中哪些I/O組被分組在一起。請參閱UG475,7系列FPGA封裝和引腳產(chǎn)品規(guī)范,以了解在每個(gè)VCCAUX_IO組中哪些I/O組被分組在一起。

當(dāng)由相同電壓供電時(shí),最多四個(gè)VCCO組需要一個(gè)47μF(或100μF)電容器。

如果為每組的VCCAUX_IO列出N/A,則這些組件沒有HP I/O組或VCCAUX_IO引腳。

去耦電容器覆蓋約100kHz。

1.2 電容要求

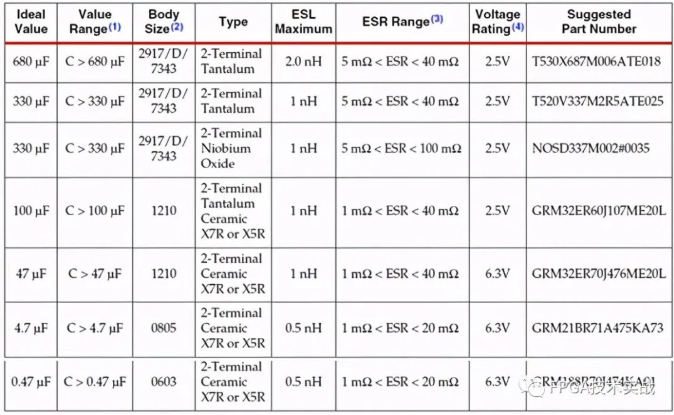

表1-5規(guī)定了表1-1、表1-2、表1-3和表1-4中電容的電氣特性,并遵循了可接受替代的指南。為這些電容器規(guī)定的等效串聯(lián)電阻(ESR)范圍可以過大。然而,這需要對產(chǎn)生的配電系統(tǒng)阻抗進(jìn)行分析,以確保不會(huì)產(chǎn)生諧振阻抗尖峰。

表1-5 PCB電容特性要求

說明:

容值可以大于指定值。

電容尺寸可以小于指定值。

ESR必須在指定范圍內(nèi)。

額定電壓可以高于規(guī)定值。

1.3 Bulk電容考慮規(guī)則

大容量電容器(D,1210)的目的是覆蓋電壓調(diào)節(jié)器截止工作和封裝陶瓷電容器開始工作之間的低頻范圍。如表1-1、表1-2、表1-3和表1-4所示,所有FPGA電源都需要大容量電容器。

選擇表1-5中規(guī)定的氧化鉭和氧化鈮電容器作為其值和控制ESR值。它們也符合ROHS標(biāo)準(zhǔn)。如果使用其他制造商的鉭、氧化鈮或陶瓷電容器,用戶必須確保其符合表2-5的規(guī)范,并通過模擬、S參數(shù)寄生提取或臺(tái)架測試進(jìn)行適當(dāng)評估。

注:用陶瓷電容器代替鉭電容器,在交流負(fù)載下有效電容值可降低50%左右。

有時(shí),許多I/O組由相同的電壓(例如1.8V)供電,建議的指南要求使用多個(gè)大容量電容器。更大的7系列FPGA中的VCCINT、VCCAUX、VCCAUX_IO和VCCBRAM也是如此。如果合并電容器(ESR和ESL)的電氣特性與推薦電容器并聯(lián)組合的電氣特性相同,則這些較小的電容器可以合并為較少(較大值)的電容器。

對于大多數(shù)VCCO、VCCINT、VCCAUX、VCCAUX_IO和VCCBRAM電容器的整合,具有足夠低ESL和ESR的大型鉭電容器是可用的。

1.4 PCB電容放置和貼裝技術(shù)

PCB Bulk電容

大容量電容器(D,1210)可能很大,有時(shí)很難靠近FPGA放置。幸運(yùn)的是,這不是問題,因?yàn)榇笕萘侩娙萜鞲采w的低頻能量對電容器位置不敏感。大容量電容器幾乎可以放置在PCB上的任何地方,但最好的放置位置盡可能靠近FPGA。電容器安裝應(yīng)遵循正常的印刷電路板布局做法,傾向于短和寬的形狀連接到多通孔的電源平面。

0805和0603陶瓷電容器

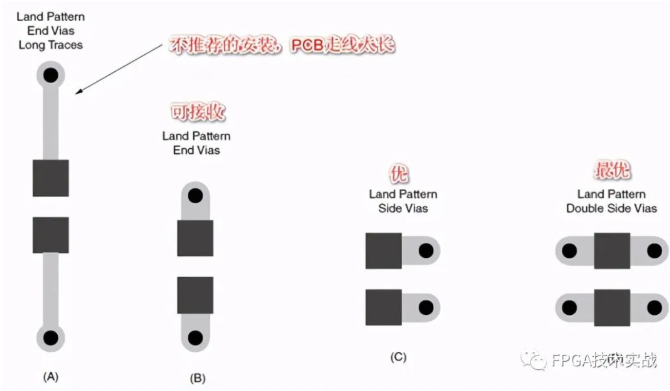

0805和0603電容覆蓋中頻范圍。位置對他們的表現(xiàn)有一定的影響。電容器應(yīng)盡可能靠近FPGA。任何放置在器件負(fù)載點(diǎn)兩個(gè)電氣英寸以內(nèi)的位置都是可以接受的。電容安裝(焊盤、走線和過孔)應(yīng)針對低電感進(jìn)行優(yōu)化。過孔應(yīng)直接與焊盤對接。通孔可以位于焊盤的端部(見圖1-1B),但最好位于焊盤的側(cè)面(見圖1-1C)。焊盤側(cè)面的通孔位置通過增加一個(gè)通孔與另一個(gè)通孔之間的互感耦合來降低安裝的總寄生電感。雙通孔可以放置在焊盤的兩側(cè)(見圖1-1D),以獲得更低的寄生電感,大封裝電容(1206或以上封裝)推薦兩側(cè)放置通孔或者放置大通孔。

圖1-1:電容器接地和安裝幾何形狀示例

2 PDS基本原理

本小節(jié)討論了PDS的用途及其組成部分的性質(zhì),還描述了電容器放置、電容器安裝、PCB幾何結(jié)構(gòu)和PCB堆疊方面的建議。

2.1 噪聲限值

正如系統(tǒng)中的器件對電源系統(tǒng)消耗的電流大小有要求一樣,對電源系統(tǒng)的純凈度也有要求。此純凈度要求規(guī)定了電源上存在的最大噪聲量。大多數(shù)數(shù)字器件,包括所有7系列FPGA,要求VCC電源的波動(dòng)不超過器件數(shù)據(jù)表中規(guī)定的規(guī)格。

數(shù)字器件消耗的功率隨時(shí)間而變化,并且這種變化發(fā)生在所有頻率標(biāo)度上,因此需要寬帶PDS來維持電壓穩(wěn)定。

功耗的低頻變化通常是器件或大部分設(shè)備啟用或禁用的結(jié)果。這種差異發(fā)生在從毫秒到天的時(shí)間范圍內(nèi)。

功率消耗的高頻變化是器件內(nèi)部單個(gè)開關(guān)事件的結(jié)果。這發(fā)生在時(shí)鐘頻率和時(shí)鐘頻率的前幾個(gè)諧波的尺度上,高達(dá)約5Ghz。

由于VCC的電壓電平是固定的,所以不斷變化的功率需求表現(xiàn)為不斷變化的電流需求。PDS必須在電源電壓變化盡可能小的情況下適應(yīng)這些電流消耗的變化。

當(dāng)器件中的電流消耗發(fā)生變化時(shí),PDS無法立即響應(yīng)該變化。因此,在PDS響應(yīng)之前,設(shè)備上的電壓會(huì)發(fā)生短暫的變化。導(dǎo)致這種PDS滯后的兩個(gè)主要原因與PDS的兩個(gè)主要部件相對應(yīng):電壓穩(wěn)壓器和去耦電容器。

PDS的第一個(gè)主要部件是電壓穩(wěn)壓器。電壓穩(wěn)壓器觀察其輸出電壓并調(diào)整其提供的電流大小,以保持輸出電壓恒定。大多數(shù)常見的電壓穩(wěn)壓器在毫秒到微秒之間進(jìn)行這種調(diào)整。電壓穩(wěn)壓器有效地維持從直流到幾百kHz的所有頻率事件的輸出電壓,這取決于穩(wěn)壓器(有些在低MHz下有效調(diào)節(jié))。對于頻率高于此范圍的瞬態(tài)事件,在穩(wěn)壓器響應(yīng)新的電流需求水平之前存在一個(gè)時(shí)間滯后。

例如,如果器件的電流需求在幾百皮秒內(nèi)增加,器件上的電壓會(huì)下降一定量,直到穩(wěn)壓器能夠調(diào)整到新的、更高水平的所需電流。這種滯后可以持續(xù)幾微秒到幾毫秒。在這段時(shí)間內(nèi),需要另一個(gè)元件來代替穩(wěn)壓器,以防止電壓下降。

第二個(gè)主要的PDS部件是去耦電容器(也稱為旁路電容器)。去耦電容器作為器件的局部儲(chǔ)能。電容器不能提供直流電,因?yàn)樗粌?chǔ)存少量的能量(穩(wěn)壓器提供直流電)。當(dāng)?shù)氐哪茉磧?chǔ)存應(yīng)該對當(dāng)前不斷變化的需求做出非常迅速的反應(yīng)。電容器有效地保持電源電壓在數(shù)百KHz至數(shù)百M(fèi)Hz的頻率(毫秒至納秒范圍)。分立去耦電容器對于發(fā)生在該范圍以上或以下的事件沒有用處。

例如,如果器件中的電流需求在幾皮秒內(nèi)增加,那么器件上的電壓會(huì)下降一定量,直到電容器能夠向器件提供額外的電荷。如果器件中的電流需求在數(shù)毫秒內(nèi)保持這一新水平,穩(wěn)壓器電路與去耦電容器并聯(lián)工作,通過改變電容器的輸出來替代電容器,以提供新的電流水平。

圖1-2顯示了PDS的主要組件:穩(wěn)壓器、去耦電容器和有源器件(FPGA)。

圖1-3顯示了一個(gè)簡化的PDS電路,其所有負(fù)載功耗由一個(gè)頻率相關(guān)電阻器表示。

2.2 電感特性

電感是電容器和PCB電流通路的特性,可以減緩電流的變化。電感使電容器不能對瞬態(tài)電流或頻率高于其有效范圍的變化作出瞬時(shí)響應(yīng)的原因。

PDS由一個(gè)穩(wěn)壓器和多級去耦電容器組成,可滿足設(shè)備電流需求,并在必要時(shí)快速響應(yīng)電流瞬變,以將電壓維持在規(guī)定范圍內(nèi)。當(dāng)這些電流需求得不到滿足時(shí),設(shè)備電源上的電壓就會(huì)發(fā)生變化。這被視為噪聲。電容器電流路徑中的電感應(yīng)最小化,因?yàn)樗璧K了去耦電容器快速響應(yīng)不斷變化的電流需求的能力。

電感發(fā)生在FPGA器件和電容器之間以及電容器和穩(wěn)壓器之間(見圖2-2)。這些寄生電感存在于電容器和所有PCB電流路徑中。重要的是要盡量減少這些寄生電感。

2.3 電容寄生電感

電容值通常被認(rèn)為是電容器最重要的特性。在電源系統(tǒng)應(yīng)用中,寄生電感(ESL)具有相同或更大的重要性。電容器封裝尺寸決定了寄生電感的大小。小封裝電容器通常具有比大封裝電容器更低的寄生電感。

去耦電容器的選擇要求:

對于特定的電容值,選擇可用的最小封裝。

對于特定的封裝尺寸(基本上是固定的電感值),選擇該封裝中可用的最高電容值。

表面貼裝芯片電容器是可用的最小電容器,是分散去耦電容器的良好選擇:

對于從100μF到非常小的值(如0.01μF),通常使用X7R或X5R型陶瓷電容器。這些電容器具有低寄生電感和低ESR,具有可接受的溫度特性。

對于較大的值,如47μF至1000μF,通常使用鉭電容器。這些電容器具有較低的寄生電感和中等的ESR,使其具有較低的Q因數(shù),因此有效頻率范圍非常廣。

如果鉭電容器不可用或無法使用,則可以使用低ESR、低電感電解電容器,前提是它們具有相當(dāng)?shù)腅SR和ESL。其他具有類似特性的新技術(shù)也可用(Os-Con、POSCAP和聚合物電解SMT)。

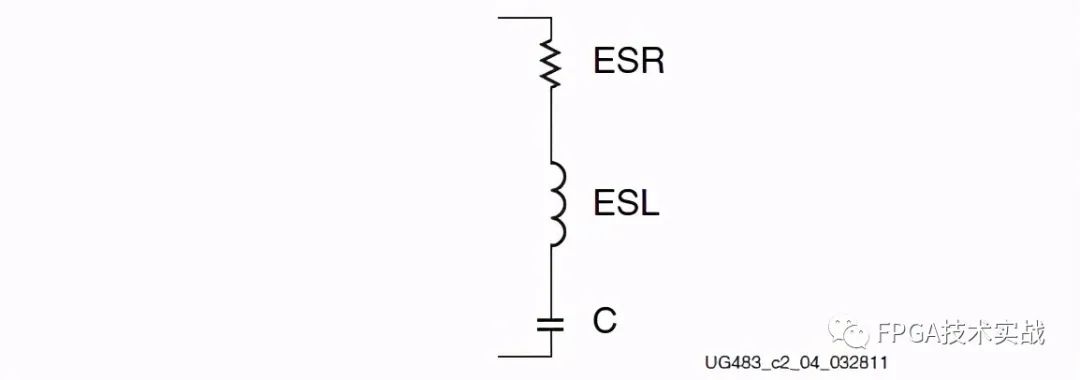

任何類型的實(shí)際電容器不僅具有電容特性,而且具有電感和電阻特性。圖1-4顯示了實(shí)際電容器的寄生模型。一個(gè)真正的電容器應(yīng)該被視為RLC電路(一個(gè)由電阻(R)、電感器(L)和電容器(C)串聯(lián)而成的電路)。

圖1-4:真實(shí)、非理想電容器的寄生

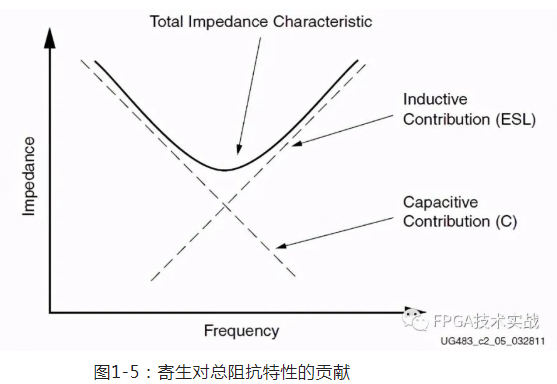

圖1-5顯示了實(shí)際電容器的阻抗特性。在這個(gè)圖上疊加的是電容器電容和寄生電感(ESL)的對應(yīng)曲線。這兩條曲線結(jié)合起來形成RLC電路的總阻抗特性。

隨著電容值的增加,電容曲線向下和向左移動(dòng)。隨著寄生電感的減小,電感曲線向下向右移動(dòng)。因?yàn)樘囟ǚ庋b中電容器的寄生電感是固定的,所以特定封裝中電容器的電感曲線保持不變。

由于在同一個(gè)封裝中選擇了不同的電容值,電容曲線相對于固定電感曲線上下移動(dòng),如圖1-6所示。

通過增加電容器的值可以降低低頻電容器的阻抗;通過減小電容器的電感可以降低高頻電容器的阻抗。雖然可以在固定封裝中指定更高的電容值,但如果不并聯(lián)更多的電容器,則不可能降低電容器(在固定封裝中)的電感。并聯(lián)使用多個(gè)電容器將寄生電感相除,同時(shí)將電容值相乘。這同時(shí)降低了高頻和低頻阻抗。

2.4 PCB電流通路電感

PCB中電流路徑的寄生電感有三個(gè)不同的來源:

電容器安裝

PCB電源和接地層

FPGA安裝

電容安裝電感

電容器安裝指的是電容器在PCB上的焊盤,焊盤和通孔之間的走線(如果有的話),以及通孔。

兩端電容器的通孔、走線和電容器安裝焊盤根據(jù)具體的幾何結(jié)構(gòu)產(chǎn)生的電感在300 pH到4 nH之間。

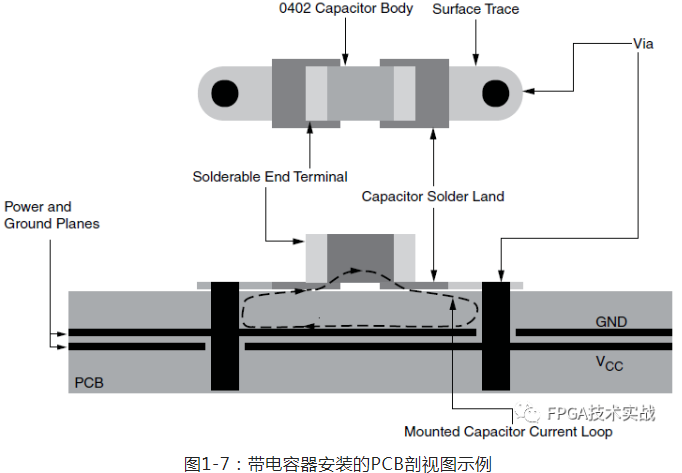

因?yàn)殡娏魍返碾姼信c電流所經(jīng)過的回路面積成正比,所以使回路尺寸最小化是很重要的。回路包括通過一個(gè)電源平面的路徑,向上通過一個(gè)通孔,通過連接走線到接地,通過電容器,通過另一個(gè)接地和連接走線,向下通過另一個(gè)通孔,然后進(jìn)入另一個(gè)平面,如圖1-7所示。

連接走線長度對安裝的寄生電感有很大影響,如果使用,應(yīng)盡可能短和寬。在可能的情況下,不應(yīng)使用連接走線,通過過孔直接下地。將過孔放置在電容器接地的一側(cè)或?qū)⑦^孔數(shù)量增加一倍,進(jìn)一步降低了安裝的寄生電感。

一些PCB制造工藝允許焊盤中的通孔幾何形狀,這是減少寄生電感的一種選擇。對于超低電感電容器,每個(gè)焊盤使用多個(gè)通孔是很重要的,例如在電容器體的側(cè)面而不是端部放置寬端子的反向縱橫比電容器。

PCB布局工程師通常試圖通過在多個(gè)電容器之間共享通孔來將更多的部件擠壓到一個(gè)小區(qū)域中。在任何情況下都不應(yīng)該使用此技術(shù)。當(dāng)?shù)诙€(gè)電容器連接到現(xiàn)有電容器的電容器時(shí),PDS的改善非常小。

電容器安裝(接地、走線和過孔)通常貢獻(xiàn)的電感量與電容器自身的寄生自感量大致相同或更多。

參考層電感

一些電感與PCB電源和接地層有關(guān)。這些平面的幾何形狀決定了它們的電感。

電流在電源和接地層中從一點(diǎn)流向另一點(diǎn)時(shí)會(huì)擴(kuò)散(由于類似于集膚效應(yīng)的特性)。平面內(nèi)的電感可描述為擴(kuò)展電感,單位為亨利每平方。決定電感量的是一個(gè)平面截面的形狀,而不是尺寸。

擴(kuò)展電感的作用和其他電感一樣,可以抵抗電源平面(導(dǎo)體)中電流量的變化。電感延遲了電容器對FPGA器件瞬態(tài)電流的響應(yīng)能力,因此應(yīng)盡可能減少有可能。因?yàn)樵O(shè)計(jì)者對平面X-Y形狀的控制是有限的,唯一可控的因素是擴(kuò)展電感值。這取決于將電源面與其相關(guān)地平面分開的電介質(zhì)的厚度。

在高頻配電系統(tǒng)中,電源和地平面成對工作,電感相互獨(dú)立共存。電源和低平面之間的間距決定了擴(kuò)展電感。間距越近(電介質(zhì)越薄),擴(kuò)展電感越低。FR4介質(zhì)不同厚度的擴(kuò)展電感近似值見表2-10。

表2-10:FR4電源接地平面不同厚度的電容和擴(kuò)展電感值

擴(kuò)展電感的減小對應(yīng)于VCC和GND的更近間距。然而,由于7系列FPGA中存在基板去耦電容,因此PCB去耦電容所需的快速瞬態(tài)電流量是有限的。這意味著低于50μ(2 mil)的介電厚度幾乎沒有好處。VCC和GND層之間50μ或75μ的介電厚度足以滿足7系列FPGA的要求。

除了提供低電感電流路徑外,電源和接地參考平面還提供一些高頻去耦電容。隨著平面面積的增加和電源與接地平面之間的間距的減小,該電容的值增加。電容每平方英寸見表2-10。然而,考慮到7系列FPGA中存在的襯底去耦電容,這些PCB電源-接地平面對產(chǎn)生的電容量通常是無關(guān)緊要的。

FPGA安裝電感

連接FPGA電源引腳(VCC和GND)的PCB焊盤和過孔為整個(gè)電源電路貢獻(xiàn)了大量寄生電感。

相關(guān)通孔長度是在FPGA焊盤和相關(guān)VCC或GND平面之間承載瞬態(tài)電流的通孔部分。任何剩余的通孔(在電源板和PCB背面之間)都會(huì)影響通孔的寄生電感(焊盤和電源板之間的通孔越短,寄生電感越小)。通過保持相關(guān)VCC和GND平面盡可能靠近FPGA(靠近PCB堆疊頂部),F(xiàn)PGA安裝中的寄生通孔電感減小。

器件引腳布置決定了反向電流路徑彼此之間的接近程度。電感與任何兩個(gè)相反的電流相關(guān)聯(lián)(例如,通過對在VCC和GND中流動(dòng)的電流)。兩條相反路徑之間的高度互感耦合降低了回路的總電感。因此,在選擇時(shí),VCC和GND過孔應(yīng)盡可能靠近。

FPGA下的通孔場有許多VCC和GND通孔,總電感是一個(gè)通孔與另一個(gè)通孔接近度的函數(shù):

對于核心VCC電源(VCCINT和VCCAUX),VCC和GND引腳之間存在反向電流。

對于I/O VCC電源(VCCO),反向電流位于任何I/O及其回流路徑之間。

無論是由VCCO還是GND引腳承載。為了減少寄生電感:

核心VCC引腳(如VCCINT和VCCAUX)以棋盤形式放置在引腳中。

VCCO和GND引腳分布在I/O引腳之間。

7系列FPGA引腳中的每個(gè)I/O引腳都與一個(gè)返回電流引腳相鄰。FPGA引腳排列決定PCB的通孔排列。PCB設(shè)計(jì)者不能控制反向的電流路徑,但可以控制電容器的安裝電感和FPGA的安裝電感之間的權(quán)衡:

通過將電源面靠近PCB疊層的上半部分并將電容器放置在上表面(減少電容器的通孔長度),兩種安裝電感都減小。

如果電源板放置在PCB堆疊的下半部分,電容器必須安裝在PCB背面。在這種情況下,F(xiàn)PGA安裝過孔已經(jīng)很長了,而使電容器過孔變長(從上表面下來)是一種不好的做法。更好的做法是利用PCB外側(cè)和感興趣的電源平面之間的短距離,在外側(cè)安裝電容器。

PCB層疊和順序

VCC和GND平面在PCB堆疊中的放置(層順序)對電源電流路徑的寄生電感有重要影響。必須在設(shè)計(jì)過程的早期考慮層疊順序:

高優(yōu)先級電源應(yīng)靠近FPGA(在PCB堆疊的上半部分)

低優(yōu)先級電源應(yīng)放置在離FPGA較遠(yuǎn)的位置(PCB堆疊的下半部分)

具有高瞬態(tài)電流的電源應(yīng)靠近PCB堆疊的頂面(FPGA側(cè))相關(guān)的VCC平面。這減少了電流在到達(dá)相關(guān)VCC和GND平面之前的垂直距離(VCC和GND通過長度)。為了減少擴(kuò)展電感,每個(gè)VCC平面都應(yīng)該在PCB堆疊中有一個(gè)相鄰的GND平面。趨膚效應(yīng)導(dǎo)致高頻電流緊密耦合,并且與特定VCC平面相鄰的GND平面趨向于攜帶與VCC平面中的電流互補(bǔ)的大部分電流。因此,相鄰的VCC和GND平面被視為一對。

并非所有VCC和GND平面對都位于PCB堆疊的上半部分,因?yàn)橹圃煜拗仆ǔR髧@中心對稱的PCB堆疊(相對于介質(zhì)厚度和蝕刻銅區(qū)域)。PCB設(shè)計(jì)人員選擇VCC和GND平面對的優(yōu)先級:高優(yōu)先級對攜帶高瞬態(tài)電流并放置在堆棧的高位置,而低優(yōu)先級對攜帶較低瞬態(tài)電流(或可以容忍更多噪聲)并放置在堆棧的低位置。

2.5 電容有效頻率

每個(gè)電容器都有一個(gè)很窄的頻帶,作為去耦電容器最有效。該頻帶以電容器的自諧振頻率FRSELF為中心。一些電容器的有效頻帶比其他電容器寬。電容器的ESR決定電容器的品質(zhì)(Q)因數(shù),Q因數(shù)可以決定有效頻帶的寬度:

鉭電容器通常具有非常寬的有效頻帶。

ESR較低的陶瓷片式電容器,通常有效頻帶非常窄。

理想電容器只有電容特性,而實(shí)際的非理想電容器也有寄生電感(ESL)和寄生電阻(ESR)。這些寄生電路串聯(lián)工作,形成RLC電路(圖2-4)。RLC電路的諧振頻率是電容器的自諧振頻率。

要確定RLC電路的諧振頻率,請使用公式2-1:

(式2-1)

(式2-1)

確定自諧振頻率的另一種方法是在等效RLC電路的阻抗曲線上尋找最小點(diǎn)。阻抗曲線可以通過頻率掃描在SPICE中計(jì)算或生成。有關(guān)計(jì)算阻抗曲線的其他方法,請參見“模擬方法”部分。

當(dāng)電容器是系統(tǒng)的一部分時(shí),區(qū)分電容器的自諧振頻率和安裝電容器的有效諧振頻率是很重要的。這相當(dāng)于電容器的諧振頻率及其寄生電感,加上電容器和FPGA之間的通孔、平面和連接走線的電感。

電容器的自諧振頻率FRSELF(電容器數(shù)據(jù)表值)遠(yuǎn)高于其在系統(tǒng)中的有效安裝諧振頻率FRIS。由于安裝電容器的性能是最重要的,安裝諧振頻率是用來評估電容器作為更大的PDS的一部分。

安裝寄生電感是電容器自身寄生電感和以下電感的組合:PCB焊盤、連接走線、過孔和電源平面。當(dāng)電容器安裝在PCB背面時(shí),過孔穿過整個(gè)PCB堆疊到設(shè)備。對于成品厚度為1.524 mm(60 mils)的電路板,這些過孔貢獻(xiàn)大約300 pH到1500 pH(電容器的安裝寄生電感,LMOUNT),具體取決于過孔之間的間距。較寬間距的通孔和較厚板中的通孔具有較高的電感。

為了確定電容器在系統(tǒng)中的總寄生電感LIS,將電容器的寄生電感LSELF加到安裝的寄生電感LMOUNT上:

去耦電容器在其諧振頻率附近的窄帶最有效,因此,在選擇電容器集合來建立去耦網(wǎng)絡(luò)時(shí),必須檢查諧振頻率。也就是說,電容器可以在比其諧振頻率高得多和低得多的頻率下有效。回想一下,相同封裝中不同值的電容器具有相同的電感曲線。如圖2-6所示,對于沿曲線感應(yīng)部分的任何給定頻率,電容器都是等效的。

2.6 電容反諧振

與FPGA的PDS中的電容器組合相關(guān)的一個(gè)問題是PDS組合阻抗中的反共振尖峰。產(chǎn)生這些尖峰的原因是PDS中的儲(chǔ)能元件(固有電容、離散電容、寄生電感以及電源和接地層)的不良組合。

配電系統(tǒng)的任何兩個(gè)連續(xù)級之間都可能出現(xiàn)反諧振,例如高頻PCB電容器和PCB平面電容器之間。電源和接地板的面間電容通常具有高Q系數(shù)。如果高頻PCB電容器也為高Q值,則高頻離散電容器與平面電容器之間的交叉點(diǎn)可能出現(xiàn)高阻抗反諧振峰。如果FPGA在這個(gè)頻率有一個(gè)高的瞬態(tài)電流需求(作為一個(gè)刺激),一個(gè)大的噪聲電壓可能會(huì)發(fā)生。

為了糾正這類問題,必須改變高頻離散電容器的特性或VCC和接地層的特性,或者將FPGA活動(dòng)轉(zhuǎn)移到遠(yuǎn)離諧振的不同頻率。

2.7 電容器放置背景

為了實(shí)現(xiàn)去偶功能,電容器應(yīng)靠近被去偶的器件。FPGA和去耦電容器之間的間距增加了電源和接地層中的電流流動(dòng)距離,并且常常增加了器件和電容器之間的電流路徑電感。

此電流路徑的電感(當(dāng)電流從電容器的VCC側(cè)傳輸?shù)紽PGA的VCC引腳,以及從FPGA的GND引腳傳輸?shù)诫娙萜鞯腉ND側(cè)時(shí),電流跟隨的回路)與回路面積成比例。減小回路面積可以減小電感。縮短器件和去耦電容器之間的距離可以減小電感,從而減少瞬態(tài)電流的阻礙。

FPGA的噪聲源和安裝電容之間的相位關(guān)系決定了電容器的有效性。為了使電容器能夠有效地以特定頻率(例如,電容器的諧振頻率)提供瞬態(tài)電流,基于電流從FPGA到電容器的距離的相位關(guān)系必須在相應(yīng)周期的一小部分之內(nèi)。

電容器的位置決定了電容器和FPGA之間傳輸線互連的長度(在這種情況下,是電源和接地板對)。這種互連線的傳輸延遲是關(guān)鍵因素。

FPGA的噪聲分為一定的頻段,不同尺寸的去耦電容負(fù)責(zé)不同的頻段。因此,電容器的放置要求由每個(gè)電容器的有效頻率決定。

當(dāng)FPGA啟動(dòng)電流需求變化時(shí),它會(huì)在PDS電壓(電源和接地層中的一個(gè)點(diǎn))中引起一個(gè)小的局部擾動(dòng)。在能夠抵消這一點(diǎn)之前,去耦電容器必須首先感應(yīng)到一個(gè)電壓差。在FPGA電源引腳的干擾開始和電容器感應(yīng)到干擾的點(diǎn)之間會(huì)出現(xiàn)一個(gè)有限的時(shí)間延遲(等式2-6)。

(式2-6)

(式2-6)

可忽略的能量傳輸?shù)紽PGA,放置距離大于需求頻率波長的四分之一。

傳輸?shù)紽PGA的能量從四分之一波長的0%增加到零距離的100%。

當(dāng)電容器放置在FPGA電源引腳四分之一波長的一小部分時(shí),能量從電容器有效地傳輸?shù)紽PGA。這個(gè)分?jǐn)?shù)應(yīng)該很小,因?yàn)殡娙萜髟诟哂谄渲C振頻率的某些頻率(較短波長)下也有效。

四分之一波長的十分之一對于大多數(shù)實(shí)際應(yīng)用來說是一個(gè)很好的目標(biāo),并導(dǎo)致將電容器放置在其去耦的電源管腳波長的四十分之一以內(nèi)。波長對應(yīng)于電容器的諧振頻率FRIS。

2.8 VREF濾波電容器

在VREF電源穩(wěn)壓中,每個(gè)引腳一個(gè)電容器放置在盡可能靠近VREF引腳的位置。使用的電容器在0.022μF–0.47μF范圍內(nèi)。VREF電容器的主要功能是降低VREF節(jié)點(diǎn)阻抗,從而減少串?dāng)_耦合。自身不需要低頻能量,不需要更大的電容器。

這僅適用于不使用內(nèi)部VREF的情況。內(nèi)部VREF是7系列FPGA中的一個(gè)特性,其中參考電壓軌在內(nèi)部生成,這反過來又允許VREF引腳用作常規(guī)I/O引腳。有關(guān)內(nèi)部VREF的更多詳細(xì)信息,請參閱UG471,7系列FPGA選擇用戶指南。

2.9 電源供電考慮

在7系列FPGA設(shè)計(jì)中,允許從公共PCB平面為1.8V VCCO、VCCAUX和VCCAUX IO供電。但是,必須仔細(xì)考慮電源噪聲,特別是VCCO軌道上的任何噪聲不應(yīng)違反VCCAUX電源的推薦工作條件范圍。見DS182,Kintex-7 FPGA數(shù)據(jù)頁碼:DC和開關(guān)特性和DS183,Virtex?-7 FPGA數(shù)據(jù)表:這些要求的直流和開關(guān)特性。

2.10 未連接的VCCO引腳

在某些情況下,不使用FPGA中的一個(gè)或多個(gè)I/O組(例如,當(dāng)FPGA的I/O管腳遠(yuǎn)遠(yuǎn)超過設(shè)計(jì)要求時(shí))。在這些情況下,可能需要保持Bank的相關(guān)VCCO引腳未連接,因?yàn)檫@樣可以釋放一些PCB布局限制。將未使用的I/O組的VCCO引腳保持在浮動(dòng)狀態(tài)會(huì)降低這些引腳和Bank中I/O引腳的ESD保護(hù)級別。為了在未使用的組中實(shí)現(xiàn)最大的ESD保護(hù),該組中的所有VCCO和I/O引腳應(yīng)連接到同一電位,無論是接地電位、有效VCCO電壓還是浮動(dòng)平面。

3 PDS仿真方法

從非常簡單到非常復(fù)雜的各種模擬方法都可以用來預(yù)測PDS的特性。如果不使用相當(dāng)復(fù)雜的模擬器和花費(fèi)大量時(shí)間,很難獲得準(zhǔn)確的模擬結(jié)果。

基本集總RLC仿真是最簡單的仿真方法之一。雖然它不能解釋PDS的分布特性,但它是選擇和驗(yàn)證去耦電容值組合不會(huì)導(dǎo)致大的反共振的有用工具。集總RLC仿真是建立去偶網(wǎng)絡(luò)等效性的一種好方法,例如評估表2-5中電容器的替代方案。

集總RLC仿真可以在SPICE或其他電路模擬器中進(jìn)行,也可以使用數(shù)學(xué)工具M(jìn)athCAD或microsoftexcel進(jìn)行。Istvan Novak在他的網(wǎng)站上發(fā)布了一個(gè)免費(fèi)的Excel電子表格,用于集中RLC模擬(以及PDS模擬的其他有用工具),工具下載:

http://www.electrical-integrity.com

表1-6還列出了一些用于PDS設(shè)計(jì)和仿真的EDA工具供應(yīng)商。這些工具涵蓋了廣泛的復(fù)雜度級別。

表1-6:用于PDS設(shè)計(jì)和仿真的EDA工具

4 PDS測量

測量可用于確定PDS是否滿足設(shè)計(jì)要求。PDS噪聲測量是一項(xiàng)獨(dú)特的任務(wù),許多專門的技術(shù)已經(jīng)被開發(fā)出來開發(fā)了。本節(jié)小節(jié)介紹噪聲幅度和噪聲頻譜測量。

4.1 噪聲幅度測量

噪聲測量必須使用高帶寬示波器(至少3 GHz示波器和1.5 GHz探頭或直接同軸連接)在實(shí)際運(yùn)行的設(shè)計(jì)上進(jìn)行測試。在設(shè)備的電源引腳或未使用的I/O驅(qū)動(dòng)高或低(稱為間諜孔測量)處進(jìn)行測量。

VCCINT和VCCAUX只能在PCB背面過孔處測量。VCCO也可以用這種方法測量,但是通過測量感興趣的Bank中未使用的I/O的靜態(tài)(固定邏輯電平)信號可以獲得更準(zhǔn)確的結(jié)果。

在PCB背面進(jìn)行噪聲測量時(shí),必須考慮測量點(diǎn)與FPGA之間路徑中的過孔寄生特性。示波器測量中不考慮此路徑中出現(xiàn)的任何電壓降。

PCB背面通孔測量也有一個(gè)潛在的問題:去耦電容器通常直接安裝在FPGA器件下方,這意味著電容器接地直接連接到VCC和GND通孔,并帶有表面走線。這些電容器就像對高頻交流電流短路一樣,混淆了測量結(jié)果。為確保測量結(jié)果不會(huì)被電容器短路,請?jiān)跍y量現(xiàn)場移除電容器(保留所有其他電容器以反映真實(shí)的系統(tǒng)行為)。

測量VCCO噪聲時(shí),可在配置為邏輯1或邏輯0驅(qū)動(dòng)器的I/O引腳處進(jìn)行測量。在大多數(shù)情況下,此“間諜孔”應(yīng)使用與Bank中其他信號相同的I/O標(biāo)準(zhǔn)。測量靜態(tài)邏輯0時(shí),會(huì)顯示在受害者身上產(chǎn)生的串?dāng)_(通過場、PCB布線、封裝布線)。測量靜態(tài)邏輯1會(huì)顯示所有相同的串?dāng)_分量以及I/O組VCCO網(wǎng)絡(luò)上存在的噪聲。通過從靜態(tài)邏輯1上測得的噪聲減去(時(shí)間上相干地)靜態(tài)邏輯0上測得的噪聲,可以查看VCCO上的噪聲。為了獲得準(zhǔn)確的結(jié)果,必須在相同的I/O位置測量靜態(tài)邏輯0和靜態(tài)邏輯1噪聲。這意味著存儲(chǔ)來自兩個(gè)邏輯狀態(tài)的時(shí)域波形信息,并在后處理數(shù)學(xué)計(jì)算工具(如MATLAB或Excel)中對兩個(gè)波形執(zhí)行減法運(yùn)算。

示波器測量方法

使用示波器查看電源系統(tǒng)噪聲有兩種基本方法,每種方法的用途不同。第一種方法調(diào)查所有可能的噪聲事件,而第二種方法有助于關(guān)注單個(gè)噪聲源。

將示波器置于無限持續(xù)模式,以獲取長時(shí)間(數(shù)秒或數(shù)分鐘)內(nèi)的所有噪聲。如果設(shè)計(jì)工作在許多不同的模式下,使用不同數(shù)量的不同資源,這些不同的條件和模式應(yīng)該在示波器獲取噪聲測量時(shí)工作。

將示波器置于平均模式并觸發(fā)已知的攻擊者事件。這個(gè)可以顯示與攻擊者事件相關(guān)的噪聲量(與攻擊者異步的任何事件都將通過平均值消除)。

電源系統(tǒng)噪聲測量應(yīng)在幾個(gè)不同的FPGA位置進(jìn)行,以確保捕捉到任何局部噪聲現(xiàn)象。

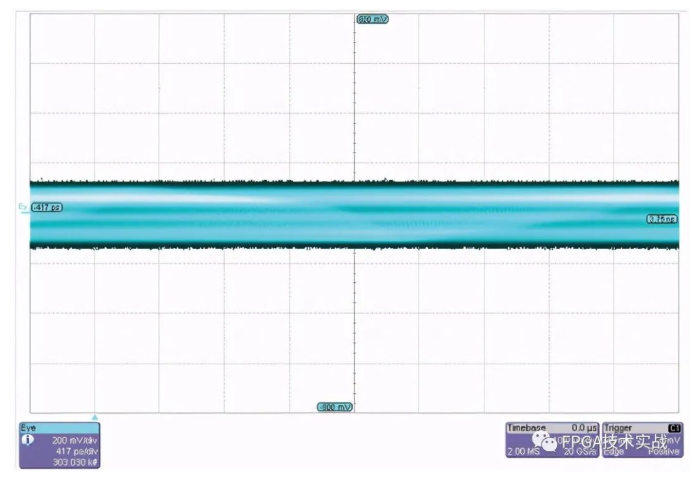

圖1-8顯示了樣品設(shè)計(jì)的VCCO引腳處進(jìn)行的平均噪聲測量。在本例中,觸發(fā)器是I/O總線接口以250MB/s的速度發(fā)送1-0-1-0模式的時(shí)鐘。

圖1-8、250Mb/s下具有多個(gè)I/O發(fā)送模式的VCCO電源的平均噪聲測量

圖1-9顯示了具有更廣泛I/O活動(dòng)的相同設(shè)計(jì)的無限持久性噪聲測量。由于無限持久性測量捕捉到長時(shí)間內(nèi)的所有噪聲事件,包括與主要入侵者相關(guān)和不相關(guān)的噪聲事件,因此顯示了所有電源系統(tǒng)偏移。

圖1-9:同一位置的無限持久性電源噪聲測量

4.2 噪聲頻譜測量

有必要的信息來改善去偶網(wǎng)絡(luò)需要額外的測量。為了確定噪聲存在的頻率,噪聲功率譜測量是必要的。頻譜分析儀或與FFT數(shù)學(xué)功能相結(jié)合的高帶寬示波器可以實(shí)現(xiàn)這一點(diǎn)。

FFT數(shù)學(xué)函數(shù)可以內(nèi)置在示波器中,但是,其中許多函數(shù)的分辨率不足以給出噪聲頻譜的清晰圖像。或者,可以從示波器捕獲長序列的時(shí)域數(shù)據(jù),并使用MATLAB或其他支持的后處理軟件將其轉(zhuǎn)換為頻域,這種方法的優(yōu)點(diǎn)是顯示用戶愿意處理的盡可能多的分辨率。如果兩個(gè)數(shù)學(xué)容量都不可用,則可以通過目視檢查時(shí)域波形和估計(jì)噪聲中存在的單個(gè)周期來近似噪聲頻率內(nèi)容。

頻譜分析儀是一種頻域儀器,顯示輸入端電壓信號的頻率成分。使用頻譜分析儀,用戶可以看到PDS不滿足要求的具體頻率。

特定頻率的過大噪聲表示PDS阻抗對于設(shè)備的瞬態(tài)電流需求過高的頻率。利用這些信息,設(shè)計(jì)者可以修改PDS以適應(yīng)特定頻率下的瞬態(tài)電流。這是通過增加有效頻率接近噪聲頻率的電容器或降低臨界頻率處的PDS阻抗來實(shí)現(xiàn)的。

噪聲頻譜測量應(yīng)采用與峰間噪聲測量相同的方式,直接在FPGA器件下方,或在靜態(tài)I/O驅(qū)動(dòng)的高或低位置進(jìn)行。頻譜分析儀使用50Ω電纜而不是有源探頭進(jìn)行測量。

一個(gè)好的方法是通過同軸連接器將測量電纜連接到靠近設(shè)備的電源和接地層中。這在大多數(shù)情況下不可用。

另一種方法是將測量電纜連接在已拆除設(shè)備附近的去耦電容器的焊盤上。電纜的中心導(dǎo)體和屏蔽層直接焊接到電容器接地上。或者,可以使用帶有50Ω RF探頭的探頭站來接觸去耦電容器焊盤。

為了保護(hù)頻譜分析儀敏感的前端電路,在線路上增加一個(gè)直流隔離電容器或衰減器。這將頻譜分析儀與器件電源電壓隔離。

圖1-10是VCCO電源噪聲的噪聲頻譜測量示例,在100 MHz下具有多個(gè)I/O發(fā)送模式。

4.3 優(yōu)化去偶網(wǎng)絡(luò)

如果需要一個(gè)高度優(yōu)化的PDS,原型系統(tǒng)的測量和仿真可以為PDS的設(shè)計(jì)提供信息。利用原型系統(tǒng)產(chǎn)生的噪聲頻譜知識和系統(tǒng)阻抗知識,可以確定和調(diào)節(jié)設(shè)計(jì)的唯一暫態(tài)電流。

要測量工作條件下設(shè)計(jì)的噪聲頻譜,請使用頻譜分析儀或帶FFT的示波器。電源系統(tǒng)阻抗可以通過直接測量或仿真來確定,也可以通過這兩種方法的結(jié)合來確定,因?yàn)橥ǔ4嬖谠S多變量和未知量。

噪聲頻譜和阻抗都是頻率的函數(shù)。通過檢查每個(gè)頻率點(diǎn)的商,計(jì)算瞬態(tài)電流作為頻率的函數(shù)(式2-7):

(式2-7)

(式2-7)

利用數(shù)據(jù)表的最大電壓紋波值,可以確定所有頻率下所需的阻抗值。這就產(chǎn)生了一個(gè)目標(biāo)阻抗作為頻率的函數(shù)。一個(gè)特殊設(shè)計(jì)的電容網(wǎng)絡(luò)可以容納特定設(shè)計(jì)的暫態(tài)電流。

5 故障排除

在某些情況下,適當(dāng)?shù)脑O(shè)計(jì)工作提前完成,但噪聲問題仍然存在。這一節(jié)將介紹可能出現(xiàn)的問題和建議的解決方法。

可能性1:噪聲來自PCB上其他器件

有時(shí)接地和/或電源面在許多器件之間共享,并且來自未充分去偶器件的噪聲影響其他器件上的PDS。產(chǎn)生這種噪音的常見原因有:

RAM接口具有固有的高瞬態(tài)電流需求,這是由臨時(shí)周期爭用或高電流驅(qū)動(dòng)器引起的

大型ASIC

當(dāng)在這些器件上本地測量到不可接受的噪聲量時(shí),應(yīng)分析本地PDS和去偶組件網(wǎng)絡(luò)。

可能性2:平面、過孔或走線的寄生電感

有時(shí)去耦網(wǎng)絡(luò)的電容是足夠的,但是從電容到FPGA的路徑中有太多的電容。

可能的原因有:

錯(cuò)誤的去耦電容器連接走線幾何或焊盤幾何

從電容器到FPGA的路徑太長

-和/或-

電源過孔中的電流路徑穿過非常厚的PCB堆疊

對于連接走線幾何和電容器接地幾何的不足,請檢查電流路徑的回路電感。如果去耦電容器的過孔與電路板上的電容焊點(diǎn)相隔幾毫米,則電流回路面積大于所需面積。

為了減少電流回路面積,過孔應(yīng)直接放置在電容器焊盤上。千萬不要用一段走線將過孔連接到焊盤上。

其他幾何結(jié)構(gòu)的改進(jìn)包括焊盤中的通孔(焊盤下方的通孔),以及焊盤旁邊的通孔(通孔跨接焊盤,而不是放置在焊盤的末端)。雙通孔還改善了連接走線幾何結(jié)構(gòu)和電容器接地幾何結(jié)構(gòu)。

特別厚的電路板(>3.2毫米或127mil)具有具有更高寄生電感的通孔。

為了減小寄生電感,將關(guān)鍵的VCC/GND平面”三明治"移動(dòng)到靠近FPGA所在的頂面,并將電容器放置在FPGA所在的頂面上。

可能性3: PCB中的I/O信號比需要的強(qiáng)

如果在改進(jìn)PDS之后VCCO PDS中的噪聲仍然過高,則可以降低I/O接口轉(zhuǎn)換速率和/或驅(qū)動(dòng)強(qiáng)度。這既適用于FPGA的輸出,也適用于FPGA的輸入。在嚴(yán)重的情況下,輸入到FPGA的過沖會(huì)使IOB箝位二極管反向偏置,從而將電流注入VCCO PDS。

如果VCCO上存在大量噪聲,則應(yīng)降低這些接口的驅(qū)動(dòng)強(qiáng)度,或使用不同的終端(在輸入或輸出路徑上)。

可能性4:I/O信號返回電流以次優(yōu)路徑傳輸

I/O信號返回電流也會(huì)導(dǎo)致PDS中的噪聲過大。對于一個(gè)設(shè)備傳輸?shù)絇CB(并最終傳輸?shù)搅硪粋€(gè)設(shè)備)的每個(gè)信號,都有一個(gè)相等且相反的電流從PCB流入設(shè)備的電源/接地系統(tǒng)。如果低阻抗返回電流路徑不可用,則使用不太理想的高阻抗路徑。當(dāng)I/O信號返回電流流過不太理想的路徑時(shí),PDS中會(huì)產(chǎn)生電壓變化,并且信號會(huì)被串?dāng)_破壞。這可以通過確保每個(gè)信號都有一個(gè)緊密間隔且完全完整的返回路徑來改善。糾正次優(yōu)回流路徑的方法:

通過驗(yàn)證的連續(xù)返回電流路徑,將信號限制在較少的路由層。

為交流電流在基準(zhǔn)面之間傳輸提供低阻抗路徑(發(fā)生層轉(zhuǎn)換的PCB位置處的高頻去耦電容器)。

更多信息可以來這里獲取==>>電子技術(shù)應(yīng)用-AET<<