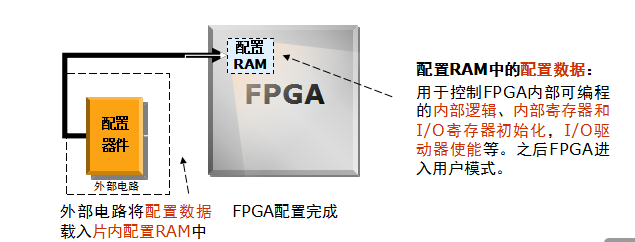

目前,大多數(shù)FPGA芯片是基于 SRAM 的結(jié)構(gòu)的, 而 SRAM 單元中的數(shù)據(jù)掉電就會丟失,因此系統(tǒng)上電后,必須要由配置電路將正確的配置數(shù)據(jù)加載到 SRAM 中,此后 FPGA 才能夠正常的運行。

常見的配置芯片有EPCS 芯片 (EPCS4、EPCS8、EPCS16、EPCS64、EPCS128),還有通用的串行 SPI FLASH 芯片如 M25P40、 M25P16、 W25Q16 等。

配置(configuraTIon)是對FPGA的內(nèi)容進行編程的過程。每次上電后都需要進行配置是基于SRAM工藝FPGA的一個特點,也可以說是一個缺點。FPGA配置過程如下:

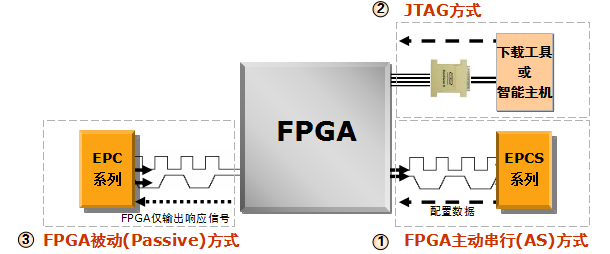

FPGA配置方式

根據(jù)FPGA在配置電路中的角色,可以將配置方式分為三類:

1.FPGA主動串行(AS)方式

2. JTAG方式

3. FPGA被動(Passive)方式

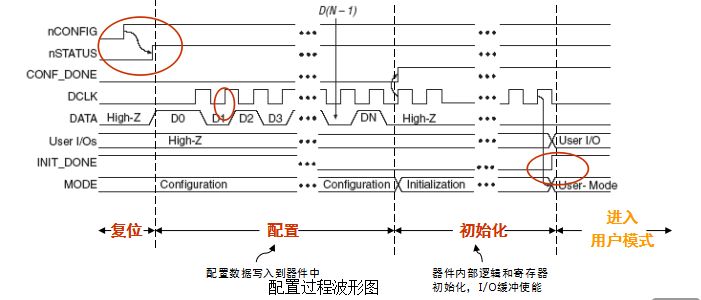

FPGA配置過程

FPGA的配置包括3個階段:復(fù)位、配置和初始化。

FPGA正常上電后,當其nCONFIG管腳被拉低時,器件處于復(fù)位狀態(tài),這時所有的配置RAM內(nèi)容被清空,并且所有I/O處于高阻態(tài),F(xiàn)PGA的狀態(tài)管腳nSTATUS和CONFIG_DONE管腳也將輸出為低。當FPGA的nCONFIG管腳上出現(xiàn)一個從低到高的跳變以后,配置就開始了,同時芯片還會去采樣配置模式(MSEL)管腳的信號狀態(tài),決定接受何種配置模式。

隨之,芯片將釋放漏極開路(open-drain)輸出的nSTATUS管腳,使其由片外的上拉電阻拉高,這樣,就表示FPGA可以接收配置數(shù)據(jù)了。在配置之前和配置過程中,F(xiàn)PGA的用戶I/O均處于高阻態(tài)。

在接收配置數(shù)據(jù)的過程中,配置數(shù)據(jù)由DATA管腳送入,而配置時鐘信號由DCLK管腳送入,配置數(shù)據(jù)在DCLK的上升沿被鎖存到FPGA中,當配置數(shù)據(jù)被全部載入到FPGA中以后,F(xiàn)PGA上的CONF_DONE信號就會被釋放,而漏極開路輸出的CONF_DONE信號同樣將由外部的上拉電阻拉高。因此,CONF_DONE管腳的從低到高的跳變意味著配置的完成,初始化過程的開始,而并不是芯片開始正常工作。

INIT_DONE是初始化完成的指示信號,它是FPGA中可選的信號,需要通過Quartus II工具中的設(shè)置決定是否使用該管腳。在初始化過程中,內(nèi)部邏輯、內(nèi)部寄存器和I/O寄存器將被初始化,I/O驅(qū)動器將被使能。

當初始化完成以后,器件上漏極開始輸出的INIT_DONE管腳被釋放,同時被外部的上拉電阻拉高。這時,F(xiàn)PGA完全進入用戶模式,所有的內(nèi)部邏輯以及I/O都按照用戶的設(shè)計運行,這時,那些FPGA配置過程中的I/O弱上拉將不復(fù)存在。不過,還有一些器件在用戶模式下I/O也有可編程的弱上拉電阻。在完成配置以后,DCLK信號和DATA管腳不應(yīng)該被浮空(floaTIng),而應(yīng)該被拉成固定電平,高或低都可以。

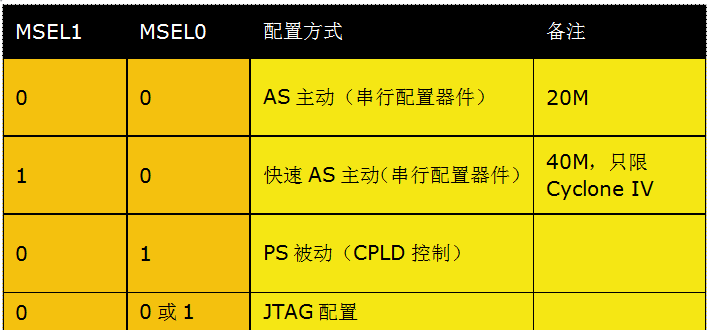

FPGA配置模式選擇

用戶可以通過設(shè)置FPGA上的MSEL0、MESL1兩個引腳的狀態(tài)來選擇配置方式。各種方式的MSEL0、MESL1設(shè)置如下表所列:

說明:

在上表中,如果只采用一種配置方式,則可以直接將MSEL0、MESL1連接到VCC(注意要與FPGA的IO口的供電VCCIO相同)或GND;

如果需要多種配置方式,那么MSEL要用控制器(單片機、CPLD等)來控制以進行切換;

MSEL管腳在配置開始前必須處于一個固定的狀態(tài),因此不能將MSEL管腳懸空。

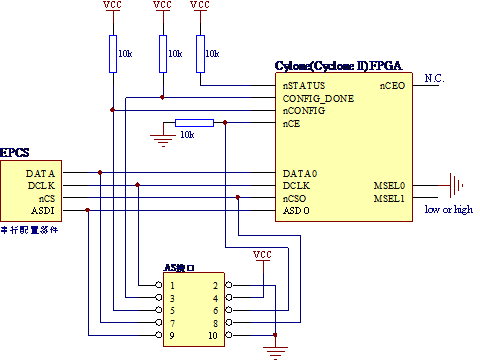

主動串行配置

主動串行配置方式(AS)是將配置數(shù)據(jù)事先存儲在串行配置器件EPCS中,然后在系統(tǒng)上電時Cyclone IV FPGA通過串行接口讀取配置數(shù)據(jù)(如果是壓縮數(shù)據(jù),還會進行解壓縮處理)對內(nèi)部的SRAM單元進行配置。

因為上述配置過程中FPGA控制配置接口,因此通常稱為主動配置方式。在配置期間,Cyclone IV用過串行接口來讀配置數(shù)據(jù),來對里面的SRAM編程。串行配置器件的四個接口包括,串行時鐘輸入DCLK,串行數(shù)據(jù)輸出DATA,低有效的片選信號NCE,串行數(shù)據(jù)輸入ASDI。

主動串行配置電路圖:

因為FPGA上的nSTATUS、CONFIG_DONE管腳都是開漏結(jié)構(gòu),所以都要接上拉電阻。FPGA的片選腳nCE必須接地。

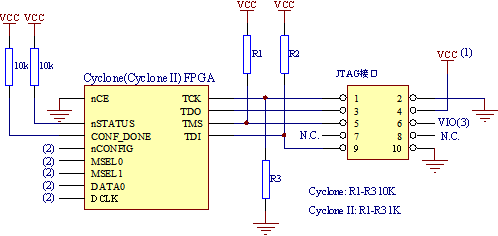

JTAG配置

通過JTAG接口,利用Quartus II軟件可以直接對FPGA進行單獨的硬件重新配置。Quartus II軟件在編譯時會自動生成用于JTAG配置的。sof文件。

如果同時使用AS方式和JTAG方式來配置FPGA,JTAG配置方式擁有最高的優(yōu)先級,此時AS方式將停止,而執(zhí)行JTAG方式配置。

利用Quartus II軟件和USB Blaster等下載電纜可下載配置數(shù)據(jù)到FPGA。Quartus II軟件可以驗證JTAG配置是否成功。JTAG配置通過下載電纜使用SOF、Jam或者JBC文件直接對FPGA進行配置,這種配置方式只能用于調(diào)試階段,因為,掉電后FPGA中的配置數(shù)據(jù)將丟失。

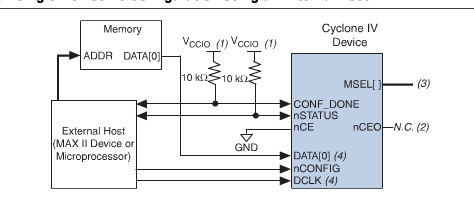

被動串行配置

被動串行PS配置方式是Altera Cyclone IV系列FPGA配置方式中比較常用的方式。但是,在工程應(yīng)用中若采用這種配置方式,F(xiàn)PGA需要連接一個智能主機(比如復(fù)雜可編程邏輯器件CPLD/微控制單元MCU等)以給其提供配置時鐘和配置數(shù)據(jù)。

在該配置方式下,智能主機在保證與存儲配置數(shù)據(jù)的閃存通信無誤的情況下,只需向FPGA提供一個DCLK信號和一個DATA0信號即可實現(xiàn)對FPGA的配置。另外,該DCLK信號還可以實現(xiàn)多種頻率以滿足用戶對配置時間的需求,這是該配置方式的一大亮點。

本文介紹了以Altera型的FPGA芯片為例介紹了FPGA的上電過程,并描述了三種常見的配置模式,用戶可以根據(jù)不同的需求來采用對應(yīng)的配置模式,每種配置模式下對應(yīng)的配置數(shù)據(jù)類型也是不相同的。

更多信息可以來這里獲取==>>電子技術(shù)應(yīng)用-AET<<