一、背景介紹

基于二值圖像的濾波算法即形態(tài)學(xué)濾波,在圖像目標(biāo)采集的預(yù)處理中經(jīng)常被使用到,針對(duì)不同的使用場(chǎng)景涉及到腐蝕、膨脹、開閉運(yùn)算等處理。實(shí)際使用中對(duì)于不同的分辨率大小以及模板窗口大小,都要進(jìn)行代碼的修改去適應(yīng)不同的場(chǎng)景,特別是模板窗口比較大時(shí),代碼改寫工作量就很大。因此,為了減少開發(fā)時(shí)間,本文實(shí)現(xiàn)了一個(gè)通用的算法IP,只需要修改模板窗口大小和工作模式(腐蝕or膨脹)參數(shù)即可,達(dá)到“自適應(yīng)”目的,避免重復(fù)低效的工作。

二、形態(tài)學(xué)濾波原理

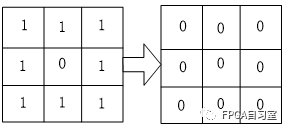

形態(tài)學(xué)濾波由腐蝕和膨脹兩種操作組成。首先,腐蝕(Erosion)的核心思想是圖像像素之間進(jìn)行邏輯與運(yùn)算,簡(jiǎn)單來(lái)說(shuō),當(dāng)一個(gè)包含當(dāng)前像素的結(jié)構(gòu)單元的像素值都為“1”時(shí)輸出待處理的的目標(biāo)像素。

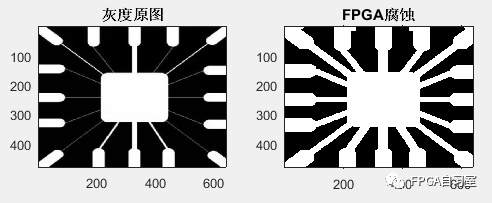

若采用窗口實(shí)現(xiàn)腐蝕操作,如圖2.1所示:

圖2.1腐蝕效果示意圖

腐蝕的作用:在形態(tài)學(xué)中的腐蝕可以去除圖像中的物體邊界點(diǎn),清除圖像中比結(jié)構(gòu)元素小的毛刺或者小突起,此外,結(jié)構(gòu)元素越大,腐蝕的面積就越大。所以,可以使用腐蝕運(yùn)算操作小區(qū)域的非目標(biāo)區(qū)域區(qū)分。

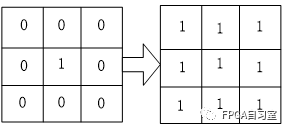

膨脹的核心思想是像素之間進(jìn)行邏輯或運(yùn)算,也就是說(shuō)每個(gè)輸入像素在輸出圖像中被替換成結(jié)構(gòu)單元的形狀。當(dāng)結(jié)構(gòu)單元中任何一個(gè)像素的灰度值為“1”時(shí),那么輸出窗口內(nèi)的像素都為“1”,此時(shí)輸出待處理的目標(biāo)像素。公式可以表示為:

若采用窗口實(shí)現(xiàn)膨脹操作,如圖2.2所示:

圖2.2 膨脹效果示意圖

膨脹的作用:膨脹運(yùn)算可以填充圖像中小于結(jié)構(gòu)元素的孔洞以及圖像邊緣部分的一些小凹陷。對(duì)于目標(biāo)區(qū)域腐蝕后再膨脹操作就是所謂的開運(yùn)算。對(duì)所選定的目標(biāo)區(qū)域先進(jìn)行膨脹操作然后再進(jìn)行腐蝕操作就是所謂的閉運(yùn)算。

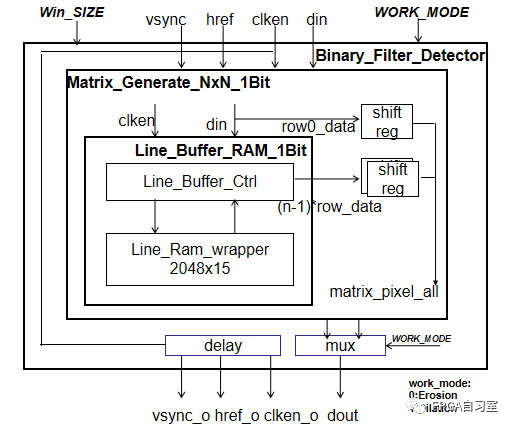

三、FPGA硬件實(shí)現(xiàn)

形態(tài)學(xué)濾波算法的FPGA硬件實(shí)現(xiàn)原理圖,如下圖所示。算法的輸入輸出接口信號(hào)采用標(biāo)準(zhǔn)的 VGA時(shí)序接口,即行場(chǎng)信號(hào)、數(shù)據(jù)和數(shù)據(jù)使能信號(hào)。算法模板輸入?yún)?shù)主要有兩個(gè),Win_SIZE 表示窗口大小,WORK_MODE 表示工作在腐蝕還是膨脹模式,根據(jù)需要配置自己想要的模板大小和工作模式。

由于行緩存是基于RAM的實(shí)現(xiàn)的,本文設(shè)計(jì)的ram的規(guī)格大小是為2048x15,

深度2048 表示支持的最大分辨率,數(shù)據(jù)位寬為15bit表示支持的最大的模板窗口大小為15x15,也可以根據(jù)需要修改ram規(guī)格,其他邏輯不需要改動(dòng)。

最后,需要開運(yùn)算或者閉運(yùn)算時(shí),只需要把兩個(gè)算法IP串聯(lián)起來(lái),配置不同的參數(shù)即可。

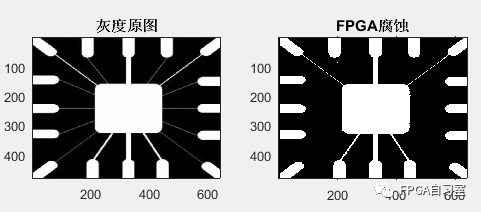

四、仿真驗(yàn)證

本節(jié)主要搭建一個(gè)視頻流Modelsim仿真平臺(tái),在基于FPGA視頻圖像算法開發(fā)過(guò)程中,有必要模擬一個(gè)視頻時(shí)序,用來(lái)驗(yàn)證算法,并有效的利用Matlab工具把靜態(tài)圖片“打散”保存到txt文本里,供Modesim讀取,然后通過(guò)Matalb“復(fù)現(xiàn)”處理后的文本。

3x3腐蝕仿真結(jié)果:

9x9腐蝕仿真結(jié)果:

5x5膨脹仿真結(jié)果:

15x15膨脹仿真結(jié)果:

更多信息可以來(lái)這里獲取==>>電子技術(shù)應(yīng)用-AET<<