FPGA教學(xué)——FPGA中的競(jìng)爭(zhēng)冒險(xiǎn)消除

2022-08-24

作者:旅FPGA之旅

來(lái)源:電子技術(shù)應(yīng)用專欄作家 FPGA之旅

競(jìng)爭(zhēng)冒險(xiǎn)消除

在FPGA的設(shè)計(jì)中,毛刺現(xiàn)象是長(zhǎng)期困擾電子設(shè)計(jì)工程師的設(shè)計(jì)問(wèn)題之,是影響工程師設(shè)計(jì)效率和數(shù)字系統(tǒng)設(shè)計(jì)有效性和可靠性的主要因素。由于信號(hào)在FPGA的內(nèi)部走線和通過(guò)邏輯單元時(shí)造成的延遲,在多路信號(hào)變化的瞬間,組合邏輯的輸出常常產(chǎn)生一些小的尖峰,即毛刺信號(hào),也容易引起競(jìng)爭(zhēng)冒險(xiǎn)現(xiàn)象,從而使電路工作的穩(wěn)定性大受影響。

1、競(jìng)爭(zhēng)與冒險(xiǎn)

1.1 競(jìng)爭(zhēng)

說(shuō)法1:門電路中有兩個(gè)輸入信號(hào)同時(shí)向相反的電平跳變的現(xiàn)象叫做競(jìng)爭(zhēng)。

說(shuō)法2:在組合電路中,某個(gè)變量(或信號(hào))經(jīng)過(guò)兩條以上的路徑到達(dá)輸出端時(shí),由于不同路徑上的延遲時(shí)間不一樣,達(dá)到輸出端的時(shí)間就會(huì)有先有后,這一現(xiàn)象稱作競(jìng)爭(zhēng)。

如圖所示電路及波形:對(duì)于與門,若穩(wěn)態(tài)時(shí),A=1,B=0或A=0,B=1時(shí),輸出皆為Y=0。但在信號(hào)的傳輸過(guò)程中,由于門的傳輸時(shí)間不同,造成在時(shí)間△t內(nèi),出現(xiàn)A和B同時(shí)高VIL(max),這樣在輸出端產(chǎn)生了很窄的脈沖,即Y=1,稱為電壓尖峰或電壓毛刺。

1.2 冒險(xiǎn)

在具有競(jìng)爭(zhēng)可能的組合電路中,由于輸入端的競(jìng)爭(zhēng)而導(dǎo)致的輸出端出現(xiàn)不該有的干擾脈沖(即所謂毛刺),就稱為冒險(xiǎn)。表現(xiàn)為輸出端出現(xiàn)了原設(shè)計(jì)中沒(méi)有的窄脈沖,常稱其為毛刺。

冒險(xiǎn)分類:

1)靜態(tài)冒險(xiǎn)與動(dòng)態(tài)冒險(xiǎn)

冒險(xiǎn)按照其產(chǎn)生形式可以分為靜態(tài)冒險(xiǎn)與動(dòng)態(tài)冒險(xiǎn)。

靜態(tài)冒險(xiǎn)是指輸入產(chǎn)生變化時(shí)輸出產(chǎn)生單個(gè)窄脈沖的現(xiàn)象。靜態(tài)冒險(xiǎn)按其穩(wěn)態(tài)與尖峰的不同可以分為靜態(tài)0型冒險(xiǎn)與靜態(tài)1型冒險(xiǎn)。靜態(tài)1型冒險(xiǎn)是指電路穩(wěn)態(tài)輸出均為1,在輸入信號(hào)變化時(shí)產(chǎn)生短暫的0脈沖的現(xiàn)象。靜態(tài)0型冒險(xiǎn)正好相反。

動(dòng)態(tài)冒險(xiǎn)是指由于輸入變化而導(dǎo)致的輸出產(chǎn)生變化的現(xiàn)象,換言之,就是由于發(fā)生了多次靜態(tài)冒險(xiǎn)導(dǎo)致輸出多個(gè)窄脈沖的現(xiàn)象。靜態(tài)冒險(xiǎn)是由于信號(hào)變化存在快慢而導(dǎo)致,而動(dòng)態(tài)冒險(xiǎn)是由于靜態(tài)冒險(xiǎn)而導(dǎo)致的,當(dāng)電路中存在快、慢與更慢的電路時(shí),就會(huì)產(chǎn)生動(dòng)態(tài)冒險(xiǎn),因?yàn)楫?dāng)不同速度的信號(hào)變化組合時(shí),就會(huì)產(chǎn)生多個(gè)窄脈沖。

2)邏輯冒險(xiǎn)和功能冒險(xiǎn)

冒險(xiǎn)按照其產(chǎn)生條件,可以分為邏輯冒險(xiǎn)和功能冒險(xiǎn)兩大類。

邏輯冒險(xiǎn)是指電路中只有一個(gè)信號(hào)發(fā)生變化卻導(dǎo)致了輸出產(chǎn)生冒險(xiǎn)的現(xiàn)象。顧名思義,這是由于電路的邏輯設(shè)計(jì)的不合理導(dǎo)致,因此應(yīng)該避免此現(xiàn)象,也就是避免下面所說(shuō)的代數(shù)法中的問(wèn)題。

功能冒險(xiǎn)是指由于電路中兩個(gè)或者以上的信號(hào)發(fā)生變化時(shí),由于電路和器件本身的特性導(dǎo)致的到達(dá)時(shí)間差而產(chǎn)生的冒險(xiǎn)。功能冒險(xiǎn)較之于邏輯冒險(xiǎn)更難處理。

1.3 競(jìng)爭(zhēng)與冒險(xiǎn)的關(guān)系

有競(jìng)爭(zhēng)不一定會(huì)有冒險(xiǎn),但有冒險(xiǎn)就一定有競(jìng)爭(zhēng)。

1.4 檢查競(jìng)爭(zhēng)冒險(xiǎn)的方法

1)邏輯表達(dá)式化簡(jiǎn)法

如果輸出端門電路的兩個(gè)輸入信號(hào)A和A’是輸入變量A經(jīng)過(guò)兩個(gè)不同的傳輸途徑而來(lái),則當(dāng)輸入變量發(fā)生變化時(shí),輸出端就可能產(chǎn)生尖峰脈沖。

故對(duì)于輸出端的邏輯函數(shù)在一定條件下能化簡(jiǎn)成:

Y=A+A’ , 存在 “0” 型競(jìng)爭(zhēng);

Y=A*A’ , 存在 “1” 型競(jìng)爭(zhēng);

的情況下,則判定一定有競(jìng)爭(zhēng)冒險(xiǎn)現(xiàn)象。

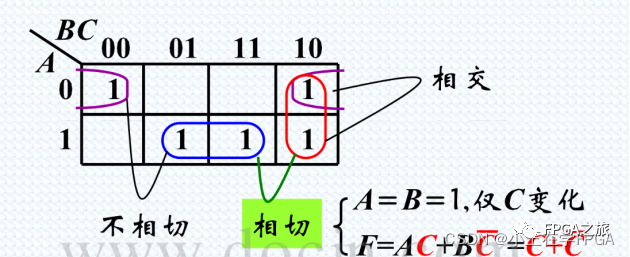

2)卡洛圖法

即如果一個(gè)邏輯函數(shù)的表達(dá)式的卡洛圖中所畫(huà)圈沒(méi)有重疊并且相切,則判定有競(jìng)爭(zhēng)冒險(xiǎn)。(本質(zhì)上還是利用上面的方法,只是比較直觀形象的判斷)

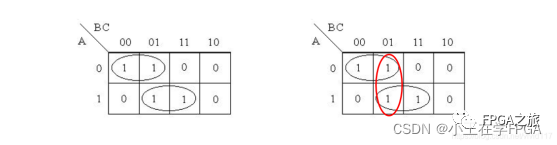

對(duì)于以下卡洛圖,左圖存在競(jìng)爭(zhēng)冒險(xiǎn),而由圖不存在競(jìng)爭(zhēng)冒險(xiǎn)。

具體方法:

通過(guò)邏輯表達(dá)式畫(huà)出卡諾圖來(lái)判斷是否會(huì)出現(xiàn)冒險(xiǎn)現(xiàn)象,當(dāng)卡諾圖中的卡諾圈相切,則有競(jìng)爭(zhēng)冒險(xiǎn)。

由上圖,圖中的圈稱為卡諾圈,卡諾圈中只能包含1,2,4,8....2^n(n為非負(fù)整數(shù))個(gè)元素,當(dāng)該函數(shù)在A=B=1時(shí),存在0型邏輯冒險(xiǎn)。

圖中紅圈與藍(lán)圈有相切的地方,被稱為卡諾圈相切。

1、變量取值在卡諾圈內(nèi)變化,不存在邏輯冒險(xiǎn);

2、變量取值在相切的卡諾圈跳變時(shí),而這個(gè)相切部分又沒(méi)有被另外的卡諾圈包圍,則可能存在邏輯冒險(xiǎn)。

1.5 消除競(jìng)爭(zhēng)冒險(xiǎn)的措施

FPGA設(shè)計(jì)中最簡(jiǎn)單的避免方法是盡量使用時(shí)序同步邏輯同步輸入輸出。

(a) 修改邏輯設(shè)計(jì),增加冗余項(xiàng),消除邏輯冒險(xiǎn);

1)存在競(jìng)爭(zhēng)的情況下,增加冗余項(xiàng),實(shí)現(xiàn)輸出消除毛刺。

例:邏輯表達(dá)式如下:Y = A’BC + AB

當(dāng)B = C = 1時(shí), 電路存在“0”型競(jìng)爭(zhēng)。增加項(xiàng):冗余項(xiàng) B&C

更變后:Y = A’BC + AB + B C (利用消去冗余項(xiàng)公式)

2)還有卡諾圖法,在兩個(gè)相切的圓之間,相切接觸的地方增加一個(gè)連接圓。

對(duì)于上面的卡洛圖,在相切的位置增加 冗余項(xiàng) B’C,故函數(shù)表達(dá)式Y(jié)=A’B’+AC+B’C

(b)采用可靠性編碼,如格雷碼;

(c)引入旁路濾波電容,輸出并聯(lián)濾波電容消除毛刺;

在輸出端并聯(lián)接一個(gè)很小的濾波電容,削弱尖峰脈沖的幅度至門電路的閾值以下。簡(jiǎn)單易行,但是會(huì)增加輸出電壓波形上升時(shí)間和下降時(shí)間,使波形變壞。

(d)加封鎖脈沖;

即在輸入信號(hào)產(chǎn)生競(jìng)爭(zhēng)冒險(xiǎn)的時(shí)間內(nèi),引入一個(gè)脈沖將可能產(chǎn)生尖峰干擾脈沖的門封鎖住,封鎖脈沖應(yīng)該在輸入信號(hào)轉(zhuǎn)換前到來(lái),轉(zhuǎn)換后消失。

(e)加選通脈沖;

即對(duì)輸出可能產(chǎn)生尖峰脈沖的門電路增加一個(gè)接選通信號(hào)的輸入端,只有在輸入信號(hào)轉(zhuǎn)換完成并穩(wěn)定后,才引入選通脈沖將它打開(kāi),此時(shí)才允許有輸出。

For邏輯冒險(xiǎn):增加冗余項(xiàng)(得到非最簡(jiǎn)邏輯,屬于修改邏輯設(shè)計(jì)的方法);卡諾圖法;增加選通電路;增加輸出濾波電容。由此看出,兩面性來(lái)了:一方面想最簡(jiǎn)化邏輯電路,可是卻有可能出現(xiàn)競(jìng)爭(zhēng)冒險(xiǎn),退而求其次,則恰當(dāng)解決問(wèn)題。

For功能冒險(xiǎn):功能冒險(xiǎn)是由于在輸入n個(gè)變量同時(shí)變化時(shí),它們的實(shí)際變化在時(shí)間上有先有后引起的,因此改變電路的邏輯設(shè)計(jì)并不能消除功能冒險(xiǎn)。對(duì)待功能冒險(xiǎn)常用的方法是增加選通信號(hào)或者增加輸出濾波電容方法。

2、毛刺

2.1 毛刺產(chǎn)生的原因

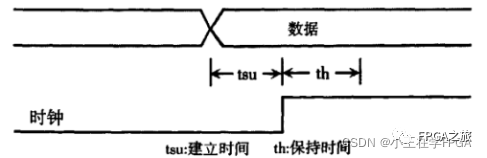

①建立時(shí)間和保持時(shí)間

建立時(shí)間(setup time)是指在觸發(fā)器的時(shí)鐘信號(hào)上升沿到來(lái)以前,數(shù)據(jù)穩(wěn)定不變的時(shí)間,如果建立時(shí)間不夠,數(shù)據(jù)將不能在這個(gè)時(shí)鐘上升沿被打入觸發(fā)器;保持時(shí)間(hold time)是指在觸發(fā)器的時(shí)鐘信號(hào)上升沿到來(lái)以后,數(shù)據(jù)穩(wěn)定不變的時(shí)間,如果保持時(shí)間不夠,數(shù)據(jù)同樣不能被打入觸發(fā)器,如圖所示,數(shù)據(jù)穩(wěn)定傳輸必須滿足建立和保持時(shí)間的要求,當(dāng)然在一些情況下,建立時(shí)間和保持時(shí)間的值可以為零。

②競(jìng)爭(zhēng)和冒險(xiǎn)

FPGA芯片是由可構(gòu)造的輸入輸出塊(Input/Output Block,IOB)、可構(gòu)造邏輯塊(Cinfigurable Logic Block,CLB)和可編程連線資源(Programmable Interconnect Array,PIA)3種可構(gòu)造單元構(gòu)成的。IOB位于芯片內(nèi)部四周,在內(nèi)部邏輯陣列與外部芯片封裝引腳之間提供一個(gè)可編程接口,他主要由邏輯門、觸發(fā)器和控制元組成。CLB組成了FPGA的核心陣列,能完成用戶指定的邏輯功能;每個(gè)CLB主要有一個(gè)組合邏輯、幾個(gè)觸發(fā)器、若干個(gè)多選一電路和控制單元組成;PIA位于芯片內(nèi)部的邏輯塊之間,經(jīng)編程后形成連線網(wǎng)絡(luò),用于芯片內(nèi)部邏輯間的相互連接,并在他們之間傳遞信息。信號(hào)在FPGA器件內(nèi)部通過(guò)連線和邏輯單元時(shí),都有一定的延時(shí)。延時(shí)的大小與連線的長(zhǎng)短和邏輯單元的數(shù)目有關(guān),同時(shí)還受器件的制造工藝、 工作電壓、溫度等條件的影響。信號(hào)的高低電平轉(zhuǎn)換也需要一定的過(guò)渡時(shí)間。由于存在這兩方面因素,多路信號(hào)的電平值發(fā)生變化時(shí),在信號(hào)變化的瞬間,組合邏輯 的輸出有先后順序,并不是同時(shí)變化(及競(jìng)爭(zhēng)現(xiàn)象),往往會(huì)出現(xiàn)一些不正確的尖峰信號(hào),這些尖峰信號(hào)稱為"毛刺"。如果一個(gè)組合邏輯電路中有"毛刺"出現(xiàn),就說(shuō)明該電路存在"冒險(xiǎn)"。(與分立元件不同,由于PLD內(nèi)部不存在寄生電容電感,這些毛刺將被完整的保留并向下一級(jí)傳遞,因此毛刺現(xiàn)象在PLD、FPGA設(shè)計(jì)中尤為突出)也就是說(shuō),在FPGA設(shè)計(jì)中,毛刺產(chǎn)生的根本原因是信號(hào)在芯片內(nèi)部走線時(shí)產(chǎn)生的延遲。

2.2 毛刺產(chǎn)生的條件

由于延遲的作用,多個(gè)信號(hào)到達(dá)終點(diǎn)的時(shí)間有先有后,形成了競(jìng)爭(zhēng),由競(jìng)爭(zhēng)產(chǎn)生的錯(cuò)誤輸出就是毛刺。所以,毛刺發(fā)生的條件就是在同一時(shí)刻有多個(gè)信號(hào)輸入發(fā)生改變。

2.3 毛刺的危害

當(dāng)毛刺信號(hào)成為系統(tǒng)的啟動(dòng)信號(hào),控制信號(hào),握手信號(hào),觸發(fā)器的清零信號(hào),預(yù)置信號(hào),時(shí)鐘信號(hào),或鎖存器的輸入信號(hào)時(shí)就會(huì)產(chǎn)生邏輯錯(cuò)誤。

2.4 消除毛刺的方法

知道了毛刺產(chǎn)生的條件,就可以通過(guò)改變?cè)O(shè)計(jì),破壞其條件來(lái)減少毛刺的發(fā)生。例如,利用格雷碼計(jì)數(shù)器每次輸出只有一位跳變的特性,代替普通的二進(jìn)制計(jì)數(shù)器,避免了毛刺的產(chǎn)生。還可以對(duì)電路進(jìn)行改進(jìn),以消除毛刺對(duì)系統(tǒng)的影響。

①利用冗余項(xiàng)法

利用冗余項(xiàng)消除毛刺有2種方法:代數(shù)法和卡諾圖法,兩者都是通過(guò)增加冗余項(xiàng)來(lái)消除險(xiǎn)象,只是前者針對(duì)于函數(shù)表達(dá)式而后者針對(duì)于真值表。以卡諾圖為例,若兩個(gè)卡諾圓相切,其對(duì)應(yīng)的電路就可能產(chǎn)生險(xiǎn)象。因此,修改卡諾圖,在卡諾圖的兩圓相切處增加一個(gè)圓,以增加多余項(xiàng)來(lái)消除邏輯冒險(xiǎn)。但該法對(duì)于計(jì)數(shù)器型產(chǎn)生的毛刺是無(wú)法消除的。

②采樣法

由于冒險(xiǎn)多出現(xiàn)在信號(hào)發(fā)生電平跳變的時(shí)刻,即在輸出信號(hào)的建立時(shí)間內(nèi)會(huì)產(chǎn)生毛刺,而在保持時(shí)間內(nèi)不會(huì)出現(xiàn),因此,在輸出信號(hào)的保持時(shí)間內(nèi)對(duì)其進(jìn)行采樣,就可以消除毛刺信號(hào)的影響,常用的采樣方法有2種:一種使用一定寬度的高電平脈沖與輸出相與,從而避開(kāi)了毛刺信號(hào),取得輸出信號(hào)的電平值。這種方法必須保證采樣信號(hào)在合適的時(shí)間產(chǎn)生,并且只適用于對(duì)輸出信號(hào)時(shí)序和脈沖寬度要求不嚴(yán)的情況。另一種更常見(jiàn)的方法叫鎖存法,是利用D觸發(fā)器的輸入端D對(duì)毛刺信號(hào)不敏感的特點(diǎn),在輸出信號(hào)的保持時(shí)間內(nèi),用觸發(fā)器讀取組合邏輯的輸出信號(hào)。由于在時(shí)鐘的上升沿時(shí)刻,輸出端Q=D,當(dāng)輸入的信號(hào)有毛刺時(shí),只要不發(fā)生在時(shí)鐘的上升沿時(shí)刻,輸出就不會(huì)有毛刺。這種方法類似于將異步電路轉(zhuǎn)化為同步電路,實(shí)現(xiàn)簡(jiǎn)單,但同樣會(huì)涉及到時(shí)序問(wèn)題。

③吸收法

由于產(chǎn)生的毛刺實(shí)際上是高頻窄脈沖,故增加輸出濾波,在輸出端接上小電容C就可以濾除毛刺。但輸出波形的前后沿將變壞,在對(duì)波形要求較嚴(yán)格時(shí),應(yīng)再加整形電路,該方法不宜在中間級(jí)使用。

④延遲法

因?yàn)槊套罱K是由于延遲造成的,所以可以找出產(chǎn)生延遲的支路。對(duì)于相對(duì)延遲小的支路,加上毛刺寬度的延遲可以消除毛刺。但有時(shí)隨著負(fù)載增加,毛刺會(huì)繼續(xù)出現(xiàn),而且,當(dāng)溫度變化,所加的電壓變化或要增加邏輯門時(shí),所加的延遲是不同的,必須重新設(shè)計(jì)延遲線,因而這種方法也是有局限性的。而且采用延遲線的方法產(chǎn)生延遲會(huì)由于環(huán)境溫度的變化而使系統(tǒng)可靠性變差。

⑤硬件描述語(yǔ)言法

這種方法是從硬件描述語(yǔ)言入手,找出毛刺產(chǎn)生的根本原因,改變語(yǔ)言設(shè)計(jì),產(chǎn)生滿足要求的功能模塊,來(lái)代替原來(lái)的邏輯功能塊。

在Verilog編程時(shí),需要注意以下幾方面,在絕大多數(shù)情況下可避免綜合后仿真出現(xiàn)冒險(xiǎn)問(wèn)題。

1)時(shí)序電路建模時(shí),用非阻塞賦值。

2)鎖存器電路建模時(shí),用非阻塞賦值。

3)用always和組合邏輯建模時(shí),用阻塞賦值。

4)在同一個(gè)always塊中建立時(shí)序和組合邏輯模型時(shí),用非阻塞賦值。

5)在同一個(gè)always塊中不要既使用阻塞賦值又使用非阻塞賦值。

6)不要在多個(gè)always塊中為同一個(gè)變量賦值。

避免在綜合時(shí)引入鎖存器的注意點(diǎn)包括:

1)組合電路的每一個(gè)if-else語(yǔ)句要完整,即每一個(gè)if要對(duì)應(yīng)一個(gè)else,時(shí)序電路if語(yǔ)句不完整不會(huì)出現(xiàn)鎖存器問(wèn)題。

2)case語(yǔ)句要完整,即每一個(gè)case語(yǔ)句對(duì)應(yīng)一個(gè)default。

更多信息可以來(lái)這里獲取==>>電子技術(shù)應(yīng)用-AET<<