自從商業(yè)上可行的 FPGA 出現(xiàn)以來,嵌入式設(shè)計(jì)人員就已經(jīng)實(shí)現(xiàn)了異構(gòu)架構(gòu)。最初,F(xiàn)PGA 主要用作處理系統(tǒng)、外設(shè)和 I/O 之間接口的粘合邏輯。但隨著 FPGA 技術(shù)的改進(jìn),市場擴(kuò)大到在嵌入式系統(tǒng)中發(fā)揮更大和更核心的作用。異構(gòu)計(jì)算的最新趨勢是將處理器和 FPGA 子系統(tǒng)集成到單個(gè) SoC 中。以處理器和軟件為中心的設(shè)計(jì)團(tuán)隊(duì)現(xiàn)在可以在這些復(fù)雜的 SoC 上利用這兩個(gè)系統(tǒng)。

異構(gòu)計(jì)算架構(gòu)

系統(tǒng)設(shè)計(jì)人員被嵌入式系統(tǒng)的處理器和 FPGA 組合所吸引,因?yàn)樗鼈冊跇?biāo)準(zhǔn)設(shè)計(jì)模板中提供了靈活性和性能。系統(tǒng)中的處理器提供了廣泛的標(biāo)準(zhǔn)外設(shè)接口,如以太網(wǎng)、串口、USB、CAN、SPI和內(nèi)存。在僅處理器方法中,應(yīng)用程序 I/O 通常通過 SPI 或 USB 連接。為處理器開發(fā)軟件已廣為人知且易于管理。

在處理器和專用 I/O 之間放置 FPGA 可提高系統(tǒng)的靈活性和處理能力,并增加硬件驅(qū)動(dòng)操作的可靠性和確定性。FPGA 不受操作系統(tǒng)或其他軟件開銷的影響,這會(huì)降低性能并降低可靠性。由于 FPGA 是可重新配置的門陣列邏輯電路矩陣,其硬件可以重新編程以執(zhí)行無數(shù)功能,包括信號(hào)處理、自定義定時(shí)和觸發(fā),以及極其先進(jìn)的確定性控制。可重新編程有助于硬件升級(jí)和產(chǎn)品差異化,從而在不斷發(fā)展的接口和標(biāo)準(zhǔn)中延長產(chǎn)品壽命。

除了這些優(yōu)勢之外,處理器加 FPGA 的組合還帶來了一些挑戰(zhàn):

FPGA 的功耗

將單獨(dú)的 FPGA 集成到 PCB 設(shè)計(jì)中的尺寸、成本和復(fù)雜性

與處理器上的軟件開發(fā)相比,與 FPGA 硬件設(shè)計(jì)相關(guān)的編程。

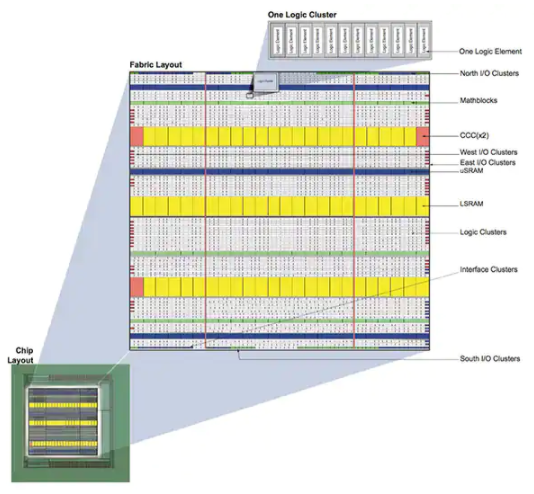

FPGA 供應(yīng)商正在通過 SoC 解決其中的許多挑戰(zhàn),SoC 集成了處理器和 FPGA,并確保兩者之間的連接。Xilinx Zynq All Programmable SoC 是一個(gè)將 ARM Cortex-A9 CPU 與 FPGA 邏輯集成的示例。Cypress Semiconductor PSoC(可編程 SoC)和 Microsemi SmartFusion cSoC(可定制 SoC)將 ARM Cortex-M3 CPU 與可編程邏輯和可編程模擬接口集成在一起。這些產(chǎn)品降低了集成 FPGA 的尺寸、成本和功耗。

圖 1:SoC 相對于 DSP 或 ASIC 的優(yōu)勢——基于每芯片的 MAC、每 W 的 MAC 和每美元的 MAC。

軟件編程和硬件描述語言

將 FPGA 子系統(tǒng)集成到處理器 SoC 通常會(huì)使 PCB 設(shè)計(jì)更加容易。然而,對這兩個(gè)系統(tǒng)進(jìn)行編程仍然很困難。通常,硬件描述語言 (HDL),如 VHDL 或 Verilog,是利用 FPGA 所必需的。精通 C/C++ 等語言的系統(tǒng)設(shè)計(jì)人員庫非常豐富,而 HDL 專家只占嵌入式系統(tǒng)工程師勞動(dòng)力的一小部分。

可編程邏輯工具已經(jīng)發(fā)展到更好地適應(yīng)嵌入式軟件工程師的技能。具有 FPGA 架構(gòu)的 FPGA 和 SoC 可供領(lǐng)域和 VHDL 專家在工業(yè)應(yīng)用中使用。FPGA 供應(yīng)商正在大力投資工具和合作伙伴,以更好地協(xié)調(diào)處理器和 FPGA 架構(gòu)之間的開發(fā)實(shí)踐。高級(jí)綜合 (HLS) 工具,例如 LabVIEW FPGA 模塊、Vivado HLS 或 SystemC,可縮小軟件和數(shù)字域之間的代碼開發(fā)差距。

一個(gè)示例工具是 LabVIEW,它自 2003 年以來就具有一個(gè)插件模塊,該模塊針對用于 NaTIonal Instruments 基于 FPGA 的硬件中的 Xilinx FPGA。該工具將處理器和 FPGA 邏輯的開發(fā)抽象為相同的語言和控制循環(huán),這可以比以前使用基于處理器的系統(tǒng)更快地創(chuàng)建。單個(gè)系統(tǒng)設(shè)計(jì)人員可以掌握軟件和 FPGA 開發(fā)領(lǐng)域,這通常需要兩名或多名具有獨(dú)特技能的工程師。他們可以利用內(nèi)置語言結(jié)構(gòu)來管理時(shí)鐘/時(shí)序、內(nèi)存 I/O 和數(shù)據(jù)傳輸(例如,直接內(nèi)存訪問),以及周期精確的仿真和調(diào)試功能、云編譯支持以提高生產(chǎn)力,以及支持 HDL 集成。一個(gè)算法,寫一次,

通過提高集成度來縮短上市時(shí)間

使用傳統(tǒng)方法,將 I/O 集成到 FPGA 中通常很耗時(shí)。許多高級(jí)綜合工具無法替代整個(gè) HDL 工具鏈,因?yàn)閺?FPGA 架構(gòu)到現(xiàn)實(shí)世界的 I/O 接口仍然必須使用 HDL 實(shí)現(xiàn)。來自 HDL 設(shè)計(jì)團(tuán)隊(duì)的軼事表明,I/O 集成通常需要 70% 以上的時(shí)間專門用于設(shè)計(jì),而只有 30% 或更少的時(shí)間用于通過控制算法或信號(hào)處理來增加差異化價(jià)值。

LabVIEW 軟件和基于 FPGA 的硬件的緊密集成帶來了解放——團(tuán)隊(duì)可以提升集成水平,不再為完全定制設(shè)計(jì)的細(xì)節(jié)所累。他們可以花更多的時(shí)間專注于增加自己的價(jià)值和差異化,而不是花在構(gòu)建操作系統(tǒng)、開發(fā)中間件驅(qū)動(dòng)程序或調(diào)試 PCB 設(shè)計(jì)信號(hào)完整性問題上。

更多信息可以來這里獲取==>>電子技術(shù)應(yīng)用-AET<<