和所有的數(shù)字電路一樣,毛刺也是FPGA電路中的棘手問(wèn)題,它的出現(xiàn)會(huì)影響電路工作的穩(wěn)定性,可靠性,嚴(yán)重時(shí)會(huì)導(dǎo)致整個(gè)數(shù)字系統(tǒng)的誤動(dòng)作和邏輯紊亂。

信號(hào)在FPGA器件中通過(guò)邏輯單元連線時(shí),一定存在延時(shí)。延時(shí)的大小不僅和連線的長(zhǎng)短和邏輯單元的數(shù)目有關(guān),而且也和器件的制造工藝、工作電壓、溫度等有關(guān)。

另外,信號(hào)的高低電平轉(zhuǎn)換也需要一定的過(guò)渡時(shí)間,由于存在這兩方面的因素,多路信號(hào)的電平值發(fā)生變化時(shí),在信號(hào)變化的瞬間,組合邏輯的輸出有先后順序,并不是同時(shí)變化,往往會(huì)出現(xiàn)一些不正確的尖峰信號(hào),這些尖峰信號(hào)就是“毛刺”。任何組合電路,反饋電路和計(jì)數(shù)器都可能。

潛在的毛刺信號(hào)發(fā)生器。

電路布線長(zhǎng)短不同造成各端口輸入信號(hào)延時(shí)不一致,有競(jìng)爭(zhēng)冒險(xiǎn),會(huì)產(chǎn)生毛刺。分立元件之間存在分布電容和電感可以濾掉這些毛刺,所以用分立元件設(shè)計(jì)電路時(shí),很少考慮競(jìng)爭(zhēng)冒險(xiǎn)和毛刺問(wèn)題,但PLD/FPGA內(nèi)部沒(méi)有分布電容和電感,不能濾掉任何毛刺(哪怕不到1ns)。

舉個(gè)簡(jiǎn)單的例子:

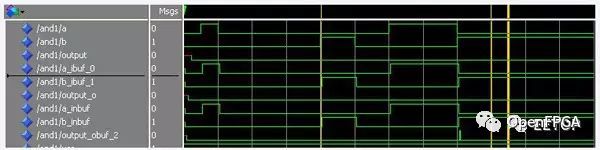

設(shè)計(jì)的一個(gè)二輸入與門,output<=A & B;進(jìn)行布局布線后仿真(此時(shí)沒(méi)有加管腳約束文件)可看到:

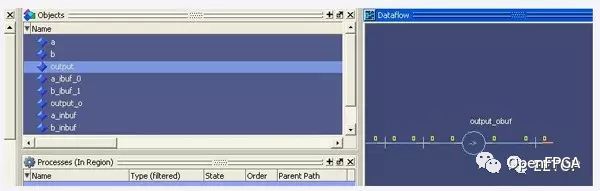

output_obuf_2處有一毛刺出現(xiàn)。毛刺高電平時(shí)間維持141ps。

從output_obuf到output輸出處,雖消除了毛刺,但不能保證其它情況下都會(huì)消除,我想有可能是此處毛刺時(shí)間比較小的原因,所以才有output處輸出是正常的。

首先毛刺的出現(xiàn)是由于輸入端A由1到0和B由0到1的變化引起的。

從靜態(tài)時(shí)序文件中可以看到:A,B到達(dá)與門的時(shí)間相差141ps,這也正是上述中出現(xiàn)毛刺的原因。

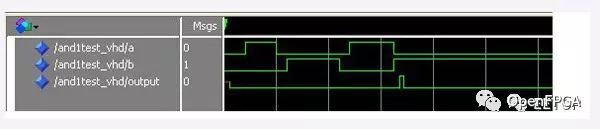

下面將管腳約束文件加進(jìn)去再進(jìn)行后仿真:

可看出此時(shí)output輸出有明顯的毛刺出現(xiàn)。

時(shí)序分析報(bào)告:

對(duì)于信號(hào)A:(Trace delay of A)+AND gate internal delay=9.139ns;

對(duì)于信號(hào)B:(Trace delay of B)+AND gate internal delay=5.607ns;

即A和B到達(dá)與門的時(shí)間相差了3.532ns,下圖顯示毛刺的時(shí)間即正好相符。

毛刺并不是對(duì)所有的輸入都有危害,如觸發(fā)器的D輸入端,只要數(shù)據(jù)不出現(xiàn)在時(shí)鐘的上長(zhǎng)升沿,并滿足數(shù)據(jù)的建立保持時(shí)間,就不會(huì)對(duì)系統(tǒng)造成危害,而當(dāng)毛刺信號(hào)成為系統(tǒng)的啟動(dòng)信號(hào),控制信號(hào),握手信號(hào),觸發(fā)器的清零信號(hào),預(yù)置信號(hào),時(shí)鐘信號(hào),或鎖存器的輸入信號(hào)時(shí)就會(huì)產(chǎn)生邏輯錯(cuò)誤。因此,判斷邏輯電路中是否存在冒險(xiǎn)以及如何避免冒險(xiǎn)是設(shè)計(jì)人員必須考慮的問(wèn)題。

更多信息可以來(lái)這里獲取==>>電子技術(shù)應(yīng)用-AET<<