高速數(shù)字接口測(cè)試,讓容限測(cè)試更高效

2023-06-13

作者:Andrea Vinci,Tektronix EMEA 技術(shù)市場(chǎng)經(jīng)理

來(lái)源:泰克科技

數(shù)字電路和接口在越來(lái)越高的時(shí)鐘頻率下的表現(xiàn)非常類(lèi)似于模擬電路。所以,為了確保新設(shè)計(jì)方案和重新設(shè)計(jì)的方案中接口的質(zhì)量,必須引入新的測(cè)量方法和測(cè)量設(shè)備。

當(dāng)今車(chē)輛中的信息娛樂(lè)系統(tǒng)需要的功能,只有借助新型高速顯卡和超快內(nèi)存才能實(shí)現(xiàn)。我們所有的數(shù)字社交互動(dòng)信息都經(jīng)由大型服務(wù)器記錄和處理,它們需要快速地從大功率存儲(chǔ)器中調(diào)取數(shù)據(jù),并傳輸至各下級(jí)系統(tǒng)進(jìn)行處理。

大量的圖像不斷被拍攝,并以高分辨率格式保存,它們?cè)诟鞣N情況下被發(fā)往 AI 服務(wù)器;先進(jìn)的算法可快速地處理數(shù)據(jù),并輸出優(yōu)質(zhì)的結(jié)果。

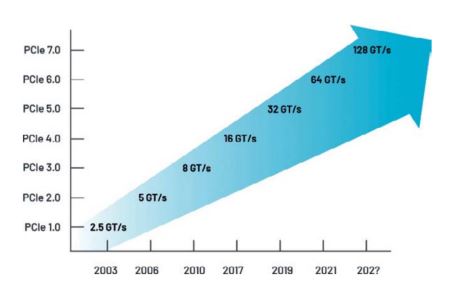

一個(gè)典型的 AI 服務(wù)器與其他先進(jìn)的計(jì)算機(jī)系統(tǒng)一樣:由一個(gè)主板和其他一些先進(jìn)的組件構(gòu)成,如:顯卡、硬盤(pán)和大量相連的交換機(jī)。所有這些設(shè)備的連接標(biāo)準(zhǔn)均基于 PCI Express (PCIe)。其自 2003 年發(fā)布第一代以來(lái),PCI-SIG 標(biāo)準(zhǔn)便一直致力于完成數(shù)據(jù)率隨每一代 PCIe 的更新翻一番的目標(biāo)。

數(shù)據(jù)傳輸速率隨 PCI Express 的代際更新而升高

數(shù)字電路的挑戰(zhàn)

然而,處理更高的數(shù)據(jù)傳輸速率意味著電子系統(tǒng)的開(kāi)發(fā)也需要一步步繼續(xù)發(fā)展,這也需要非常多的技巧和耐心。復(fù)雜且相互關(guān)聯(lián)的主板系統(tǒng)和增插卡需要仔細(xì)拆解為更小的電路,每個(gè)子電路都將作為下一階段的目標(biāo)進(jìn)行改進(jìn),即使整個(gè)電路設(shè)計(jì)已經(jīng)完成。

隨著對(duì)帶寬需求的增加,PCIe Gen4 已經(jīng)在各個(gè)市場(chǎng)中取代了上一代技術(shù)。與此相適應(yīng),開(kāi)發(fā)人員對(duì)現(xiàn)行的電路設(shè)計(jì)進(jìn)行不斷更新,交流有關(guān)走線(xiàn)、布線(xiàn)的建議和準(zhǔn)則,以最大程度地減少串?dāng)_或解決因過(guò)孔位置不當(dāng)導(dǎo)致的 EMI 問(wèn)題。

這些開(kāi)發(fā)人員往往是探路先鋒,他們持續(xù)所面臨的問(wèn)題是確定潛在的信號(hào)衰減可能發(fā)生的位置和原因,以及究竟還存在多大的冗余。簡(jiǎn)單地將一個(gè)插頭換為更實(shí)惠的品類(lèi)、最后關(guān)頭因?yàn)榱W(xué)原因或者供應(yīng)鏈而導(dǎo)致的引線(xiàn)分配的微調(diào)、固件或硬件的升級(jí),又或者是生產(chǎn)工藝的任何變化都可能是可怕的噩夢(mèng),因?yàn)榻鉀Q這些問(wèn)題需要花費(fèi)額外的精力和時(shí)間來(lái)重新對(duì)線(xiàn)路板進(jìn)行設(shè)計(jì)。

TMT4 PCIe性能綜合測(cè)試儀

在主板上應(yīng)用 BIOS 更新可以實(shí)現(xiàn)與 NVMx SSD 硬盤(pán)間的全速通訊,但也可能引起電氣物理層面上的變化。在固件升級(jí)期間,與主板連接且與 CPU 通信的交換機(jī)和計(jì)時(shí)器的配置可能會(huì)發(fā)生變化,在變化之后執(zhí)行“通道容限測(cè)試”可能會(huì)得到不同的測(cè)試結(jié)果。抖動(dòng)限值的改進(jìn)隨時(shí)可能發(fā)生,在綜合模擬工具中進(jìn)行準(zhǔn)確建模是在確定對(duì) PHY 物理層實(shí)際產(chǎn)生影響之前的虛擬驗(yàn)證的關(guān)鍵。然而,模擬并不是總能代表真實(shí)的情況,所以仍然必須執(zhí)行物理層面的測(cè)試。

低功耗的 Gen3 和 Gen4 配置常常被重新設(shè)置,以實(shí)現(xiàn)潛在的節(jié)能配置。即使在對(duì)電源電路進(jìn)行微調(diào)時(shí),也應(yīng)該確保電源重新接通的步驟足夠快,以滿(mǎn)足連接建立時(shí)間的要求,因?yàn)閮H僅是增加幾毫秒便可能導(dǎo)致形成一種需要重新驗(yàn)證的新情況。

然而,在這些場(chǎng)景下,重新對(duì)線(xiàn)路設(shè)計(jì)進(jìn)行驗(yàn)證可能并不經(jīng)濟(jì)高效:事實(shí)上,對(duì)在物聯(lián)網(wǎng)/消費(fèi)者應(yīng)用中銷(xiāo)售且依舊使用 PCIe Gen3 連接的非關(guān)鍵性低成本產(chǎn)品進(jìn)行微小的設(shè)計(jì)變更后重新花費(fèi)時(shí)間進(jìn)行實(shí)驗(yàn)室驗(yàn)證可能并不合理。

半導(dǎo)體企業(yè)需要遵循復(fù)雜的決策路徑,以便針對(duì)某設(shè)計(jì)變更根據(jù)經(jīng)驗(yàn)作出是否進(jìn)行新的驗(yàn)證的判斷。判斷的標(biāo)準(zhǔn)源于風(fēng)險(xiǎn)和成本分析。

在此情況下使用到的測(cè)試儀器通常為誤碼率測(cè)試儀 (BERT) 和示波器。這些儀器也在不斷發(fā)展,以滿(mǎn)足每一代 PCIe 標(biāo)準(zhǔn)的要求,但根據(jù)用戶(hù)的經(jīng)驗(yàn),這些儀器的操作普遍比較有挑戰(zhàn)性。

驗(yàn)證成本不僅僅與硬件的購(gòu)置成本有關(guān),而且與執(zhí)行此工作而配備的專(zhuān)家資源的時(shí)間成本有關(guān)。一名軟件操作助手可以通過(guò)測(cè)試來(lái)保證進(jìn)行每項(xiàng)檢測(cè)時(shí)被測(cè)設(shè)備都進(jìn)行了正確的電氣連接,但是使用 BERT 和帶探頭的示波器的整體過(guò)程還是需要一名專(zhuān)家全程進(jìn)行監(jiān)控。

以鏈路初始化的驗(yàn)證為例

以鏈路初始化為例,它是一個(gè)物理層的控制過(guò)程,其對(duì)于設(shè)備物理層的初始化和將一些設(shè)置應(yīng)用至鏈路是不可或缺的。在正常操作中,這個(gè)過(guò)程是自動(dòng)的,但如果您對(duì)深度的設(shè)計(jì)驗(yàn)證感興趣,則需要對(duì)特定數(shù)據(jù)進(jìn)行編碼的軟件來(lái)允許用戶(hù)診斷和監(jiān)控在狀態(tài)轉(zhuǎn)換期間信號(hào)發(fā)生的潛在問(wèn)題。BERT 通常用于精確控制的鏈路訓(xùn)練和均衡,涵蓋三個(gè)關(guān)鍵測(cè)試領(lǐng)域:合規(guī)性、容限測(cè)試和故障檢測(cè)。此外還需要實(shí)時(shí)示波器,需要高度開(kāi)發(fā)的應(yīng)用軟件在接收端自動(dòng)完成復(fù)雜的測(cè)試過(guò)程,并與 BERT 實(shí)時(shí)通訊,交換配置參數(shù)數(shù)據(jù)。

容限測(cè)試還需要在 PCIe 插槽的每個(gè)通道上依次重復(fù)一系列固定的步驟,包括設(shè)置觸發(fā)電壓時(shí)間。這種涉及多種不同高度開(kāi)發(fā)設(shè)備的冗長(zhǎng)且復(fù)雜的工序可能引入人為失誤,進(jìn)而影響到整個(gè)檢測(cè)程序的效率。

Tektronix 并非尋求 BERT/示波器系統(tǒng)的替代品或是已經(jīng)廣泛使用的 On Chip Lane Margining Tool,而是采取了不同的解決方案。

TMT4 PCIE性能綜合測(cè)試儀實(shí)時(shí)為用戶(hù)顯示眼圖。

TMT4 PCIE性能綜合測(cè)試儀開(kāi)創(chuàng)了業(yè)內(nèi)獨(dú)特的、評(píng)估 PCIe Gen 3 和 PCIe Gen 4 鏈路運(yùn)行狀況的功能。

TMT4 PCIE性能綜合測(cè)試儀可連接至大多數(shù)流行的 PCI 形狀因數(shù),如 CEM、M.2、U.2 和 U.3,能夠與當(dāng)今可用的大多數(shù) PCIe 設(shè)備進(jìn)行連接。該TMT4綜合測(cè)試儀除顯示眼圖外,還提供了其接收端用來(lái)最大化眼圖高度和寬度的補(bǔ)償相關(guān)的信息。

系統(tǒng)對(duì)于發(fā)射器測(cè)試提供了兩個(gè)重要的數(shù)據(jù):可以在容限測(cè)試儀接收器測(cè)量的每個(gè)通道/預(yù)設(shè)組合的眼圖。容限測(cè)試儀的接收器訓(xùn)練值,用于充分張開(kāi)眼圖。

在接收端,可以對(duì)測(cè)試件的接收器路徑進(jìn)行功能評(píng)估。具體來(lái)說(shuō),其旨在確定在預(yù)期的操作范圍內(nèi)從容限測(cè)試儀發(fā)射的信號(hào)在錯(cuò)誤返回之前的衰減程度。

在這樣的使用情境下,新的 TMT4 PCIE性能綜合測(cè)試儀可作為額外的設(shè)備,專(zhuān)注于發(fā)送和接收通道的容限,使用戶(hù)在短短幾分鐘內(nèi)評(píng)估 PCIe Gen 3 和 PCIe Gen 4 設(shè)備的運(yùn)行狀況成為可能。

更多精彩內(nèi)容歡迎點(diǎn)擊==>>電子技術(shù)應(yīng)用-AET<<