一. 簡介

第八例啦,本例將介紹如何通過FPGA采集DS18B20傳感器的溫度值。

二. DS18B20簡介

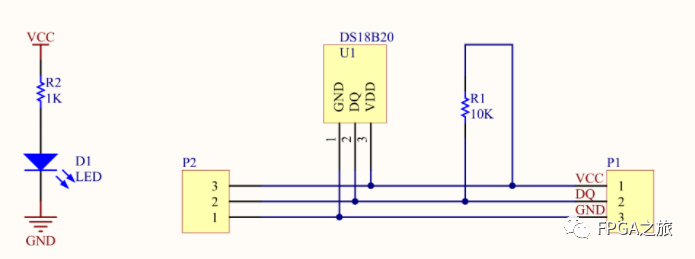

通過原理圖可以看出,DS18B20溫度傳感器只有一條總線,可想而知,其結(jié)構(gòu)的簡單化,導(dǎo)致了其操作的復(fù)雜化。更多關(guān)于該傳感器的一些特性參數(shù),以及性能指標(biāo),可以詳細(xì)閱讀官網(wǎng)提供的數(shù)據(jù)手冊。接下來主要講解怎樣使用它。

三. 初始化

從圖中可以看出,首先得由我們FPGA將總線拉低,時間為480us以上

FPGA釋放總線后,再等待一個15-60us

然后會由DS18B20將總線拉低,時間為60-240us

最后DS18B20也會釋放總線,等待一定時間后(從圖中根據(jù)自己之前的時間可以算出),初始化完成

四. 寫

這里我們只看上面一行圖,前半部分對應(yīng)寫0的操作,后半部分對應(yīng)著寫1的操作.

從圖中可以得出,寫每一位的時鐘周期為60us,然后每一位之間的時間間隔至少為1us

寫的時候,先FPGA拉低總線15us,告知DS18B20要接收數(shù)據(jù)了,然后的45us里面根據(jù)數(shù)據(jù)是0還是1,決定FPGA是將數(shù)據(jù)線拉低還是拉高

完了之后,F(xiàn)PAG釋放總線,完成一位的數(shù)據(jù)寫入

此外每寫入一個字節(jié)后,最好等待50us的時間,再寫下一個字節(jié)

五. 讀

在第三節(jié)的那個圖的第二行中,有完整的讀操作時序可以看到,讀寫的周期數(shù)和每位之間的間隔數(shù)完全相同,只是對應(yīng)的操作稍有變化,但變化不大,先簡要的說明一下

前15us為真正的讀取操作,后面的45us可以不用管,F(xiàn)PGA直接釋放總線

讀取數(shù)據(jù)在前面的15us內(nèi)完成,具體怎樣可以看下面的這張圖

FPGA先將總線拉低一個T_INT時間,可以定為1.5us

然后FPGA釋放總線,等待一個T_RC時間,也可以定為1.5us

最后,在接下來的時間點,進行采樣讀取數(shù)據(jù)

讀取數(shù)據(jù)的操作在此就完成了。

六. 讀出數(shù)據(jù)的格式

最后再對數(shù)據(jù)的格式進行介紹一下

從圖中可以看到,一個溫度數(shù)據(jù)是16位的

在Figure2中可以看到每一位下對應(yīng)著的含義,S表示符號位,1為負(fù)數(shù),0為正數(shù)

在Table1中,可以看到一些溫度值,對應(yīng)著的二進制是怎樣表示的,下面舉例說明一下

+0.5 0000_0000_0000_1000 = 1/2 = 0.5

-0.5 1111_1111_1111_1000 = 0000_0000_0000_0111 + 1

= 0000_0000_0000_1000

= -0.5

負(fù)數(shù)在這里面是存儲的補碼,先要取反,然后加一,最后添負(fù)號

七. 程序

剛開始的時候,可以參考C51編寫的代碼來寫Verilog的代碼,這樣可以很快的知道編寫的流程是怎樣的,以及狀態(tài)機的狀態(tài)有那些和一些注意事項

通過下面的C語言讀取溫度的過程,可以看知道讀取溫度的具體步驟

先啟動溫度轉(zhuǎn)換,由于溫度轉(zhuǎn)換需要一點時間,所以需要一點等待,然后再進行讀溫度寄存器的命令,然后是讀取溫度了,最后通過上面的Figure2圖進行裝換。

Verilog程序的狀態(tài)機如下圖,可以與上面的C程序很好的對應(yīng)起來

給出Signal Top抓取的信號圖

最后在開發(fā)板上的效果如下圖

就不進行仿真了啦!

需要完整代碼的可以在公眾號FPGA之旅中回復(fù) :FPGA之旅設(shè)計99例之第八例

更多信息可以來這里獲取==>>電子技術(shù)應(yīng)用-AET<<

電子技術(shù)應(yīng)用專欄作家 FPGA之旅

原文鏈接:https://mp.weixin.qq.com/s/medhKIQCo-KB904mXzwmpw