近日,一則美國(guó)制造出了0.7納米芯片的芯片在筆者的朋友圈傳播。與此同時(shí)傳播的新還有類似繞開(kāi)EUV光刻機(jī)、美國(guó)打造全球分辨率最高光刻系統(tǒng)。這究竟是個(gè)什么新聞?從現(xiàn)階段看EUV光刻機(jī)會(huì)是怎樣的一個(gè)未來(lái)?

讓我們來(lái)還原以下這個(gè)新聞本身。

美國(guó)企業(yè)推出了0.7nm芯片?

這其實(shí)是來(lái)自美國(guó)Zyvex Labs的一個(gè)報(bào)道。

在9月21日, Zyvex Labs宣布,推出世界上最高分辨率的光刻系統(tǒng) — ZyvexLitho1。該工具使用量子物理技術(shù)來(lái)實(shí)現(xiàn)原子精度圖案化和亞納米(768 皮米——Si (100) 2×1 二聚體行的寬度)分辨率。這一進(jìn)步使量子計(jì)算機(jī)能夠?yàn)檎嬲踩耐ㄐ盘峁├尾豢善频募用埽贿€更快的藥物發(fā)現(xiàn)和更準(zhǔn)確的天氣預(yù)報(bào)。

報(bào)道進(jìn)一步指出,ZyvexLitho1 是一款基于掃描隧道顯微鏡 (STM:Scanning Tunneling Microscopy) 儀器,Zyvex Labs 自 2007 年以來(lái)一直在改進(jìn)該儀器。ZyvexLitho1 包含許多商業(yè)掃描隧道顯微鏡所不具備的自動(dòng)化特性和功能。

“構(gòu)建可擴(kuò)展的量子計(jì)算機(jī)存在許多挑戰(zhàn)。我們堅(jiān)信,要實(shí)現(xiàn)量子計(jì)算的全部潛力,需要高精度制造,”Michelle Simmons 教授說(shuō)。“我們對(duì) ZyvexLitho1 感到興奮,這是第一個(gè)提供原子精度圖案化的商用工具。”

STM 光刻技術(shù)的發(fā)明者 Joe Lyding 教授表示:“迄今為止,Zyvex Labs 技術(shù)是這種原子級(jí)精確光刻技術(shù)的最先進(jìn)和唯一的商業(yè)化實(shí)現(xiàn)。” Lyding 是 2014 年費(fèi)曼獎(jiǎng)獲得者,也是伊利諾伊大學(xué)電氣與計(jì)算機(jī)工程專業(yè)的 Robert C. MacClinchie 特聘教授。

ZyvexLitho1 中嵌入的是我們的 ZyVector。這種具有低噪聲和低延遲的 20 位數(shù)字控制系統(tǒng)使我們的用戶能夠?yàn)楣虘B(tài)量子器件和其他納米器件和材料制作原子級(jí)精確的圖案。完整的 ZyvexLitho1 系統(tǒng)還包括配置用于制造量子器件的 ScientaOmicron 超高真空 STM。

“我期待繼續(xù)與 Zyvex 進(jìn)行富有成效的合作,”ScientaOmicron 產(chǎn)品經(jīng)理 SPM Andreas Bettac 博士評(píng)論道。“在這里,我們將最新的 UHV 系統(tǒng)設(shè)計(jì)和 ScientaOmicron 久經(jīng)考驗(yàn)且成熟的 SPM 與 Zyvex 用于基于 STM 的光刻的專用高精度 STM 控制器相結(jié)合。”

從報(bào)道可以看到,該產(chǎn)品還得到了美國(guó)DARPA(國(guó)防高級(jí)研究計(jì)劃署)、陸軍研究辦公室、能源部先進(jìn)制造辦公室和德克薩斯大學(xué)達(dá)拉斯分校的 Reza Moheimani 教授的支持,后者最近獲得了工業(yè)成就獎(jiǎng)國(guó)際自動(dòng)控制聯(lián)合會(huì)授予“支持在單原子尺度上制造量子硅器件的控制發(fā)展”獎(jiǎng)。

由此可見(jiàn),這個(gè)所謂的0.7nm芯片,可能我傳統(tǒng)意義上的芯片制造工藝是不一樣的。

對(duì)半導(dǎo)體行業(yè)有了解的讀者應(yīng)該清楚,我們平時(shí)所謂的多少納米,其實(shí)是一個(gè)工藝節(jié)點(diǎn)的代號(hào)。通常意義上,這個(gè)代號(hào)是用一個(gè)數(shù)字命名,后跟納米的縮寫,例如7nm、5nm、3nm 等。

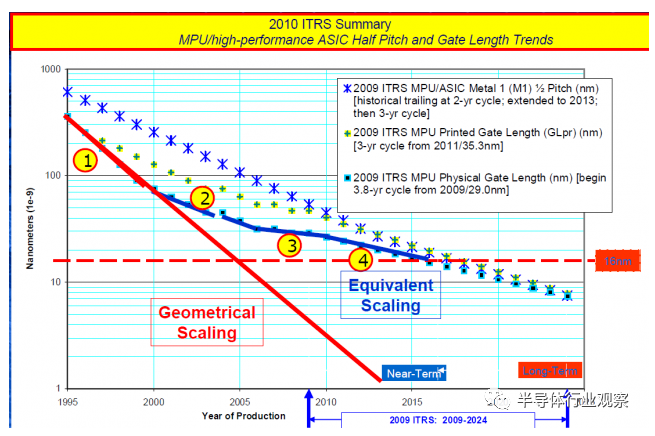

從大約 1960 年代到 1990 年代末,節(jié)點(diǎn)是根據(jù)它們的門長(zhǎng)度命名的。這張來(lái)自 IEEE 的圖表顯示了這種關(guān)系。

半導(dǎo)體制造涉及巨大的資本支出和大量的長(zhǎng)期研究。從論文中引入新技術(shù)方法到大規(guī)模商業(yè)制造之間的平均時(shí)間長(zhǎng)度約為 10-15 年。幾十年前,半導(dǎo)體行業(yè)認(rèn)識(shí)到,如果存在用于節(jié)點(diǎn)引入的通用路線圖以及這些節(jié)點(diǎn)將針對(duì)的特征大小,這將對(duì)每個(gè)人都有好處。這將允許廣泛、同時(shí)開(kāi)發(fā)將新節(jié)點(diǎn)推向市場(chǎng)所需的所有難題。多年來(lái),ITRS(國(guó)際半導(dǎo)體技術(shù)路線圖)發(fā)布了該行業(yè)的總體路線圖(已經(jīng)停止更新了)。這些路線圖跨越 15 年,為半導(dǎo)體市場(chǎng)設(shè)定了總體目標(biāo)。

長(zhǎng)期以來(lái),柵極長(zhǎng)度(晶體管柵極的長(zhǎng)度)和半間距(芯片上兩個(gè)相同特征之間距離的一半)與工藝節(jié)點(diǎn)名稱相匹配,但上一次出現(xiàn)這種情況是在1997 年。pitch 繼續(xù)匹配節(jié)點(diǎn)名稱幾代,但在任何實(shí)際意義上不再與它相關(guān)。

由此可見(jiàn),這在工藝上與我們熟悉的工藝節(jié)點(diǎn)是不太一樣。至于這個(gè)光刻,則是所謂的STM光刻。

繞開(kāi)EUV光刻技術(shù)?

從相關(guān)報(bào)道指出,達(dá)成這個(gè)0.7納米分辨率的光刻系統(tǒng)這是一種稱為氫去鈍化光刻(Hydrogen Depassivation Lithography )的技術(shù),它是一種電子束光刻技術(shù) (EBL),可實(shí)現(xiàn)原子分辨率。

據(jù)維基百科介紹,電子束光刻(通常縮寫EBL)是掃描聚焦電子束以在覆蓋有稱為光刻膠(曝光)的電子敏感膜的表面上繪制自定義形狀的做法。電子束改變了光刻膠的溶解度,通過(guò)將抗蝕劑浸入溶劑中(顯影),可以選擇性地去除曝光或未曝光區(qū)域。與光刻一樣,其目的是在抗蝕劑中創(chuàng)建非常小的結(jié)構(gòu),然后通常通過(guò)蝕刻將其轉(zhuǎn)移到基板材料上。

電子束光刻的主要優(yōu)點(diǎn)是它可以繪制具有sub-10 nm 分辨率的自定義圖案(直接寫入) 。這種形式的無(wú)掩模光刻具有高分辨率和低產(chǎn)量,限制了其用于光掩模制造、半導(dǎo)體器件的小批量生產(chǎn)以及研發(fā)。

據(jù)介紹,該機(jī)器的用途包括為基于量子點(diǎn)的量子比特制作極其精確的結(jié)構(gòu),以實(shí)現(xiàn)最高的量子比特質(zhì)量。該產(chǎn)品可用于其他非量子相關(guān)應(yīng)用,例如構(gòu)建用于生物醫(yī)學(xué)和其他化學(xué)分離技術(shù)的納米孔膜。如上所述,該產(chǎn)品的缺點(diǎn)是吞吐量非常低,換而言之,它可能適合制造小批量的量子處理器芯片,對(duì)于大批量消費(fèi)電子產(chǎn)品來(lái)說(shuō),這不是一個(gè)好的解決方案。

Zyvex Labs在官網(wǎng)中也表示,該系統(tǒng)能夠使原子精密光刻成為現(xiàn)實(shí),當(dāng)中用于 STM 光刻的 UHV 系統(tǒng) 、前體氣體計(jì)量和 Si MBE 、數(shù)字矢量光刻和自動(dòng)化和腳本。他們表示,如果沒(méi)有亞納米分辨率和精度,這種 7.7 納米(10 像素)正方形的曝光是不可能的。

Zyvex Labs指出,ZyvexLitho1 使用氫去鈍化光刻從 Si (100) 2×1 重建表面去除 H 原子。這種自我顯影的曝光技術(shù)本質(zhì)上是二元的。H-Si 鍵要么斷裂(將 H 原子送入真空),要么沒(méi)有。沒(méi)有部分暴露或鄰近效應(yīng)。利用這個(gè)過(guò)程和作為硅表面晶格的全局基準(zhǔn)網(wǎng)格允許數(shù)字光刻。亞納米像素是 4 個(gè)表面硅原子。可以將設(shè)計(jì)網(wǎng)格與我們的像素網(wǎng)格相同的計(jì)算機(jī)輔助設(shè)計(jì) (CAD) 文件加載到 ZyvexLitho1 中,并且可以自動(dòng)將圖案分割成不同的幾何形狀,從而允許尖端矢量與不同的光刻模式一起使用。然后可以自動(dòng)進(jìn)行曝光。

他們還強(qiáng)調(diào),由于光刻模式和成像模式在能量上分離良好,因此可以在光刻前后對(duì)Si表面進(jìn)行成像。這種非曝光成像模式允許自動(dòng)識(shí)別硅晶格,因此可以自動(dòng)識(shí)別像素在表面上的位置。這種 Lattice Lock 過(guò)程自動(dòng)保持尖端定位(以及因此光刻)準(zhǔn)確。

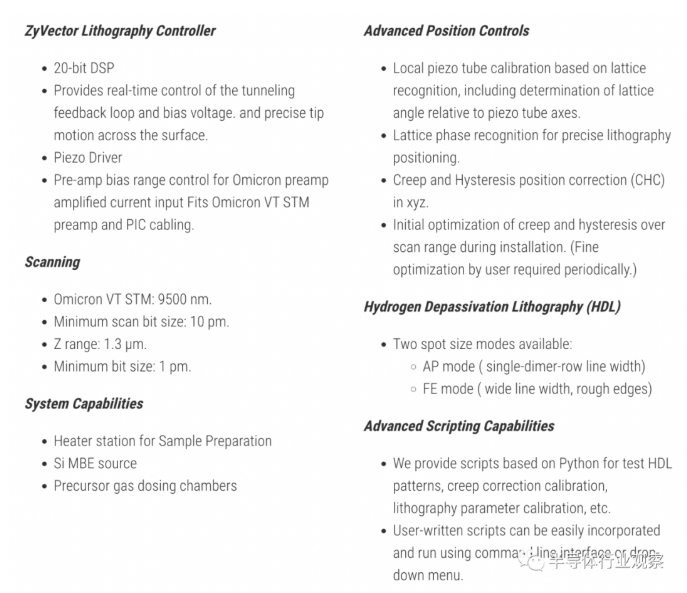

從他們提供的表格上看,該系統(tǒng)擁有以下特點(diǎn):

那么,關(guān)于這個(gè)的討論又來(lái)到了——EBL能取代傳統(tǒng)光刻嗎?

EBL能成為新選擇嗎?

所謂光刻,是芯片制造中的一種圖案化工藝。該過(guò)程涉及將圖案從光掩模轉(zhuǎn)移到基板。這主要是使用配備有光學(xué)光源的步進(jìn)器和掃描儀來(lái)完成的,這也是我們現(xiàn)在主流的芯片制造方式,大家熟悉的EUV和DUV就是使用這種方式的。

其他形式的光刻包括直寫電子束(direct-write e-beam)和納米壓印( nanoimprint)。在研發(fā)中還有幾種下一代光刻(NGL)技術(shù)——如多光束電子束和定向自組裝(DSA)。

據(jù)美國(guó)NIST方面介紹,電子束光刻允許精細(xì)控制納米結(jié)構(gòu)特征,這些特征構(gòu)成多種器件技術(shù)的基礎(chǔ)。讓10 nm 的橫向分辨率、1 nm 的放置精度和 1 mm 的圖案化區(qū)域都是可能的。然而,實(shí)現(xiàn)這些性能指標(biāo)取決于許多特定于樣品的相互依賴的因素——圖案定義和斷裂、基板和掩模材料、曝光前和曝光后工藝、對(duì)準(zhǔn)特征定義——以及關(guān)鍵的細(xì)節(jié)光刻系統(tǒng)的操作。

NIST表示,作為一項(xiàng)核心能力,其開(kāi)發(fā)的工藝處于或接近傳統(tǒng)電子束光刻技術(shù)的極限,以推進(jìn)各個(gè)領(lǐng)域的納米級(jí)設(shè)備和測(cè)量科學(xué),例如:用于精確計(jì)時(shí)的芯片級(jí)頻率梳;用于波長(zhǎng)和量子頻率轉(zhuǎn)換的非線性集成光學(xué);用于傳感、轉(zhuǎn)換和非線性動(dòng)力學(xué)研究的片上腔光機(jī)械和微/納米機(jī)電系統(tǒng);具有用于量子信息的非線性和量子發(fā)射器光源的量子光子集成電路;從紫外到紅外的超表面,用于捕獲和探測(cè)原子和離子、偏振測(cè)量、成像和時(shí)空超快激光脈沖整形;用于像差校正的光學(xué)顯微鏡標(biāo)準(zhǔn)。

但正如很多報(bào)道中所說(shuō),其吞吐和準(zhǔn)確度,限制了EBL的發(fā)展。根據(jù)eBeam Initiative的一份調(diào)查顯示,使用類似電子書光刻這樣的直寫設(shè)備制作一份掩膜寫入時(shí)間大概在2.5到13個(gè)小時(shí)不等,其平均數(shù)在6.8個(gè)小時(shí)。根據(jù)該組織的報(bào)告,對(duì)于復(fù)雜掩膜而言,最長(zhǎng)寫入時(shí)間在14到60個(gè)小時(shí)。一般來(lái)說(shuō),制造商們對(duì)于寫入時(shí)間超過(guò)24個(gè)小時(shí)的掩膜設(shè)計(jì)方案會(huì)比較頭疼。因?yàn)檫^(guò)長(zhǎng)的寫入時(shí)間就意味著更高的成本,更長(zhǎng)的處理時(shí)間和良率問(wèn)題。

在半導(dǎo)體行業(yè)觀察之前的報(bào)道《無(wú)掩膜光刻,有機(jī)會(huì)嗎?》的文章中,我們也對(duì)包括電子束光刻在內(nèi)的技術(shù)進(jìn)行了分析。得出的結(jié)論是,傳統(tǒng)技術(shù)前進(jìn)雖然很難,包括ASML的CTO在文章《EUV光刻機(jī)何去何從》中也承認(rèn)了這一點(diǎn)。

但毫無(wú)疑問(wèn),這依然是芯片制造技術(shù)的主流。

更多信息可以來(lái)這里獲取==>>電子技術(shù)應(yīng)用-AET<<