配置電路

FPGA配置方式靈活多樣,根據(jù)芯片是否能夠自己主動(dòng)加載配置數(shù)據(jù)分為主模式、從模式以及JTAG模式。典型的主模式都是加載片外非易失( 斷電不丟數(shù)據(jù)) 性存儲(chǔ)器中的配置比特流,配置所需的時(shí)鐘信號( 稱為CCLK) 由FPGA內(nèi)部產(chǎn)生,且FPGA控制整個(gè)配置過程。從模式需要外部的主智能終端( 如處理器、微控制器或者DSP等) 將數(shù)據(jù)下載到FPGA中,其最大的優(yōu)點(diǎn)就是FPGA 的配置數(shù)據(jù)可以放在系統(tǒng)的任何存儲(chǔ)部位,包括:Flash、硬盤、網(wǎng)絡(luò),甚至在其余處理器的運(yùn)行代碼中。JTAG 模式為調(diào)試模式,可將PC 中的比特文件流下載到FPGA中,斷電即丟失。此外,目前賽靈思還有基于Internet 的、成熟的可重構(gòu)邏輯技術(shù)System ACE解決方案。

(1) 主模式

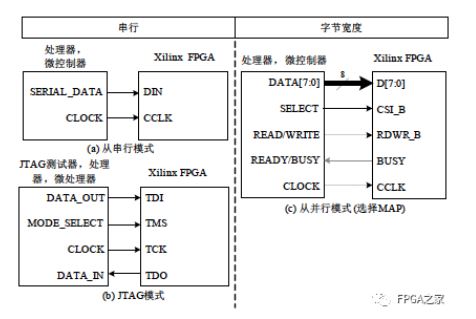

在主模式下,F(xiàn)PGA上電后,自動(dòng)將配置數(shù)據(jù)從相應(yīng)的外存儲(chǔ)器讀入到SRAM中,實(shí)現(xiàn)內(nèi)部結(jié)構(gòu)映射;主模式根據(jù)比特流的位寬又可以分為:串行模式( 單比特流) 和并行模式( 字節(jié)寬度比特流) 兩大類。如:主串行模式、主SPI Flash 串行模式、內(nèi)部主SPI Flash串行模式、主BPI 并行模式以及主并行模式,如圖5-19所示。

(2) 從模式

在從模式下,F(xiàn)PGA 作為從屬器件,由相應(yīng)的控制電路或微處理器提供配置所需的時(shí)序,實(shí)現(xiàn)配置數(shù)據(jù)的下載。從模式也根據(jù)比特流的位寬不同分為串、并模式兩類,具體包括:從串行模式、JTAG模式和從并行模式三大類,其概要說明如圖5-20所示。

(3)JTAG模式

在JTAG模式中,PC和FPGA通信的時(shí)鐘為JTAG接口的TCLK,數(shù)據(jù)直接從TDI進(jìn)入FPGA,完成相應(yīng)功能的配置。

圖5-19 常用主模式下載方式示意圖

圖5-20 常用的從模式下載方式示意圖

目前,主流的FPGA芯片都支持各類常用的主、從配置模式以及JTAG,以減少配置電路失配性對整體系統(tǒng)的影響。在主配置模式中,F(xiàn)PGA自己產(chǎn)生時(shí)鐘,并從外部存儲(chǔ)器中加載配置數(shù)據(jù),其位寬可以為單比特或者字節(jié);在從模式中,外部的處理器通過同步串行接口,按照比特或字節(jié)寬度將配置數(shù)據(jù)送入FPGA芯片。此外,多片F(xiàn)PGA可以通過JTAG菊花鏈的形式共享同一塊外部存儲(chǔ)器,同樣一片/ 多片F(xiàn)PGA也可以從多片外部存儲(chǔ)器中讀取配置數(shù)據(jù)以及用戶自定義數(shù)據(jù)。

Xilinx FPGA的常用配置模式有5 類:主串模式、從串模式、Select MAP模式、Desktop配置和直接SPI配置。在從串配置中,F(xiàn)PGA接收來自于外部PROM或其它器件的配置比特?cái)?shù)據(jù),在FPGA產(chǎn)生的時(shí)鐘CCLK的作用下完成配置,多個(gè)FPGA可以形成菊花鏈,從同一配置源中獲取數(shù)據(jù)。Select MAP模式中配置數(shù)據(jù)是并行的,是速度最快的配置模式。SPI配置主要在具有SPI接口的FLASH電路中使用。下面以Spartan-3E系列芯片為例,給出各種模式的配置電路。

5.5.2 主串模式——最常用的FPGA配置模式

1.配置單片F(xiàn)PGA

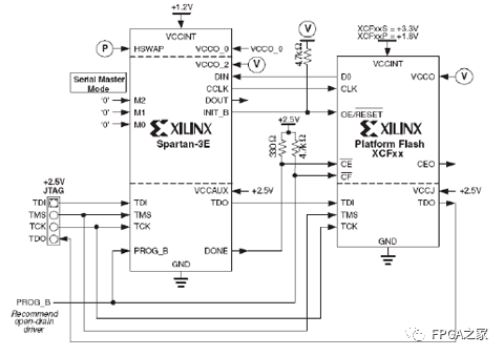

在主串模式下,由FPGA的CCLK管腳給PROM提供工作時(shí)鐘,相應(yīng)的PROM在CCLK的上升沿將數(shù)據(jù)從D0管腳送到FPGA的DIN管腳。無論P(yáng)ROM芯片類型( 即使其支持并行配置),都只利用其串行配置功能。Spartan3E系列FPGA的單片主串配置電路如圖5-21所示。主串模式是賽靈思公司各種配置方式中最簡單,也最常用的方式,基本所有的可編程芯片都支持主串模式。

圖5-21 Spartan-3E主串模式配置電路

2.配置電路的關(guān)鍵點(diǎn)

主串配置電路最關(guān)鍵的3點(diǎn)就是JTAG鏈的完整性、電源電壓的設(shè)置以及CCLK信號的考慮。只要這3步任何一個(gè)環(huán)節(jié)出現(xiàn)問題,都不能正確配置PROM芯片。

(1)JTAG鏈的完整性

FPGA和PROM芯片都有自身的JTAG接口電路,所謂的JTAG鏈完整性指的是將JTAG連接器、FPGA、PROM的TMS、TCK連在一起,保證從JTAG連接器TDI到其TDO之間,形成JTAG連接器的“TDI →(TDI~TDO) → (TDI~TDO) → JTAG連接器TDO”的閉合回路,其中(TDI~TDO) 為FPGA或者PROM芯片自身的一對輸入、輸出管腳。圖5-12中配置電路的JTAG鏈從連接器的TDI到FPGA的TDI,再從FPGA的TDO到PROM的TDI,最后從PROM的TDO到連接器的TDO,形成了完整的JTAG鏈,F(xiàn)PGA芯片被稱為鏈?zhǔn)仔酒R部梢愿鶕?jù)需要調(diào)換FPGA和PROM的位置,使PROM成為鏈?zhǔn)仔酒?/p>

(2) 電源適配性

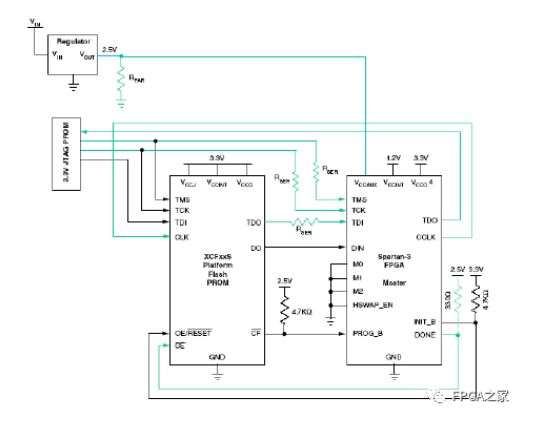

如圖5-22所示,由于FPGA和PROM要完成數(shù)據(jù)通信,二者的接口電平必須一致,即FPGA相應(yīng)分組的管腳電壓Vcco_2必須和PROM Vcco的輸入電壓大小一致,且理想值為2.5V,這是由于FPGA的PROG_B和DONE管腳由2.5V的Vccaux供電。此外,由于JTAG連接器的電壓也由2.5V的Vccaux提供,因此PROM的VCCJ也必須為2.5V。因此,如果接口電壓和參考電壓不同,在配置階段需要將相應(yīng)分組的管腳電壓和參考電壓設(shè)置為一致;在配置完成后,再將其切換到用戶所需的工作電壓。當(dāng)然,F(xiàn)PGA和PROM也可以自適應(yīng)3.3V的I/O電平以及JTAG電平,但需要進(jìn)行一定的改動(dòng),即添加幾個(gè)外部限流電阻,如圖5-22所示。在主串模式下,XCFxxS系列PROM的核電壓必須為3.3V,XCFxxP系列PROM的核電壓必須為1.8V。

圖5-22 3.3V的JTAG配置電路示意圖

圖5-22中的RSER、RPAR這兩個(gè)電阻要特別注意。首先,RSER= 68Ω將流入每個(gè)輸入的電流限制到9.5mA ;其次,N= 3三個(gè)輸入的二極管導(dǎo)通,

RPAR = VCCAUX min/ NIIN = 2.375V/(3*9.5mA)

=83 Ω或82 Ω ( 與標(biāo)準(zhǔn)值誤差小于5%的電阻 )

(3)CCLK的信號完整性

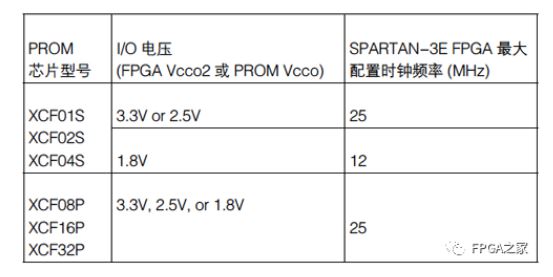

CCLK信號是JTAG配置數(shù)據(jù)傳輸?shù)臅r(shí)鐘信號,其信號完整性非常關(guān)鍵。FPGA 配置電路剛開始以最低時(shí)鐘工作,如果沒有特別指定,將逐漸提高頻率。CCLK信號是由FPGA內(nèi)部產(chǎn)生的,對于不同的芯片和電平,其最大值如表F-1所示。

表5-1 不同PROM芯片的最大配置時(shí)鐘頻率

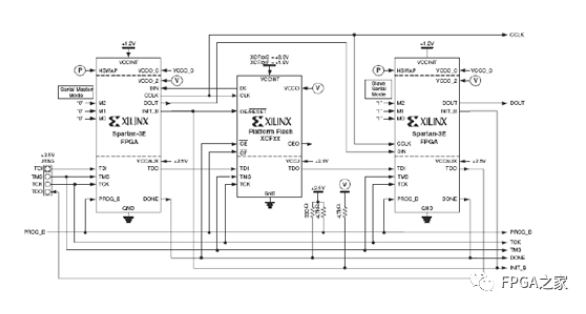

3.配置多片F(xiàn)PGA

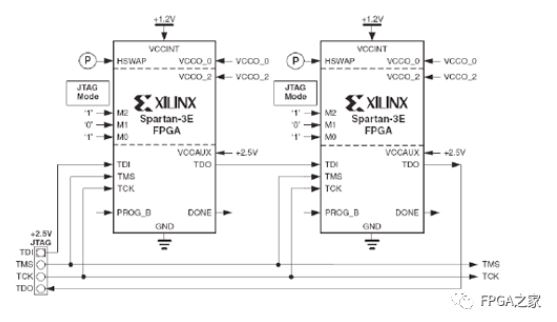

多片F(xiàn)PGA的配置電路和單片的類似,但是多片F(xiàn)PGA之間有主(Master)、從(Slave) 之分,且需要選擇不同的配置模式。兩片Spartan 3E系列FPGA的典型配置電路如圖5-23所示,兩片F(xiàn)PGA存在主、從地位之分。

圖5-23 主從模式下兩片F(xiàn)PGA的配置電路

5.5.3 SPI串行Flash配置模式

1.SPI串行配置介紹

串行Flash的特點(diǎn)是占用管腳比較少,作為系統(tǒng)的數(shù)據(jù)存貯非常合適,一般都是采用串行外設(shè)接口(SPI 總線接口)。Flash 存貯器與EEPROM根本不同的特征就是EEPROM可以按字節(jié)進(jìn)行數(shù)據(jù)的改寫,而Flash只能先擦除一個(gè)區(qū)間,然后改寫其內(nèi)容。一般情況下,這個(gè)擦除區(qū)間叫做扇區(qū)(Sector),也有部分廠家引入了頁面(Page) 的概念。選擇Flash產(chǎn)品時(shí),最小擦除區(qū)間是比較重要的指標(biāo)。在寫入Flash時(shí),如果寫入的數(shù)據(jù)不能正好是一個(gè)最小擦除區(qū)間的尺寸,就需要把整個(gè)區(qū)間的數(shù)據(jù)全部保存另外一個(gè)存貯空間,擦除這個(gè)空間,然后才能重新對這個(gè)區(qū)間改寫。大多數(shù)Flash工藝更容易實(shí)現(xiàn)較大的擦除區(qū)間,因此較小擦除區(qū)間的Flash 其價(jià)格一般會(huì)稍貴一些。此外,SPI是標(biāo)準(zhǔn)的4線同步串行雙向總線,提供控制器和外設(shè)之間的串行通信數(shù)據(jù)鏈路,廣泛應(yīng)用于嵌入式設(shè)備中。

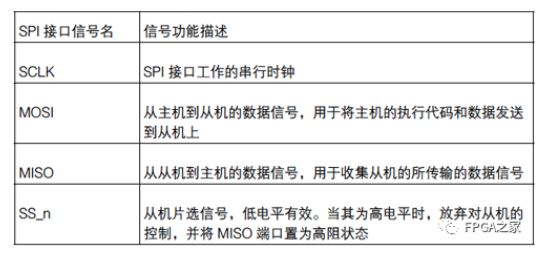

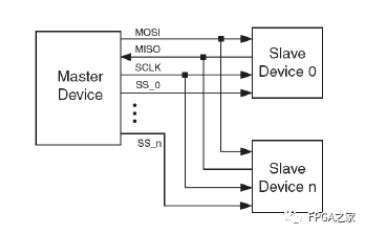

賽靈思公司的新款FPGA都支持SPI接口。SPI總線通過4根信號線來完成主、從之間的通信,典型的SPI系統(tǒng)中常包含一個(gè)主設(shè)備以及至少一個(gè)從設(shè)備,在FPGA應(yīng)用場合中,F(xiàn)PGA芯片為主設(shè)備,SPI 串行FLASH為從設(shè)備。4個(gè)SPI接口信號的名稱和功能如表5-2所示。

表5-2 SPI接口信號列表

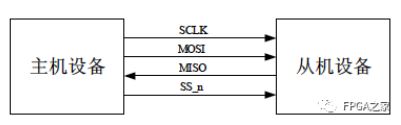

一個(gè)主芯片和一個(gè)從芯片的通信接口如圖5-24所示。FPGA通過SCLK控制雙方通信的時(shí)序,在SS_n為低時(shí),F(xiàn)PGA通過MOSI 信號線將數(shù)據(jù)傳送到FLASH,在同一個(gè)時(shí)鐘周期中,F(xiàn)LASH通過SOMI將數(shù)據(jù)傳輸?shù)紽PGA芯片。無論主、從設(shè)備,數(shù)據(jù)都是在時(shí)鐘電平跳轉(zhuǎn)時(shí)輸出,并在下一個(gè)相反的電平跳轉(zhuǎn)沿,送入另外一個(gè)芯片。

圖5-24 SPI接口連接示意圖

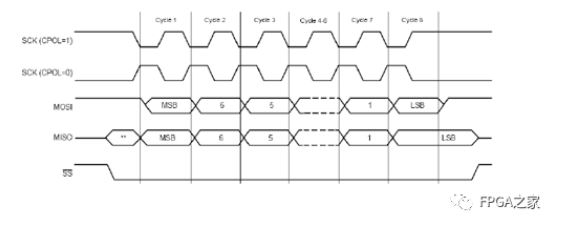

其中SCLK信號支持不同的速率,一般常采用20MHz。通過SPI 接口中的CPOL和CPHA這兩個(gè)比特定義了4種通信時(shí)序。其中,CPOL信號定義了SCLK的空閑狀態(tài),當(dāng)CPOL為低時(shí),SCLK的低電平為空閑狀態(tài),否則其空閑狀態(tài)為高電平;CPHA定義了數(shù)據(jù)有效的上升沿位置,當(dāng)其為低時(shí),數(shù)據(jù)在第1 個(gè)電平跳轉(zhuǎn)沿有效,否則數(shù)據(jù)在第2個(gè)電平跳轉(zhuǎn)沿有效。其相應(yīng)的時(shí)序邏輯如圖5-25所示。

圖5-27 CPHA為低時(shí)SPI的總線時(shí)序示意圖

圖5-28 CPHA為高時(shí)SPI的總線時(shí)序示意圖

可以通過增加片選信號SS_n的位寬來支持多個(gè)從設(shè)備,SS_n的位寬等于從設(shè)備的個(gè)數(shù)。對于某時(shí)刻被選中的從設(shè)備和主設(shè)備而言,其讀寫時(shí)序邏輯和圖5-29一樣。

圖5-29 多個(gè)從芯片的連接電路圖

SPI串行FLASH作為一種新興的高性能非易失性存儲(chǔ)器,其有效讀寫次數(shù)高達(dá)百萬次,不僅引腳數(shù)量少、封裝小、容量大,可以節(jié)約電路板空間,還能夠降低功耗和噪聲。從功能上看,可以用于代碼存儲(chǔ)以及大容量的數(shù)據(jù)和語音存儲(chǔ),對于以讀為主,僅有少量擦寫和寫入時(shí)間的應(yīng)用來說,支持分區(qū)( 多頁) 擦除和頁寫入的串行存儲(chǔ)是最佳方案。

2.SPI串行FLASH配置電路

SPI串行配置模式常用于已采用了SPI串行FLASH PROM的系統(tǒng),在上電時(shí)將配置數(shù)據(jù)加載到FPGA中,這一過程只需向SPI串行發(fā)送一個(gè)4字節(jié)的指令,其后串行FLASH中的數(shù)據(jù)就像PROM配置方式一樣連續(xù)加載到FPGA中。一旦配置完成,SPI中的額外存儲(chǔ)空間還能用于其它應(yīng)用目的。

1)SPI 配置電路

雖然SPI接口是標(biāo)準(zhǔn)的4線接口,但不同的SPI FLASH PROM芯片采用了不同的指令協(xié)議。FPGA芯片通過變量選擇信號VS[2:0] 來定義FPGA和SPI FLASH的通信方式、FPGA的讀指令以及在有效接收數(shù)據(jù)前插入的冗余比特?cái)?shù)。常用SPI FLASH與FPGA的有效操作配置如表5-3所示,其余的VS[2:0] 配置留有它用。

表5-3 賽靈思芯片所支持的SPI FLASH存儲(chǔ)器以及配置列表

從整體上看來,控制SPI串行閃存比較容易,只需要使用簡單的指令就能完成讀取、擦除、編程、寫使能/禁止以及其它功能。所有的指令都是通過4 個(gè)SPI 引腳串行移位輸入的。

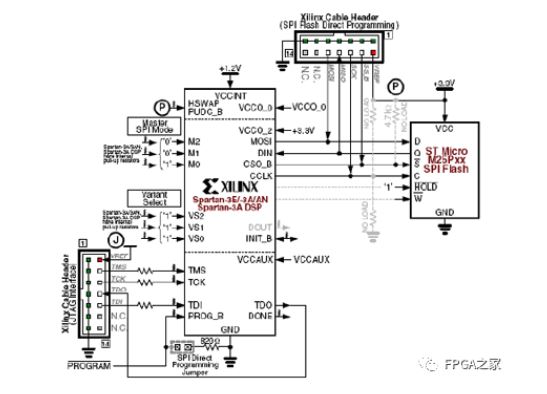

圖5-30 支持快讀寫的串行FLASH配置電路示意圖

不同型號的FPGA芯片具有數(shù)目不同的從設(shè)備片選信號,因此所掛的串行芯片數(shù)目也就不一樣。例如:Spartan-3E系列FPGA芯片只有1位SPI從設(shè)備片選信號,因此只能外掛一片SPI串行FLASH芯片。在SPI串行FLASH配置模式下,M[2:0]=3'b001。FPGA 上電后,通過外部SPI 串行FLASH PROM完成配置,配置時(shí)鐘信號由FPGA芯片提供時(shí)鐘信號,支持兩類業(yè)界常用的FLASH。

圖5-30給出了Spartan3E系列FPGA支持0X0B快速讀寫指令的STMicro 25系列PROM的典型配置電路。其中的Flash芯片需要Flash編程器來加載配置數(shù)據(jù);單片的FPGA芯片構(gòu)成了完整的JTAG鏈,僅用來測試芯片狀態(tài),以及支持JTAG在線調(diào)試模式,與SPI配置模式?jīng)]有關(guān)系。

從中可以看出,SPI Flash容量大,適合于大規(guī)模設(shè)計(jì)場合。但由于SPI配置需要專門的Flash編程器,且操作起來比較麻煩,不適合在產(chǎn)品研發(fā)階段調(diào)試FPGA芯片,因此一般還會(huì)添加JTAG鏈專門用于在線調(diào)試。

圖5-31 Atmel SPI串行FLASH配置電路示意圖

圖5-31給出了Spartan3E系列FPGA支持SPI協(xié)議的Atmel公司“C”、“D”系列串行Flash芯片的典型配置電路。這兩個(gè)系列的FLASH芯片可以工作在很低溫度,具有短的時(shí)鐘建立時(shí)間。同樣,單片的FPGA芯片構(gòu)成了完整的JTAG鏈,僅用來測試芯片狀態(tài),以及支持JTAG在線調(diào)試模式,與SPI 配置模式?jīng)]有關(guān)系。

表5-3給出了SPI配置接口的連線說明,每個(gè)SPI Flash PROM采用的名字略有不同,SPI Flash PROM的寫保護(hù)信號和保持控制信號在FPGA配置階段是不用的。其中HOLD管腳在配置階段必須為高,為了編程Flash存儲(chǔ)器,寫保護(hù)信號必須為高。

5.5.4 從串配置模式

在串行模式下,需要微處理器或微控制器等外部主機(jī)通過同步串行接口將配置數(shù)據(jù)串行寫入FPGA芯片,其模式選擇信號M[2:0]=3'b111。典型的Spartan 3E系列FPGA單片配置電路如圖5.5.11所示。DIN輸入管腳的串行配置數(shù)據(jù)需要在外部時(shí)鐘CCLK 信號前有足夠的建立時(shí)間。其中單片F(xiàn)PGA 芯片構(gòu)成了完整的JTAG鏈,僅用來測試芯片狀態(tài),以及支持JTAG 在線調(diào)試模式,與從串配置模式?jīng)]有關(guān)系。外部主機(jī)通過下拉PROG_B啟動(dòng)配置并檢測INIT_B 電平,當(dāng)INIT_B 為高時(shí),表明FPGA 做好準(zhǔn)備,開始接收數(shù)據(jù)。此時(shí),主機(jī)開始提供數(shù)據(jù)和時(shí)鐘信號直到FPGA 配置完畢且DONE 管腳為高,或者INIT_B 變低表明發(fā)生配置錯(cuò)誤才停止。整個(gè)過程需要比配置文件大小更多的時(shí)鐘周期,這是由于部分時(shí)鐘用于時(shí)序建立,特別當(dāng)FPGA 被配置為等待DCM鎖存其時(shí)鐘輸入。

圖5-32 FPGA從串配置電路示意圖

此外,從串配置模式也可配置多片F(xiàn)PGA芯片,典型的兩片Spartan 3E系列FPGA的從串配置電路如圖5-33所示。所有芯片的CCLK信號都有主控設(shè)備提供,靠近主控設(shè)備的FPGA要充當(dāng)橋梁的作用,將配置數(shù)據(jù)轉(zhuǎn)發(fā)到第二個(gè)FPGA芯片。可以看到采用從串配置的好處主要在于節(jié)省電路板面積,并使得系統(tǒng)具備更大的靈活性。

圖5-33 多片F(xiàn)PGA從串模式配置電路

5.5.5 JTAG配置模式

1.JTAG配置電路

賽靈思公司的FPGA芯片具有IEEE 1149.1/1532協(xié)議所規(guī)定的JTAG接口,只要FPGA上電,不論模式選擇管腳M[2:0] 的電平,都可用采用該配置模式。但是將模式配置管腳設(shè)置為JTAG模式,即M[2:0]=3'b101時(shí),F(xiàn)PGA芯片上電后或者PROG_B管腳有低脈沖出現(xiàn)后,只能通過JTAG模式配置。JTAG模式不需要額外的掉電非易失存儲(chǔ)器,因此通過其配置的比特文件在FPGA斷電后即丟失,每次上電后都需要重新配置。由于JTAG模式已更改,配置效率高,是項(xiàng)目研發(fā)階段必不可少的配置模式。典型的Spartan 3E系列芯片的JTAG配置電路如圖5-34所示。

圖5-34 JTAG模式配置電路示意圖

5.5.6 System ACE配置方案

隨著FPGA成為系統(tǒng)級解決方案的核心,大型、復(fù)雜設(shè)備常需要多片大規(guī)模的FPGA。如果使用PROM進(jìn)行配置,需要很大的PCB面積和高昂的成本,因此很多情況下都利用微處理由從模式配置FPGA芯片,但該配置方案容易出現(xiàn)總線競爭且延長了系統(tǒng)啟動(dòng)時(shí)間。為了解決大規(guī)模FPGA的配置問題,賽靈思公司推出了系統(tǒng)級的System ACE(Advanced ConfiguraTIon Environment) 解決方案。

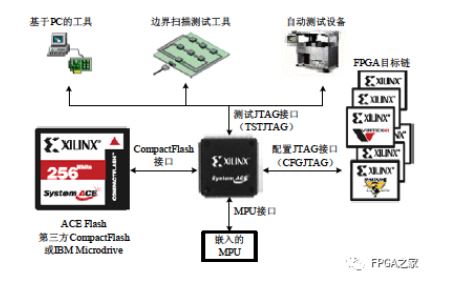

System ACE可在一個(gè)系統(tǒng)內(nèi),甚至在多個(gè)板上,對賽靈思的所有FPGA進(jìn)行配置,使用Flash存儲(chǔ)卡或微硬盤保存配置數(shù)據(jù),通過System ACE控制器把數(shù)據(jù)配置到FPGA中。目前,System ACE有System ACE

CF(Compact Flash)、System ACE SC(Soft Controller) 以及System ACE MPM(MuTI-Package Module) 三種。讀者需要注意的是:System ACE SC/MPM 是和System ACE CF 獨(dú)立的解決方案。典型的ACE 接口以及系統(tǒng)組成如圖5-35 所示。

圖5-35 典型的ACE接口以及系統(tǒng)組成示意圖

1.System ACE CF解決方案

System ACE CF的核心是System ACE CF存儲(chǔ)設(shè)備和System ACE控制器芯片。System ACE CF存儲(chǔ)設(shè)備包括賽靈思的ACE Flash卡或其它廠家的Compact Flash卡以及IBM的微硬盤。Compact Flash卡的容量為32MB~4GB,微硬盤的容量為2GB~6GB,至少可配置數(shù)百片F(xiàn)PGA芯片。

System ACE CF控制器提供了存儲(chǔ)單元和FPGA器件之間的接口,PC和存儲(chǔ)器的標(biāo)準(zhǔn)JTAG接口。控制器芯片默認(rèn)的配置模式也是通過邊界掃描的方式將數(shù)據(jù)配置到FPGA 鏈中,同樣可由邊界掃描鏈的測試和編程接口來輔助進(jìn)行系統(tǒng)原形的調(diào)試,其主要特點(diǎn)有:

- 支持賽靈思所有FPGA芯片的配置;

- 以最小的PC板空間實(shí)現(xiàn)多達(dá)8Gb的配置 ;

- 包括高達(dá)152Mbps的配置速率;

- 利用帶有嵌入式處理器核的FPGA進(jìn)行系統(tǒng)調(diào)節(jié);

- 管理多個(gè)比特流( 全部或部分),并按需要對其進(jìn)行激活;

- 包含處理器核初始化;

- 軟件存儲(chǔ)加密;

- 可移動(dòng)存儲(chǔ)器件;

- 降低了定制配置系統(tǒng)的成本,支持大多數(shù) CompactFlash卡,包括Microdrive單元;包含內(nèi)置式微處理器接口,可以直接調(diào)整FPGA配置;釋放設(shè)計(jì)資源。

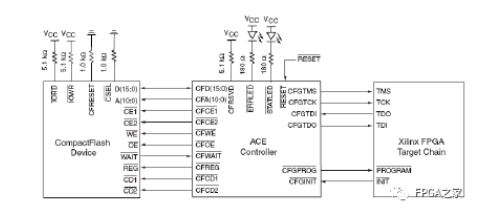

圖5-36 System ACE CF配置電路示意圖

Compact Flash接口是ACE控制器的關(guān)鍵接口,可連接Compact Flash卡、標(biāo)準(zhǔn)的Compact Flash模塊以及IBM微硬盤。Compact Flash可以進(jìn)行拆卸,因此對存儲(chǔ)內(nèi)容進(jìn)行修改和升級以及更換容量都非常方便。Compact Flash接口由Compact Flash控制器和Compact Flash仲裁器兩部分組成。由System ACE CF配置FPGA的接口電路如圖5-36所示。

2.System ACE SC解決方案

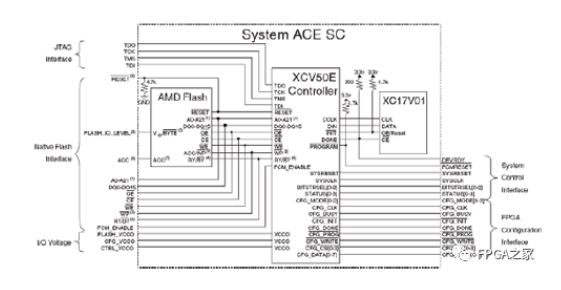

System ACE SC為用戶提供了自主性,用戶可以自由地選擇每一部分的元件,可將其置于電路板的任何位置,且所有的功能在一個(gè)獨(dú)立的FPGA中完成,并不需要整合其他組件。System ACE SC有4個(gè)主要接口:邊界掃描JTAG接口、系統(tǒng)控制接口、Flash存儲(chǔ)器接口以及FPGA 接口,如圖5-37所示。

圖5-37 System ACE SC接口示意圖

其中JTAG接口主要提供邊界掃描測試和對具有JTAG接口的Flash存儲(chǔ)器通信;Flash接口主要和外邊的Flash芯片通信,讀取存儲(chǔ)器內(nèi)的內(nèi)容以及對存儲(chǔ)器進(jìn)行編程;系統(tǒng)控制接口主要提供輸入時(shí)鐘、配置控制信號和配置狀態(tài)信號等;FPGA 接口主要用于配置FPGA,可通過從串、從并以及Selec tMAP等配置模式。

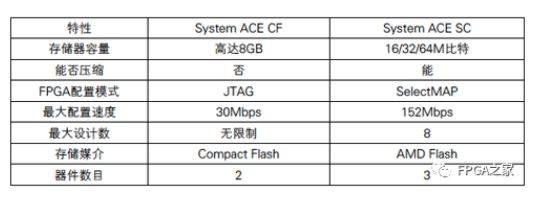

System ACE SC和System ACE CF的主要區(qū)別在于,System ACE SC的控制器是一個(gè)軟核邏輯,而不是芯片,需要和設(shè)計(jì)一起下載到FPFA中。其余區(qū)別如表5-4所列。

表5-4 System ACE CF和System ACE SC的區(qū)別

典型的System ACE SC 配置電路如圖5-38 所示。

圖5-38 System ACE SC配置電路示意圖

3.System ACE MPM解決方案

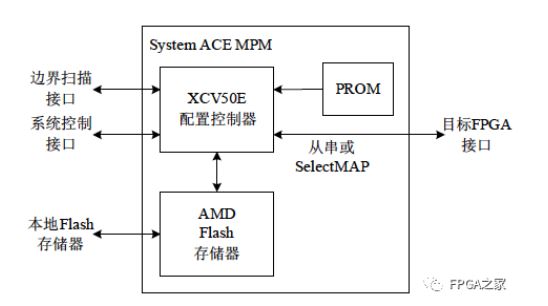

System ACE MPM是一個(gè)整合的組件解決方案,包括FPGA和PROM組成的配置控制組件和一個(gè)Flash存儲(chǔ)組件,并封裝為一個(gè)模塊,通過盡可能少的組件來實(shí)現(xiàn)配置電路。賽靈思公司有16M、32M 以及64M位低密度的System ACE MPM。System ACE MPM 有4 個(gè)主要接口,和System ACE SC 的接口一樣,其特征和功能也與System ACE SC 一樣。二者的區(qū)別在于:System ACE MPM 封裝了整個(gè)配置模塊,而System ACE SC 允許用戶自行配置,其接口電路如圖5-39 所示。

圖5-39 System ACE MPM接口電路示意圖

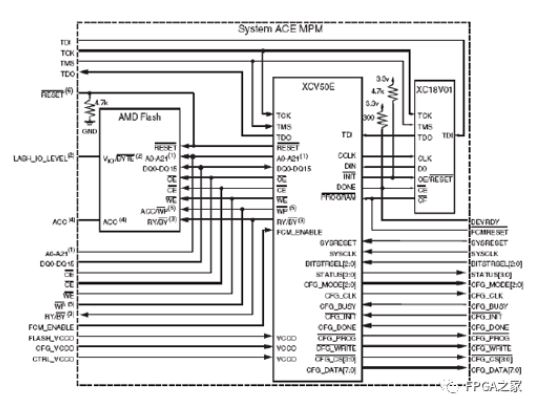

System ACE MPM是賽靈思公司第一個(gè)支持位流壓縮的配置方案,支持多種配置模式,同時(shí)可多達(dá)8個(gè)FPGA鏈的從串配置模式和多達(dá)4個(gè)FPGA的Select MAP配置模式,最大配置速率為152Mbps,同時(shí)又可最大限度地減小電路板空間和連線。典型的System ACE MPM 配置電路如圖5-40所示。總之,System ACE技術(shù)簡化了大型FPGA 系統(tǒng)的配置方案,令開發(fā)人員將精力主要集中在系統(tǒng)性能的提高和開發(fā)時(shí)間的縮短。

圖5-40 System ACE MPM配置電路示意圖

更多信息可以來這里獲取==>>電子技術(shù)應(yīng)用-AET<<