FPGA是一個(gè)很特殊的芯片,可能在2個(gè)月前,我還對(duì)它一無(wú)所知。我們熟知的芯片都是CPU,GPU,或者知道ASIC的概念。但實(shí)際上,F(xiàn)PGA已經(jīng)走過了30個(gè)年頭,它目前已經(jīng)成為一個(gè)包含各種先進(jìn)電路,邏輯單元,接口,芯片封裝,制造等技術(shù)的“集大成者”。在硬件不斷發(fā)展的同時(shí),F(xiàn)PGA的開發(fā)軟件和設(shè)計(jì)工具也在不斷迭代和更新。基于硬件描述語(yǔ)言HDL,抽象出HLS(High-Level Synthesis)(翻譯為高層次綜合?怎么聽起來都沉得別扭)技術(shù),通過高層設(shè)計(jì)去隱藏很多底層邏輯和細(xì)節(jié),讓FPGA的開發(fā)更加簡(jiǎn)單。即使這樣,F(xiàn)PGA開發(fā)還是同CPU,GPU不一樣,它需要設(shè)計(jì)者在一定程度上了解FPGA的內(nèi)部架構(gòu),這樣才能引導(dǎo)高層語(yǔ)言綜合工具睡時(shí)到優(yōu)化的系統(tǒng)性能。

一:開發(fā)FPGA的痛點(diǎn)

首先,F(xiàn)PGA的體量非常大,大得驚人,英特爾最新的StraTIx10 GX 10M 有 433億只晶體管,1020萬(wàn)個(gè)可編程邏輯單元,以及2304個(gè)可編程的I/O接口。這些數(shù)量龐大的晶體管組成了大量的可編程邏輯單元和查找表結(jié)構(gòu),大量運(yùn)算單元,各種類型和大小的內(nèi)存資源,高速串行I/O,多個(gè)嵌入式處理器,還有成百上午種不同功能的軟核和硬核IP。因?yàn)榭删幊蹋梢酝ㄟ^定制實(shí)現(xiàn)極高吞吐量和極低的功耗。

當(dāng)這么多硬件資源都集成到了一個(gè)芯片上,用戶如何對(duì)這些硬件進(jìn)行編程呢?

通常來說,我們要解決一個(gè)復(fù)雜問題,常用的辦法就是分解任務(wù),我們需要?jiǎng)澐智宄男┦窃谟布贤瓿桑男┩ㄟ^軟件完成。在FPGA,這種分解非常困難和復(fù)雜。例如:哪部分用編程邏輯(硬件),哪部分使用片上的芯片。如何合理分配片上內(nèi)存,內(nèi)不足時(shí),如何優(yōu)化……

如何降低FPGA的開發(fā)難度,EDA軟件一定要好用,所以,不管英特爾還是賽靈思,包括我了解的一個(gè)新創(chuàng)團(tuán)隊(duì),都會(huì)在EDA軟件團(tuán)隊(duì)上做大力投入,甚至做EDA軟件開發(fā)的人員要多于FPGA本身的工程師數(shù)量。另外,業(yè)界也出現(xiàn)了大量的第三方公司,負(fù)責(zé)FPGA設(shè)計(jì)咨詢公司,IP提供商,外包公司等……,業(yè)務(wù)已經(jīng)發(fā)展產(chǎn)生了很多特定的分工。

當(dāng)前,F(xiàn)PGA還在進(jìn)入更多的市場(chǎng),比如:嵌入式應(yīng)用,5G和汽車市場(chǎng),這些領(lǐng)域中的大多數(shù)開發(fā)團(tuán)隊(duì)都沒有FPGA相關(guān)的設(shè)計(jì)專業(yè)知識(shí)和經(jīng)驗(yàn)。而且,他們更多是純軟件開發(fā),更多依賴于人工智能技術(shù)。這些也使得FPGA的開發(fā)難度被放大。

二:HLS——讓軟件工程師開發(fā)FPGA

HLS指的是通過EDA工具,將描述的邏輯結(jié)構(gòu)轉(zhuǎn)換成低抽象級(jí)語(yǔ)言描述的電路模型的過程。

這里,我不得不再?gòu)?qiáng)調(diào)一下HLS的概念,因?yàn)橛洸蛔。悴惶?/p>

High-Level Synthesis 簡(jiǎn)稱:HLS 指的是將高層次語(yǔ)言描述的邏輯結(jié)構(gòu),自動(dòng)轉(zhuǎn)換成低抽象級(jí)語(yǔ)言描述的電路模型的過程。有點(diǎn)象我們軟件領(lǐng)域講的 Java 語(yǔ)法在運(yùn)行時(shí),根據(jù)不同的機(jī)器翻譯成不同的機(jī)器字節(jié)碼。所謂高層次語(yǔ)言,通常指的是 C,C++,SystemC等,通常有點(diǎn)較高的抽象度,并且往往不具有時(shí)鐘或時(shí)序的概念,相比之下,諸如Verilog,VHDL,SystemVerilog等低層次語(yǔ)言,通常用來描述時(shí)鐘周期精準(zhǔn)的寄存器傳輸級(jí)電路模型,這也就是當(dāng)前ASIC或者FPGA設(shè)計(jì)最為普遍使用的電路建模和描述方法。

為什么要使用HLS?

1: 這是一個(gè)趨勢(shì)。因?yàn)榧呻娐返膹?fù)雜度太高,已經(jīng)逐漸超過人類可以手工管理的范疇。使用RTL代碼,代碼行過多,不現(xiàn)實(shí)。而使用C,C++ 等高層語(yǔ)言,可以將代碼縮至10%。

根據(jù)NEC2004年發(fā)布的研究,一個(gè)擁有100萬(wàn)邏輯門的芯片設(shè)計(jì)通常要編寫30萬(wàn)行RTL代碼。

2: 高層語(yǔ)言更善于復(fù)用,特別是對(duì)于IP的重用。

因?yàn)閭鹘y(tǒng)的RTL的IP 往往需要定義固定的架構(gòu)和接口標(biāo)準(zhǔn),在IP重用時(shí),需要大量的時(shí)間運(yùn)行系統(tǒng)互聯(lián)和接口驗(yàn)證。高層語(yǔ)言屏蔽了這些要求,轉(zhuǎn)而由HLS工具具體來負(fù)責(zé)完成。現(xiàn)代FPGA有大量的IP單元,這些IP有固定功能,一定需要大量復(fù)用。

3: HLS能幫到軟件和算法工程師參與主導(dǎo)芯片設(shè)計(jì),這是因?yàn)镠LS能夠屏蔽實(shí)現(xiàn)細(xì)節(jié)。對(duì)于硬件工程師,HLS也能幫助他們快速設(shè)計(jì)迭代,專注于性能,面積或功耗模塊,不用關(guān)注上層的算法實(shí)現(xiàn)。

我們?cè)谡凥LS前,先看看RTL的發(fā)展:

通過描述寄存器到寄存器之間的邏輯功能描述電路的HDL層次。RTL級(jí)是比門級(jí)更高的抽象層次,使用RTL級(jí)語(yǔ)言描述硬件電路一般比門級(jí)描述簡(jiǎn)單高效得多。這個(gè)時(shí)期,工程師們都在關(guān)注RTL。

HLS經(jīng)過發(fā)展,產(chǎn)生了以C++ 為主的目標(biāo)語(yǔ)言,從而被很多不少不了解RTL的工程師所接受。而且,HLS在性能上也近似RTL的水平。

到現(xiàn)在,英特爾,賽靈思,包括多倫多大學(xué)都推出了各自的HLS工具。

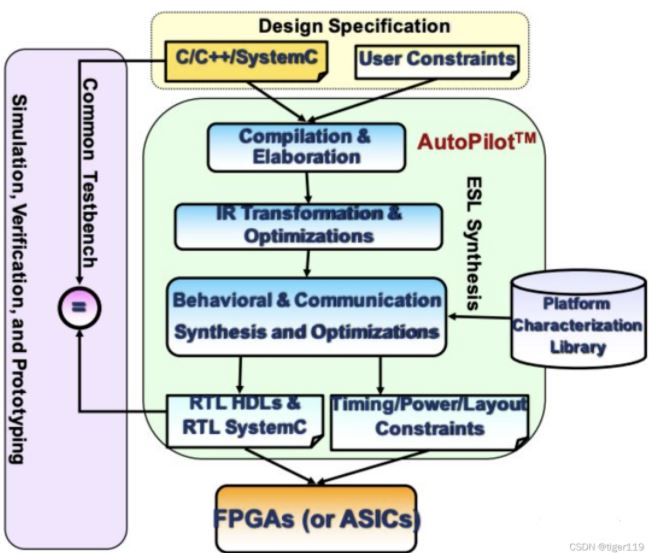

其中比較成功的工具是AutoPilot,

前端,它使用了LLVM的編譯器架構(gòu),能夠使用C,C++,OSCI SystemC等語(yǔ)言,使用llvm-gcc編譯器將高層語(yǔ)言模型轉(zhuǎn)換為IR,優(yōu)化后,再根據(jù)具體的硬件平臺(tái),生成RTL代碼。

AutoPilot在某些領(lǐng)域完勝人工優(yōu)化RTL的結(jié)果。說明了HLS的潛力。

HLS的主流優(yōu)化方法有以下幾種:

1: 字長(zhǎng)分析和優(yōu)化。

FPGA的一個(gè)最主要特點(diǎn)可以使用任意字長(zhǎng),所以 HLS工具也不需要拘泥于某種固定的長(zhǎng)度。好處呢,對(duì)性能提升和面積縮減有幫助。

2: 循環(huán)優(yōu)化

可以使用多面體模型來達(dá)成循環(huán)優(yōu)化,可以幫助實(shí)現(xiàn)性能和面積優(yōu)化,同時(shí)也能幫助提升內(nèi)存的使用效率。

3: 對(duì)并行的支持。

RTL是可以直接實(shí)例化成多個(gè)運(yùn)算單元并行執(zhí)行的,C/C++ 一開始是順序執(zhí)行,但后面也引入的并行支持。如:pthreads和OpenMP等多線程并行編程方法,以及OpenCL等針對(duì)GPU異桅系統(tǒng)進(jìn)行并行編程的擴(kuò)展。

作為HLS工具,一定要支持并行。比如:lgeup就整合了對(duì)pthead,OpenMP的支持。英特爾推出了OpenCL SDK,將其引和HLS,并生成FPGA硬件電路邏輯和CPU代碼兩部分,從而實(shí)現(xiàn)FPGA作為硬件加速模塊的快速開發(fā)。

盡管如此,HLS要完全替代人工的RTL建模,還有很長(zhǎng)的路要走。對(duì)于FPGA而言,內(nèi)存瓶頸是制約性能的關(guān)鍵要素,所以,如何有效利用片上和片外的各類存儲(chǔ)單元,是HLS的研究熱點(diǎn)。

P4 語(yǔ)言是實(shí)現(xiàn)SDN 的重要手段,所以,新型的FPGA開發(fā)工具,需要對(duì)P4進(jìn)行編譯和支持。

三:商業(yè)級(jí)的開發(fā)工具

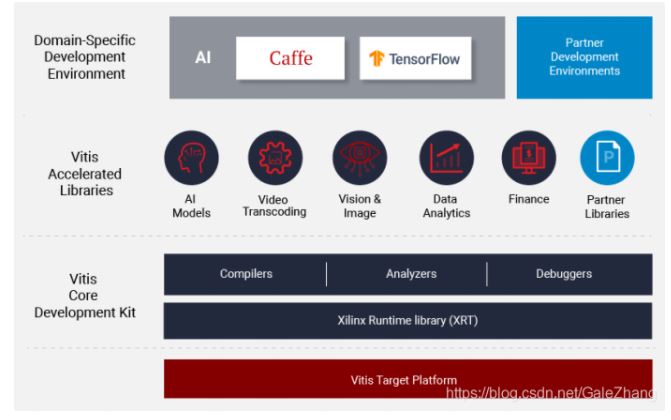

3.1 賽靈思ViTIs 開源開發(fā)工具

ViTIs花費(fèi)了 1000人。年的開發(fā)工作量。

ViTIs的核心架構(gòu)示意圖如下:

3.2 英特爾oneAPI

OneAPI 可以針對(duì)英特爾的所有芯片進(jìn)行編程。

英特爾將旗下的芯片分成了SVMS四類:

標(biāo)量架構(gòu)(Scalar):CPU

矢量架構(gòu)(Vector):GPU

短陣架構(gòu)(Matrix):AI芯片

空間架構(gòu)(Special): FPGA.

四:業(yè)界看法

業(yè)界普遍認(rèn)為,GPU之所以在人工智能獲得成功,很大程度上取決于對(duì)軟件和算法工程師的友好。而FPGA雖然在不斷擴(kuò)展應(yīng)用范圍,在性能和功耗上也不比GPU差,但是,它的編程仍然是以RTL開發(fā)為主,這對(duì)開發(fā)者并不算友好。

所以,F(xiàn)PGA在HLS上的發(fā)展和突破,可能是FPGA能否有更廣泛應(yīng)用的最后一塊拼圖。

更多信息可以來這里獲取==>>電子技術(shù)應(yīng)用-AET<<